- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

4.5. Комбінаційні схеми

Багато застосувань цифрової логіки вимагають наявності схем з декількома входами і декількома виходами, у яких вихідні сигнали визначаються поточними вхідними сигналами. Така схема називається комбінаційною схемою. Не всі схеми мають таку властивість. Наприклад, схема, що містить елементи пам'яті, може генерувати вихідні сигнали, що залежать від значень, які зберігаються в пам'яті. Мікросхема, що реалізує таблицю істинності (наприклад, приведену на рис. 4.3 а, являє типовий приклад комбінаційної схеми. Розглянемо найбільш часто використовувані комбінаційні схеми.

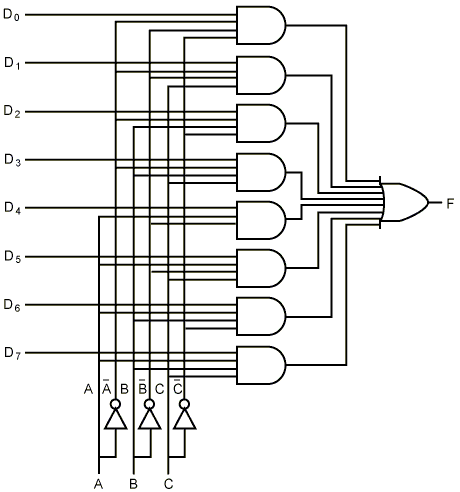

Мультиплексори. На цифровому логічному рівні мультиплексор – це схема з 2n входами, одним виходом і п лініями керування, що вибирають один із входів. Обраний вхід з'єднується з виходом. На рис. 4.10 зображена схема восьмивходового мультиплексора. Три лінії керування А, В і С кодують 3-бітне число, що вказує, яка з восьми ліній входу повинна

Рис. 4.10 - Схема восьмивходового мультиплексора

з'єднуватися з вентилем АБО і, отже, з виходом. Поза залежністю від того, яке значення буде на лініях керування, сім вентилів І будуть завжди видавати на виході 0, а восьмий може видавати або 0, або 1 у залежності від значення обраної лінії входу. Кожен вентиль І запускається визначеною комбінацією ліній керування. Схема мультиплексора показана на рис. 4.10. Якщо до цього додати джерело живлення і «землю», то мультиплексор можна запакувати в корпус з 14 виводами.

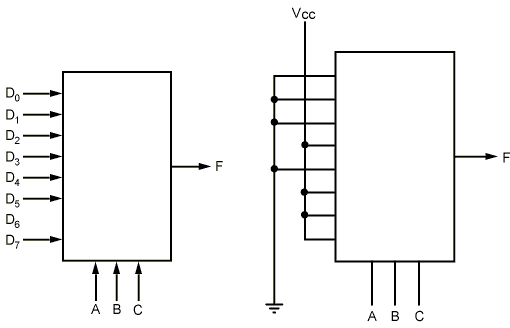

Використовуючи мультиплексор, можна реалізувати функцію більшості (див. рис. 4.3 а), як показано на рис. 4.11 б. Для кожної комбінації А, В і С вибирається одна з вхідних ліній. Кожен вхід з'єднується або з Vcc (логічна 1), або з «землею» (логічний 0). Алгоритм з'єднання входів дуже простий: вхідний сигнал Di такий же, як значення в рядку i у таблиці істинності. На рис. 4.3 а в рядках 0, 1, 2 і 4 значення функції дорівнюють 0, тому відповідні входи заземлюються; у рядках, що залишилися, значення функції дорівнюють 1, тому відповідні входи з'єднуються з логічною 1. Таким чином можна реалізувати будь-яку таблицю істинності з трьома змінними, використовуючи мікросхему на рис. 4.11 а.

Отже, мультиплексор може використовуватися для вибору одного з декількох входів і може реалізувати таблицю істинності. Його також можна використовувати як перетворювач паралельного коду в послідовний. Якщо подати 8 бітів даних на лінії входу, а потім переключати лінії керування послідовно від 000 до 111 (двійкові числа), 8 бітів надійдуть на лінію виходу послідовно. Звичайно таке перетворення здійснюється при введенні інформації з клавіатури, оскільки кожне натискання клавіші визначає 7- або 8-бітне число, яке повинне передаватися послідовно по телефонній лінії.

Протилежністю мультиплексора є демультиплексор, що з'єднує єдиний вхідний сигнал з одним з 2n виходів у залежності від значень п ліній керування. Якщо бінарне значення ліній керування дорівнює k, то вибирається вихід k.

Декодери. Як другий приклад розглянемо схему, що одержує на вході п-бітне число і використовує його для того, щоб вибрати (тобто встановити на значення 1) одну з 2n вихідних ліній. Така схема називається декодером. Приклад декодера для п=3 показаний на рис. 4.12.

а) б)

Рис. 4.11 - Мультиплексор, побудований на СІС (а); той же мультиплексор, змонтований для обчислення функції більшості (б)

Щоб зрозуміти, навіщо потрібний декодер, представимо пам'ять, що складається з 8 мікросхем, кожна з яких містить 1 Мбайт. Мікросхема 0 має адреси від 0 до 1 Мбайт, мікросхема 1 – адреси від 1 Мбайт до 2 Мбайт і т.д. Три старших двійкових розряди адреси використовуються для вибору однієї з восьми мікросхем. На рис.4.12 ці три біти – три входи А, В і С. В залежності від вхідних сигналів рівно одна з восьми вихідних ліній (D0,..., D7) приймає значення 1; інші лінії приймають значення 0. Кожна вихідна лінія запускає одну з восьми мікросхем пам'яті. Оскільки тільки одна лінія приймає значення 1, запускається тільки одна мікросхема.

Принцип

роботи схеми, зображеної

на рис. 4.12 не складний.

Кожен

вентиль

І має три

входи, з яких перший

або

А, або

,

другий

або

В, або

,

а

третій

або

С,

або

![]() .

Кожен

вентиль запускається різною комбінацією

входів:

D0

– сполученням

,

,

,

Di

–

,

,

С

і т. д.

.

Кожен

вентиль запускається різною комбінацією

входів:

D0

– сполученням

,

,

,

Di

–

,

,

С

і т. д.

Компаратори. Ще одна схема – компаратор. Компа-ратор порівнює два слова, що надходять на вхід. Компаратор, зображений на рис.4.13 приймає два вхідних сигнали, А і В, кожен довжиною 4 біти, і видає 1, якщо вони рівні, і 0, якщо

Рис. 4.12 - Схема декодера, що містить