- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

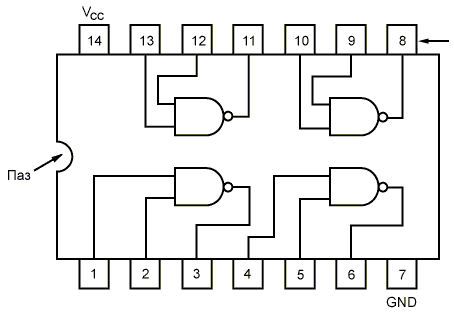

Основні цифрові логічні схеми Інтегральні схеми

Вентилі виробляються і продаються не по окремості, а в модулях, що називаються інтегральними схемами (ІС) або мікросхемами. Інтегральна схема – це квадратний шматочок кремнію розміром приблизно 5x5 мм, на якому знаходиться кілька вентилів. Маленькі інтегральні схеми звичайно містяться в прямокутні пластикові або керамічні корпуси розміром від 5 до 15 мм у ширину і від 20 до 50 мм у довжину. Уздовж довгих боків розташовується два паралельних ряди виводів близько 5 мм у довжину, які можна вставляти в роз’єми або впаювати в друковану плату. Кожен вивід з'єднується з входом або виходом деякого вентиля, або з джерелом живлення, або з «землею». Корпус із двома рядами виводів зовні й інтегральними схемами усередині офіційно називається дворядним корпусом (Dual Inline Package, скорочено DIP), але всі називають його мікросхемою, стираючи розходження між шматком кремнію і корпусом, у який він міститься. Більшість корпусів мають 14, 16, 18, 20, 22, 24, 28,40, 64 або 68 виводів. Для великих мікросхем часто використовуються корпуси, у яких виводи розташовані з усіх чотирьох боків або знизу.

Мікросхеми можна розділити на кілька класів з погляду кількість вентилів, що вони містять. Ця класифікація, звичайно, дуже груба, але іноді вона може бути корисна:

- МІС (мала інтегральна схема): від 1 до 10 вентилів.

- СІС (середня інтегральна схема): від 1 до 100 вентилів.

- БІС (велика інтегральна схема): від 100 до 100 000 вентилів.

- НБІС (надвелика інтегральна схема): більше 100 000 вентилів.

Ці схеми мають різні властивості і використовуються для різних цілей.

МІС звичайно містить від двох до шести незалежних вентилів, кожний з яких може використовуватися окремо. На рис. 4.9 зображена звичайна мікросхема МІС, що містить чотири вентилі НЕ-І. Кожний з цих вентилів має два входи й один вихід, що вимагає наявності 12 виводів. Крім того, мікросхемі потрібне живлення (Vcc) і «земля» (GND). Вони розділяються усіма вентилями. На корпусі поруч з виводом 1, як правило, є паз, щоб можна було визначити, що це вивід 1. Щоб уникнути плутанини на діаграмі, за згодою не показуються невикористані вентилі, джерело живлення і «земля».

Подібні мікросхеми коштують кілька центів. Кожна мікросхема МІС містить кілька вентилів і приблизно до 20 виводів. У 70-і роки комп'ютери конструювалися з великої кількості таких мікросхем, але в даний час на одну мікросхему містять цілий центральний процесор і істотну частину пам'яті (кеш-пам'яті).

Рис. 4.9 - Мікросхема МІС, що містить 4 вентилі

Для зручності приймається, що у вентиля з'являються зміни на виході, як тільки з'являються зміни на вході. Насправді існує визначена затримка вентиля, яка складається з часу проходження сигналу через мікросхему і час перемикання. Час затримки звичайно складає від 1 до 10 нс.

В даний час стало можливим розміщувати до 100 млн транзисторів на одну мікросхему (ядро процесора Реntium IV містить 42 млн транзисторів). Внаслідок того, що будь-яка схема може бути сконструйована з вентилів НЕ-І, може створитися враження, що виробник здатний виготовити мікросхему, що містить 5 млн вентилів НЕ-І. Але для створення такої мікросхеми буде потрібно 15 000 002 виводів. Оскільки стандартний вивід займає 0,1 дюйм, мікросхема буде більше 18 км у довжину, що негативно позначиться на купівельній спроможності. Тому щоб використовувати переваги даної технології, потрібно розробити такі схеми, у яких кількість вентилів сильно перевищує кількість виводів.