- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

4.4. Еквівалентність схем

Розробники схем часто намагаються скоротити число вентилів, щоб знизити ціну, зменшити площу схеми, скоротити споживання енергії і т.д. Щоб спростити схему, розробник повинний знайти іншу схему, що може обчислювати ту ж функцію, але при цьому вимагає меншої кількості вентилів (або може працювати з більш простими вентилями, наприклад двовходовими замість чотиривходових). Булева алгебра є інструментом у пошуку еквівалентних схем.

Як приклад використання булевої алгебри розглянемо схему і таблицю істинності для АВ+АС (рис. 4.5 а). Багато правил звичайної алгебри мають силу для булевої алгебри. Наприклад, вираз АВ+АС може бути перетворений в А(В+С) за допомогою дистрибутивного закону. На рис. 4.5 б показана схема і таблиця істинності для А(В+С). Дві функції є еквівалентними тоді і тільки тоді, коли обидві функції приймають те саме значення для всіх можливих змінних. З таблиць істинності на рис. 4.5 видно, що А(В+С) еквівалентно АВ+АС. Незважаючи на цю еквівалентність, схема на рис. 4.5 б краща, ніж схема на рис. 4.5 а, оскільки вона містить менше вентилів.

Як правило, розробник виходить з визначеної булевої функції, а потім застосовує до неї закони булевої алгебри, щоб знайти більш просту функцію, еквівалентну вихідній. На основі отриманої функції можна конструювати схему.

Щоб

використовувати даний підхід, потрібні

деякі рівності з булевої

алгебри.

У табл. 1 показані деякі основні закони.

Треба відзначити, що кожний

закон має дві

форми.

Одну форму з іншої можна одержати,

змінюючи І на АБО

і 0 на 1.

Усі

закони можна легко довести, склавши

їхні

таблиці істинності.

Майже у всіх випадках результати

очевидні, за винятком законів де

Моргана,

законів поглинання і дистрибутивного

закону А+ВС=(А+В)(А+С). Закони де

Моргана

поширюються

на вирази

з

більше ніж двома змінними, наприклад

![]() .

.

A |

В |

С |

АВ |

АС |

АВ+АС |

|

А |

В |

С |

А |

В+С |

А(В+С) |

А |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

а) б)

Рис. 4.5. Дві еквівалентні функції: АВ+АС (а); А(В+С) (б).

Таблиця 5.1 - Деякі закони булевої алгебри

Назви законів |

І |

АБО |

Закони тотожності |

1А=А |

0+А=А |

Закони нуля |

ОА=0 |

1+А=1 |

Закони ідемпотентності |

АА=А |

А+А=А |

Закони інверсії |

А |

А+ =1 |

Комунікативні закони |

АВ=ВА |

А+В=В+А |

Асоціативні закони |

(АВ)С=А(ВС) |

(А+В)+С= А+(В+З) |

Дистрибутивні закони |

А+ВС= (А+В)(А+С) |

А(В+С)=АВ+АС |

Закони поглинання |

А(А+В)=А |

А+АВ=А |

1 |

2 |

3 |

Закони Де Моргана |

|

|

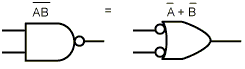

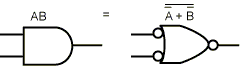

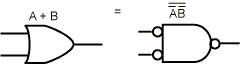

Закони Де Моргана припускають альтернативний запис. На рис. 4.6 а форма І дається із запереченням, що показується за допомогою інвертуючи входів і виходів. Таким чином, вентиль АБО з інвертованими вхідними сигналами еквівалентний вентилеві НЕ-І. З рис. 4.6 б, на якому зображена друга форма закону Де Моргана, ясно, що замість вентиля НЕ-АБО можна намалювати вентиль І з інвертованими входами. За допомогою заперечення обох форм закону Де Моргана приходимо до еквівалентних репрезентацій вентилів І і АБО (див. рис. 4.6 в і 4.6, г). Аналогічні символічні зображення існують для різних форм закону Де Моргана (наприклад, n-вхідний вентиль НЕ-І стає вентилем АБО з інвертованими входами).

а) б)

в) г)

Рис. 4.6 - Альтернативні позначення деяких вентилів: НЕ-І (а); НЕ-АБО (б); І (в); АБО (г)

Використовуючи рівняння, зазначені на рис. 4.6 і аналогічні рівняння для багатовхідних вентилів, можна легко перетворити суму добутків у чисту форму НЕ-І або чисту форму НЕ-АБО.

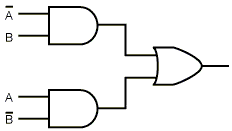

Як

приклад розглянемо

функцію

ВИКЛЮЧНЕ

АБО

(рис. 4.7 а).

Стандартна

схема,

що

виражає

суму добутків,

показана на рис. 4.7 б.

Щоб

перейти до форми НЕ-І, потрібно

лінії,

що

з'єднують виходи вентилів І з входом

вентиля АБО,

намалювати з

інвертуючими входами і

виходами,

як показано на

рис. 4.7

в.

Потім,

застосовуючи

рис. 4.6 а,

приходимо до рис. 4.7 г.

Змінні

і

![]() можна одержати

з

А і В, використовуючи вентилі НЕ-І або

НЕ-АБО з

об'єднаними входами. Відзначимо,

що інвертуючі входи

(виходи)

можуть переміщатися уздовж лінії за

бажанням,

наприклад,

від виходів вхідних вентилів до входів

вихідного

вентиля.

можна одержати

з

А і В, використовуючи вентилі НЕ-І або

НЕ-АБО з

об'єднаними входами. Відзначимо,

що інвертуючі входи

(виходи)

можуть переміщатися уздовж лінії за

бажанням,

наприклад,

від виходів вхідних вентилів до входів

вихідного

вентиля.

А |

У |

XOR |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

а) б)

в) г)

Рис. 4.7 - Таблиця істинності для функції ВИКЛЮЧнЕ АБО (а); три схеми для обчислення цієї функції (б-г)

Дуже важливо відзначити, що той самий вентиль може обчислювати різні функції в залежності від використовуваних угод. На рис. 8 а показано вихід певного вентиля, F, для різних комбінацій вхідних сигналів. І вхідні, і вихідні сигнали показані у вольтах. Якщо прийняти угоду, що 0 В – це логічний нуль, а 3,3 В або 5 В – логічна одиниця, одержимо таблицю істинності, показану на рис. 4.8 б, тобто функцію І. Така угода називається позитивною логікою. Однак якщо прийняти негативну логіку, тобто прийняти, що 0 В – це логічна одиниця, а 3,3 В або 5 В – логічний нуль, то одержимо таблицю істинності, показану на рис. 4.8 в, тобто функцію АБО.

Таким чином, все залежить від того, яка угода обрана для відображення вольтів у логічних величинах.

A

В

F

1

1

1

1

0

1

0

1

1

0

0

0

А

В

F

0v

0v

0v

0v

5v

0v

5v

0v

0v

5v

5v

5v

A

В

F

0

0

0

0

1

0

1

0

0

1

1

1

а) б) в)

Рис.5.8 - Електричні характеристики пристрою (а); позитивна логіка (б); негативна логіка (в)