- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

4.3. Реалізація булевих функцій

Отже, представлення булевої функції у вигляді суми максимум 2п добутків уможливлює реалізацію цієї функції. На рис. 4.3 можна побачити, як це здійснюється. На рис. 4.3 б вхідні сигнали А, В і С показані з лівої сторони, а функція М, отримана на виході, показана з правої сторони. Оскільки необхідні додаткові величини (інверсії) вхідних змінних, вони утворюються шляхом проходження сигналу через інвертори 1,2 і 3. З 6 вертикальних ліній 3 пов'язані з вхідними змінними, а 3 інші – з їх інверсіями. Ці лінії забезпечують передачу вхідного сигналу до вентилів. Наприклад, вентилі 5, 6 і 7 як вхід використовують А. У реальній схемі ці вентилі, імовірно, будуть безпосередньо з'єднані проводом з А без яких-небудь проміжних вертикальних проводів.

Схема містить чотири вентилі І, по одному для кожного члена в рівнянні для М (тобто по одному для кожного рядка в таблиці істинності з результатом 1). Кожен вентиль І обчислює один із зазначених рядків таблиці істинності. Зрештою всі дані добутки сумуються (мається на увазі операція АБО) для одержання кінцевого результату.

Якщо дві лінії на малюнку перетинаються, зв'язок є в тому випадку, якщо на перетинанні зазначена жирна крапка. Наприклад, вихід вентиля 3 перетинає всі 6 вертикальних ліній, але пов'язаний він тільки із С.

Реалізувати схему для будь-який булевої функції можна за такі етапи:

Скласти таблицю істинності для даної функції.

Забезпечити інвертори, щоб потворити інвер-сії для кожного вхідного сигналу.

Намалювати вентиль І для кожного рядка табли-ці істинності з результатом 1.

З'єднати вентилі І з відповідними вхідними сигналами.

Вивести виходи усіх вентилів І у в вентиль АБО.

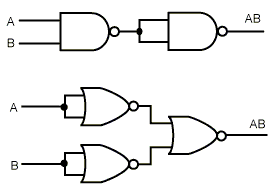

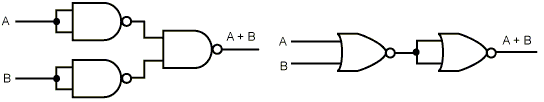

У даному прикладі показано, як реалізувати будь-яку булеву функцію з використанням вентилів НЕ, І і АБО. Однак набагато зручніше будувати схеми з використанням одного типу вентилів. Схеми, побудовані по попередньому алгоритмі, можна легко перетворити у форму НЕ-І або НЕ-АБО. Щоб здійснити таке перетворення, усе, що потрібно – це спосіб реалізації НЕ, І і АБО за допомогою одного типу вентилів. На рис. 4.4 показано, як це можна зробити, використовуючи тільки вентилі НЕ-І або тільки вентилі НЕ-АБО. Відзначимо, що існують також інші способи подібного перетворення.

а) б)

в)

Рис. 4.4 - Конструювання вентилів НЕ (а), І (б) і АБО (в) з використанням тільки вентилів НЕ-І або тільки вентилів НЕ-АБО

Для того щоб реалізувати булеву функцію з використанням тільки вентилів НЕ-І або тільки вентилів НЕ-АБО, можна спочатку додержуватися алгоритму, описаному вище, і сконструювати схему з вентилями НЕ і І і АБО. Потім потрібно замінити багатовхідні вентилі еквівалентними схемами з використанням двоходових вентилів. Наприклад, A+B+C+D можна поміняти на (A+B)+(C+D), використовуючи три двовходові вентилі. Потім вентилі НЕ і І і АБО заміняються схемами, зображеними на рис. 4.4.

Хоча така процедура і не приводить до оптимальних схем з погляду мінімального числа вентилів, вона демонструє, що подібне перетворення здійсненне. Вентилі НЕ-І і НЕ-АБО вважаються повними, тому що можна обчислити будь-яку булеву функцію, використовуючи тільки вентилі НЕ-І або тільки вентилі НЕ-АБО. Інші вентилі не мають такої властивості, от чому саме ці два типи вентилів кращі при побудові схем.