- •Мови, рівні і віртуальні машини

- •Сучасні багаторівневі машини

- •Поняття архітектури пк

- •1.4. Розвиток комп’ютерної архітектури

- •Розвиток багаторівневих машин

- •Типи сучасних еом

- •Питання до лекції

- •2.1. Принципи розробки сучасних комп'ютерів

- •2.2. Паралелізм на рівні команд

- •2.3. Конвеєри

- •2.4. Суперскалярні архітектури

- •2.5. Паралелізм на рівні процесорів

- •2.6. Векторні комп'ютери

- •Блок управління

- •2.7. Мультипроцессори

- •2.8. Мультикомпьютери

- •Питання до лекції

- •3. Основи комп’ютерної організації : пам’ять

- •3.1. Ієрархічна структура пам'яті

- •3.2. Загальні відомості про пам'ять

- •3.4. Методи звертання до пам'яті

- •3.5. Модулі пам'яті

- •3.6. Ряди і банки пам'яті

- •3.8. Код з виправленням помилок

- •3. 9. Скільки потрібно пам'яті

- •Питання до лекції

- •4. Цифровий рівень побудови ом

- •4.1. Вентилі і булева алгебра

- •4.2. Булева алгебра

- •4.3. Реалізація булевих функцій

- •4.4. Еквівалентність схем

- •Основні цифрові логічні схеми Інтегральні схеми

- •4.5. Комбінаційні схеми

- •3 Входи і 8 виходів

- •4.6. Арифметичні схеми.

- •4.7. Тактові генератори

- •Питання до лекції

- •Цифровий рівень побудови ом.

- •5. Цифровий логічний рівень архітектури: пам’ять, мікропроцесори

- •5.2. Синхронні sr-защіпки

- •5.3. Синхронні d-защіпки

- •5.4. Тригери (flip-flops)

- •5.5. Регістри

- •5.6. Організація пам'яті

- •Тригер (б)

- •Кожний ряд представляє одне з 3-бітних слів. При операції зчитування і запису завжди зчитується або записується ціле слово

- •5.7. Мікросхеми пам'яті

- •5.9. Мікросхеми процесорів

- •Стрілочки указують вхідні і вихідні сигнали. Короткі діагональні лінії вказують на наявність декількох висновків.

- •Питання до лекції

- •6. Шини

- •6.1. Ширина шини

- •6.2. Синхронізація шини

- •6.3. Синхронні шини

- •6.5. Асинхронні шини

- •6.6. Арбітраж шини

- •6.7. Принципи роботи шини

- •Питання до лекції

- •7. Мікроархітектурний рівень

- •7.1. Приклад мікроархітектури

- •7.2. Тракт даних

- •В цьому розділі

- •Табліця 7.1. Деякі комбінації сигналів аллу і відповідні їм функції

- •7.3. Синхронізація тракту даних

- •7.4. Робота пам'яті.

- •7.5. Мікрокоманди

- •7.6. Управління мікрокомандами: Mic-1

- •7.7. Приклад архітектури команд: ijvm

- •7.8. Модель пам'яті ijvm

- •Питання до лекції

- •8. Рівень архітектури команд

- •8.1. Моделі пам'яті

- •8.2. Загальний огляд рівня архітектури команд

- •8.3. Властивості рівня команд

- •8.4. Регістри

- •8.5. Команди

- •8.6. Загальний огляд рівня команд машини Pentium II

- •8.8. Загальний огляд рівня команд системи ultrasparc II

- •8.9. Загальний огляд віртуальної машини Java

- •8.10. Типи даних

- •8.11. Числові типи даних

- •8.12. Нечислові типи даних

- •8.13. Типи даних процесора Pentium II

- •Підтримувані типи відмічені хрестом (х)

- •8.14. Типи даних машини UltraSparc II

- •8.16. Типи даних віртуальної машини Java

- •8.17. Формати команд

- •Питання до лекції

- •9. Адресація

- •9.1. Способи адресації

- •9.2. Безпосередня адресація

- •9.3. Пряма адресація

- •9.4. Регістрова адресація

- •9.5. Непряма регістрова адресація

- •Лістинг 9.1 - Програма на асемблері для обрахунку суми елементів масиву.

- •9.6. Індексна адресація

- •Листинг 9.2. Програма на мові асемблера для обчислення операції або від (Аі і Ві ) для масиву з 1024 елементів.

- •9.7. Відносна індексна адресація

- •9.8. Стекова адресація

- •9.9. Зворотній польський запис

- •9.10. Обчислення формул в зворотнім польськім записі

- •Питання до лекції

Питання до лекції

Побудуйте ієрархічну структуру пам’яті у вигляді піраміди!

Дайте визначення оперативної пам’яті, або пам’ять з вільним доступом! Які є види оперативної пам’яті?

Які існують рівні кеш-пам’яті?

Розкажіть окремо про всі рівні кеш-пам’яті!

Яка проблема виникаю при взаємодії процесора з пам’яттю?

Які є два шляхи рішення цієї проблеми?

Що називається кеш-пам’яттю?

В чому полягає ідея принципу локальності?

Намалюйте загальну схему взаємодії між процесором і кеш-пам’яттю!

В чому полягає різниця між суміжною і розділеною кеш-пам’яттю?

Розкажіть про асинхронну пам’ять і її типи!

Розкажіть про протокольні типи DRAM !

Які є види модулів пам’яті?

Коротко розкажіть про ряди і банки пам’яті!

Які бувають ємності чіпів?

Що це таке „кодоване слово” та „інтервал Хеммінга” ?

Як можна визначити скільки потрібно пам’яті для ЕОМ?

4. Цифровий рівень побудови ом

В основі ієрархічної схеми архітектури обчислювальних машин знаходиться цифровий логічний рівень, або апаратне забезпечення комп'ютера. Всі наступні, більш вищі рівні архітектури неможливо вивчити без знання різних аспектів цифрової логіки. Предмет вивчення знаходиться на межі інформатики та електротехніки, але матеріал є самодостатнім, тому попереднього ознайомлення з апаратним забезпеченням і електротехнікою не потрібно.

Основні елементи, з яких конструюються цифрові комп'ютери, надзвичайно прості. Спочатку розглянемо основні елементи, а також спеціальну двозначну алгебру (булеву алгебру), що використовується при конструюванні цих елементів. Потім розглянемо основні схеми, які можна побудувати з вентилів у різних комбінаціях, у тому числі схеми для виконання арифметичних дій. За допомогою комбінації вентилів можна зберігати інформацію, тобто побудувати пам'ять, процесори, шини.

4.1. Вентилі і булева алгебра

Цифрові схеми можуть конструюватися з невеликої кількості простих елементів шляхом сполучення цих елементів у різних комбінаціях. Цифрова схема – це схема, в якій є тільки два логічних значення. Як правило, сигнал від 0 до 1 В представляє одне значення (наприклад, 0), а сигнал від 2 до 5 В – інше значення (наприклад, 1). Напруга за межами зазначених величин неприпустима. Маленькі електронні пристрої, що називаються вентилями, можуть обчислювати різні функції від цих двозначних сигналів. Ці вентилі формують основу апаратного забезпечення, на якій будуються всі цифрові комп'ютери.

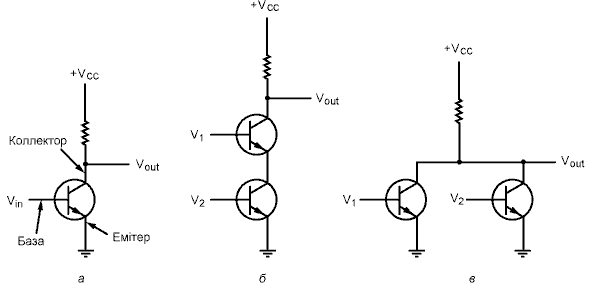

Опис принципів роботи вентилів відноситься до рівня фізичних пристроїв. Розглянемо основний принцип їх роботи. Вся сучасна цифрова логіка ґрунтується на тому, що транзистор може працювати як дуже швидкий бінарний перемикач. На рис. 4,1 а зображено біполярний транзистор, вбудований у просту схему. Транзистор має три з'єднання з зовнішнім світом: колектор, базу і емітер. Якщо вхідна напруга Vіn нижча визначеного критичного значення, транзистор виключається і діє як дуже великий опір. Це приводить до того, що вихідний сигнал Vout стає близьким до Vcc (напруги, що подається ззовні), як правило +5 В для даного типу транзистора. Якщо Vіn перевищує критичне значення, транзистор включаться і діє як провід, викликаючи заземлення сигналу Vоut (0 В).

Важливо відзначити, що якщо напруга Vіn низька, то Vout висока, і навпаки. Ця схема, таким чином, є інвертором, що перетворює логічний 0 у логічну 1, і логічну 1 у логічний 0. Резистор (ламана лінія) потрібний для обмеження кількості струму, що проходить через транзистор, щоб транзистор не згорів. На перемикання з одного стану на інший звичайно потрібно декілька наносекунд.

На рис. 4.1 б два транзистори з'єднані послідовно. Якщо і напруга V1, і напруга V2 високі, то обидва транзистора будуть служити провідниками і знижувати Vout. Якщо одна з вхідних напруг низька, то відповідний транзистор буде виключатися і напруга на виході буде високою. Іншими словами, Vout буде низькою тоді і тільки тоді, коли і напруга V1 і напруга V2 висока.

На рис. 4.1 в обидва транзистори з'єднані паралельно. Якщо один із вхідних сигналів високий, буде включатися відповідний транзистор і знижувати вихідний сигнал. Якщо обидві напруги на вході низькі, то вихідна напруга буде високою.

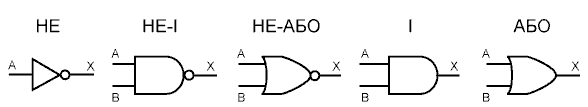

Ці три схеми утворюють три найпростіших вентилі. Вони називаються вентилями НЕ, НЕ-І і НЕ-АБО. Вентилі НЕ часто називають інверторами. Якщо прийняти, що висока напруга (Vсс – це логічна 1. а низька напруга (“земля”) – логічний 0, то можна значення на виході можна виразити як функцію від вхідних значень Значки, що використовуються для зображення цих трьох типів вентилів, показані на рис. 4.2 а - в. Там же наводиться значення функції для кожної схеми На малюнках А і В – це вхідні сигнали, а X – вихідний сигнал. Кожен рядок таблиці визначає вихідний сигнал для різних комбінацій вхідних сигналів.

А |

у |

X |

0 |

0 1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

JJ |

1 |

0 |

А |

у |

X |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Рис. 4.1 - Транзисторний інвертор (а), вентиль НЕ-І (б), вентиль НЕ-АБО (в)

а) б) в) г) д)

|

А |

А

В

Х

0

0

1

0

1

0

1

0

0

1

1

0

А

В

Х

0

0

0

0

1

1

1

0

1

1

1

1

|

|

||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

0 |

1 |

|

||||||||||||||||||||||||||||||||||

|

1 |

0 |

|

||||||||||||||||||||||||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||

А |

В |

Х |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Рис. 4.2 - Значки для зображення 5 основних вентилів. Значення функції для кожного вентиля

Якщо вихідний сигнал (рис. 4.1 б) подати в інвертор, одержимо іншу схему, протилежну вентилю НЕ-І, тобто таку схему, в якій вихідний сигнал 1 дорівнює 1 тоді і тільки тоді, коли обидва вхідних сигналів рівні 1. Така схема називається вентилем І, її схематичне зображення й опис відповідної функції подані на рис. 4.2 а. Точно так само вентиль НЕ-АБО може бути пов'язаний з інвертором. Тоді отримується схема, у якої вихідний сигнал дорівнює 1 в тому випадку, якщо хоча б один з вхідних сигналів - 1, і дорівнює 0, якщо обидва вхідних сигналів рівні 0. Зображення цієї схеми, яка називається вентилем АБО, а також опис відповідної функції подано на рис. 4.2 д. Маленькі кружечки в схемах інвертора, вентиля НЕ-І і вентиля НЕ-АБО називаються інвертуючими виходами.

П’ять вентилів, зображених на рис. 4.2, складають основу цифрового логічного рівня. Вентилі НЕ-І, НЕ-АБО потребують два транзистори кожний, а вентилі І і АБО – три транзистори кожний. Внаслідок цього в більшості комп’ютерів використовуються вентилі НЕ-І і НЕ-АБО, а не І і АБО. (На практиці усі вентилі виконуються трохи інакше, але НЕ-І і НЕ-АБО все одно простіші, ніж І і АБО.) Варто згадати, що вентилі можуть мати більш двох входів. У принципі вентиль НЕ-І, наприклад, може мати довільну кількість входів, але на практиці більше восьми, як правило, не буває.

Основні серії виробничих технологій. Дві основні технології – біполярна і МОН (метал-оксид-напівпровідник). Серед біполярних технологій можна назвати ТТЛ (транзисторно-транзисторну логіку), що була основою цифрової електроніки протягом багатьох років, і ЕЗЛ (емітерно-зв’язану логіку), що використовується в тих випадках, коли потрібна висока швидкість виконання операцій.

Вентилі МОН працюють повільніше, ніж ТТЛ і ЕЗЛ, але споживають набагато менше енергії і займають набагато менше місця, тому можна компактно розташувати велику кількість таких вентилів. Вентилі МОН мають кілька різновидів: р-канальний МОН-прилад, n-канальний МОН-прилад і комплементарний МОН. Хоча МОН-транзистори конструюються не так, як біполярні транзистори, вони мають таку ж здатність функціонувати, як електронні перемикачі. Сучасні процесори і пам'ять найчастіше розробляються з використанням технології комплементарних МОН, що працює при напрузі +3,3 В.