- •Операционная система

- •Функции

- •Понятие

- •Эволюция и основные идеи

- •[Править] Пакетный режим

- •[Править] Разделение времени и многозадачность

- •Разделение полномочий

- •Реальный масштаб времени

- •Существующие операционные системы unix, стандартизация операционных систем и posix

- •Пост-unix-архитектуры

- •III) Система шина pci: назначение, структура и характеристики.

III) Система шина pci: назначение, структура и характеристики.

Определение.

Интерфейс

– стандартный набор линий связи и

стандартных протоколов обмена информацией

по этим линиям.

Ш ина

PCI.

Наличие

специальных контроллеров (мостов),

обеспечивающих частично обмен информацией,

а так же служащих для подключения других

с-ных шин и уст-в к данной магистрали.

Шина 32 разрядная, адреса 32 разрядные,

тактовая частота 33 МГц, возможна работа

с частотой 66 МГц. Скорость передачи

данных 132 Мбайт/сек и 264 Мбайт/сек. Шина

синхронная. Обмен данными пакетными

режимами. После подачи кода адреса,

формируется нес-ко пакетов данных.

Арбитраж запросов на прерывания

централизованный. Каждое уст-во имеет

собственную линию запроса на прерывание

и линию подтверждения прерывания.

Предусмотрено три способа завершения

транзакций (обмен данными).

1. По

завершению обмена данными.

2. По

тайм-ауту (завершению интервала времени,

отведённого на обмен данными).

3.

При отсутствии отклика от одного из

уст-в участвующих в обмене.

Шина

PCI имеет два варианта: 32-разрядный (в нем

используется 124-контактный разъем) и

64-разрядный (188-контактный разъем). При

этом гарантируется как прямая, так и

обратная совместимость 32- и 64-разрядных

устройств. Чаще всего применяется

32-разрядный вариант PCI.

Тактовая

частота PCI составляет 33 МГц (однако

допускается и частота 66 МГц). Максимальная

теоретически возможная скорость обмена

при тактовой частоте 33 МГц достигает

132 или 264 Мбайт/с для 32 и 64 разрядов данных.

Предусмотрена возможность включения

плат с напряжением питания как 5 В, так

и 3,3 В (в раздельные разъемы). На магистрали

предусмотрен арбитраж, то есть возможность

поочередного захвата шины несколькими

задатчиками, с разрешением конфликтов

между ними. Предусмотрен высокоскоростной

обмен по магистрали без участия

процессора. Возможна автоконфигурация,

то есть автоматическое распределение

ресурсов между включенными платами (по

принципу PnP). Каждое из устройств шины

может захватить ее и провести необходимый

обмен.

Недостаток шины является

ограниченное количество устройств на

шине (не более четырех), для большего

количества устройств необходимо

применение мостов PCI—PCI.

Шина

PCI относится к мультиплексированным

шинам, она имеет полностью мультиплексированную

шину адреса/данных. При этом адрес может

быть 32 разрядным или 64-разрядным (он

передается по 32-разрядной шине за два

такта, сначала младшие разряды, затем

старшие) Точно так же и данные могут

передаваться как 32-разрядные, так и

64-разрядные (за два такта при 32-разрядной

шине). В 64-разрядной версии PCI шина

адреса/данных имеет 64 разряда.

Основной режим обмена по шине —

синхронный, тактируемый положительными

фронтами тактового сигнала шины, но

возможен и асинхронный обмен (как и в

случае ISA). В цикл обмена (или транзакцию)

входит фаза адреса (в начале) длительностью

один такт и фаза данных длительностью

в один или несколько тактов.

ина

PCI.

Наличие

специальных контроллеров (мостов),

обеспечивающих частично обмен информацией,

а так же служащих для подключения других

с-ных шин и уст-в к данной магистрали.

Шина 32 разрядная, адреса 32 разрядные,

тактовая частота 33 МГц, возможна работа

с частотой 66 МГц. Скорость передачи

данных 132 Мбайт/сек и 264 Мбайт/сек. Шина

синхронная. Обмен данными пакетными

режимами. После подачи кода адреса,

формируется нес-ко пакетов данных.

Арбитраж запросов на прерывания

централизованный. Каждое уст-во имеет

собственную линию запроса на прерывание

и линию подтверждения прерывания.

Предусмотрено три способа завершения

транзакций (обмен данными).

1. По

завершению обмена данными.

2. По

тайм-ауту (завершению интервала времени,

отведённого на обмен данными).

3.

При отсутствии отклика от одного из

уст-в участвующих в обмене.

Шина

PCI имеет два варианта: 32-разрядный (в нем

используется 124-контактный разъем) и

64-разрядный (188-контактный разъем). При

этом гарантируется как прямая, так и

обратная совместимость 32- и 64-разрядных

устройств. Чаще всего применяется

32-разрядный вариант PCI.

Тактовая

частота PCI составляет 33 МГц (однако

допускается и частота 66 МГц). Максимальная

теоретически возможная скорость обмена

при тактовой частоте 33 МГц достигает

132 или 264 Мбайт/с для 32 и 64 разрядов данных.

Предусмотрена возможность включения

плат с напряжением питания как 5 В, так

и 3,3 В (в раздельные разъемы). На магистрали

предусмотрен арбитраж, то есть возможность

поочередного захвата шины несколькими

задатчиками, с разрешением конфликтов

между ними. Предусмотрен высокоскоростной

обмен по магистрали без участия

процессора. Возможна автоконфигурация,

то есть автоматическое распределение

ресурсов между включенными платами (по

принципу PnP). Каждое из устройств шины

может захватить ее и провести необходимый

обмен.

Недостаток шины является

ограниченное количество устройств на

шине (не более четырех), для большего

количества устройств необходимо

применение мостов PCI—PCI.

Шина

PCI относится к мультиплексированным

шинам, она имеет полностью мультиплексированную

шину адреса/данных. При этом адрес может

быть 32 разрядным или 64-разрядным (он

передается по 32-разрядной шине за два

такта, сначала младшие разряды, затем

старшие) Точно так же и данные могут

передаваться как 32-разрядные, так и

64-разрядные (за два такта при 32-разрядной

шине). В 64-разрядной версии PCI шина

адреса/данных имеет 64 разряда.

Основной режим обмена по шине —

синхронный, тактируемый положительными

фронтами тактового сигнала шины, но

возможен и асинхронный обмен (как и в

случае ISA). В цикл обмена (или транзакцию)

входит фаза адреса (в начале) длительностью

один такт и фаза данных длительностью

в один или несколько тактов.

Основные сигналы шины PCI следующие: AD0…AD31 — шина адреса/данных. Адрес передается в начале цикла, затем — данные; -C/BE0…-C/BE3 (Command/Byte Enable) — четыре линии, которые в фазе адреса определяют один из 16 возможных типов цикла передачи данных (табл. 8.9), а в фазе данных определяют действительность байтов данных; -FRAME — строб адреса, активен во время передачи данных; -IRDY (Initiator Ready) — готовность задатчика (инициатора обмена) к обмену данными; -TRDY (Target Ready) — готовность исполнителя (целевого устройства) к обмену данными; -DEVSEL (Device Select) — подтверждение опознания адреса от исполнителя; -STOP — запрос на останов текущего цикла от исполнителя к задатчику; -RST — сброс всех устройств; CLK — тактовый сигнал шины; PAR — бит четности для линий AD0…AD31 и C/BE0… C/BE3; -PERR — сигнал ошибки четности; -REQ0…-REQ3 — запрос от PCI-устройств на захват шины; -GNT0…-GNT3 — предоставление шины PCI-устройствам; -REQ64 — запрос на 64-битный обмен; -ASK64 — подтверждение 64-разрядного обмена; -INTRA, -INTRB, -INTRC, -INTRD — линии запросов прерываний; IDSEL — выбор устройства-исполнителя в циклах записи и чтения конфигурации. |

|

||||||||||||||||||||||||||||||||

Операция конфигурирования (циклы записи и чтения конфигурации) служит для автоматического распределения ресурсов компьютера при включении питания. В этих циклах для выбора (адресации) конфигурируемого устройства-исполнителя применяется специальный сигнал IDSEL, передаваемый в фазе адреса. Каждому PCI-устройству соответствует 256-байтная область конфигурации, где находится информация как о самом устройстве, так и о выделенных ему ресурсах. Область конфигурации не относится ни к адресному пространству памяти, ни к адресному пространству устройств ввода/вывода. Компьютер распределяет ресурсы между устройствами в соответствии с их особенностями, потребностями и ограничениями.

|

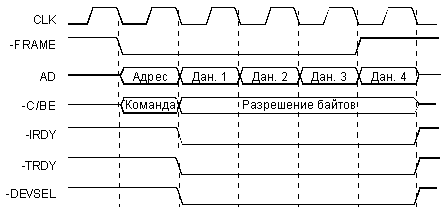

При синхронном обмене (рис. 8.11) в начале цикла (адресная фаза) по шине AD передается код адреса, а по линиям C/BE — код типа цикла (команда). Действительность адреса определяется сигналом -FRAME (по положительному фронту CLK после начала сигнала -FRAME). После опознания адреса исполнитель выставляет сигнал подтверждения выборки -DEVSEL, после чего начинается фаза данных. То есть можно сказать, что адрес передается асинхронно. |

В фазе данных по шине данных передаются слова данных, тактируемые положительными фронтами сигнала CLK. Сигналы готовности -IRDY и -TRDY выставляются в начале фазы данных и остаются активными до окончания цикла. По линиям -C/BE в фазе данных передаются сигналы разрешения байтов (то есть определяется формат передаваемых данных). Перед последним тактом передачи данных задатчик снимает сигнал -FRAME, после чего снимаются сигналы -IRDY, -TRDY и -DEVSEL.

|

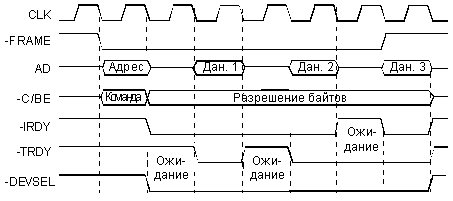

При асинхронном обмене по шине PCI (рис. 8.12) фаза адреса осуществляется как в предыдущем случае, а в фазе данных как задатчик, так и исполнитель могут приостанавливать обмен снятием своих сигналов готовности (соответственно, -IRDY и -TRDY). Цикл обмена (транзакция) при этом удлиняется за счет введения дополнительных тактов ожидания. Сигналы -FRAME и -DEVSEL |

вырабатываются аналогично случаю синхронного обмена.

Рис.

8.11. Синхронный обмен по шине PCI.

Рис.

8.11. Синхронный обмен по шине PCI. Рис.

8.12. Асинхронный обмен по шине PCI.

Рис.

8.12. Асинхронный обмен по шине PCI.