- •Объяснить принцип работы базового логического элемента стандартных серий имс ттл к155, км 155 по электрической схеме:

- •Объяснить работу электрической схемы логического элемента или-не.

- •Объяснить работу электрической схемы инвертора.

- •Объяснить работу электрической схемы с тремя состояниями на выходе.

- •Объяснить работу регистра по схеме:

- •Объяснить принцип схемной реализации матрицы пзу.

- •Объяснить работу счетчика по схеме:

- •Объяснить принцип действия дешифратора по схеме:

- •Объяснить принцип действия мультиплексора по схеме:

Объяснить работу регистра по схеме:

На Рис изображена схема регистра для записи, хранения и выдачи числа в прямом параллельном коде.

Перед записью числа на шину «установка» подают импульс и все триггеры восстанавливаются в нулевом положении, за тем импульс подают шину «запись» и разряды записываемого числа через схемы И поступают в соответствующие триггеры. Если в разряде числа записана 1, то триггеры устанавливаются в единичное состояние, а если в разряде записан 0, то нулевое состояние. В таком виде число хранится до поступления импульса «сброс».

Если число надо списать, то подают импульс на шину «чтение». При этом сигналы с прямых выходов триггеров через схемы И поступают к потребителю. Число в обратном коде считается точно также, но с инверсных выходов в триггере.

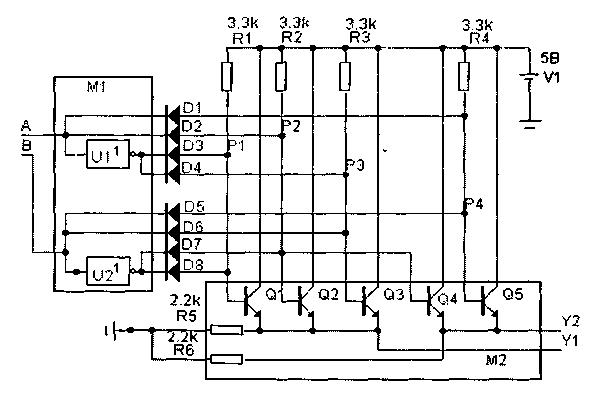

Объяснить принцип схемной реализации матрицы пзу.

Один

из вариантов схемной реализации матрицы

ПЗУ представлен на

рис.

Один

из вариантов схемной реализации матрицы

ПЗУ представлен на

рис.

Она представляет собой матричную сетку (коммутационную матрицу) ортогональных проводников, в местах пересечения которых могут быть установлены полупроводниковые элементы с односторонней проводимостью(диоды или транзисторы «Х»).

Схема имеет адресные входы А, В, выходы содержимого ячеек памяти Y, вывод для источника питания и общий вывод.

Верхняя часть схемы(матрица М1) представляет собой полный дешифратор. Если разрядность адреса равна m(m=2),то в дешифраторе на каждый разряд адреса приходится 4(m-1) горизонтальных линий, одна половина которых связана с входной шиной адреса непосредственно, а вторая — через инвертор. Число вертикальных линий в полном дешифраторе равно 2m.На вертикальной линии Pi (базе транзистора) появится положительный потенциал, если оба диода заперты сигналом логической единицы на их катодах. В результате вертикальные проводники формируют выходы полного дешифратора по адресным сигналам А и В:

Каждому адресу ПЗУ соответствует уровень логической единицы на одном вертикальном проводнике и логического нуля на всех остальных. Таким образом матрица Ml реализует логическую операцию И. Нижняя часть — программируемая матрица М2 реализует логическую операцию ИЛИ.

Если на базе любого из транзисторов, включенного в режиме эмиттерного повторителя, положительный потенциал, то на выходе Y. (горизонтальном проводнике) появляется логическая единица. Линии выходов называются линиями битов. ПЗУ нашего примера имеет организацию 4x2 бит, то есть по каждому из четырех адресов можно прочитать двухбитовое слово, содержащееся в соответствующей ячейке памяти

Объяснить работу счетчика по схеме:

Асинхронные счетчики представляют собой цепочку триггеров последовательно соединенных друг с другом. Импульсами счета для триггеров более старших разрядов являются сигналы с выходов триггеров младших разрядов.

Каждый триггер отображает один разряд числа, данная схема способна вести счет до максимума трёх разрядного двоичного числа 111. Перед началом счета на установочные входы триггеров подают импульс сброса, значит в счетчике записывается число 000.

Т-триггеры, используемые в данной схеме, работают в счетном режиме. Для этого на вход «Режим» подается лог. 1.

В счетчике импульсами счета для триггеров старших разрядов являются сигналы с выходов младших разрядов.

Частота срабатывания триггера старшего разряда в два раза меньше частоты срабатывания триггера младшего разряда.

По состоянию триггеров после каждого импульса счета судят о количестве поданных единиц информации на вход счетчика. При этом код, снимаемый с их выходов, последовательно увеличивается на единицу.