- •1. Виды технического обслуживания и ремонта оборудования с пу. Структура ремонтного цикла.

- •2. Перечень типовых регламентированных работ по каждому виду то электрической и электрон части оборудования. Учет то.

- •3. Основные задачи службы технического обслуживания и ремонта , структура и состав участка.

- •4.Функциональные требования подразделений и служб к персоналу, занятому эксплуатацией и обслуживанием.

- •5. Общие понятия: определение надеж, безотказн, долговечн, ремонтопригодн, наработки, срока службы, работоспособного состояния, поврежд и отказов

- •6. Требования к надёжности эспу. Причины отказов.

- •7. Источники получения информации о надежности эспу: статические данные об отказе по результатам эксплуатации.

- •8. Определение теории вероятности, случайного события, случайной величины и вероятности.

- •9. Распределение вероятностей, математическое ожидание и дисперсия случайных величин. Теоремы сложения и умножения вероятности.

- •10.Показатели надежности: вероятность безотказной работы, средняя наработка до отказа, интенсивность отказов. Кривая интенсивности отказов электронных систем.

- •11. Схемы для расчета надежности систем и последовательным и параллельным соединением элементов по средневероятным данным: выражения для вероятности безотказной работы, средней наработки до отказа.

- •13. Эффективность работы оператора(наладчика) в зависимости от уровня нагрузки. Виды и причины ошибок оператора.

- •14. Обзор схемных и конструкторских мер повышения надежности устройств программного управления.

- •15. Резервирование как способ обеспечения надежности. Примеры схемотехнического решения по обеспечению надежности для конкретного эспу

- •17. Виды средств технического диагностирования. Показатели и характеристики.

- •18. Характеристика этапов и задач контроля и технического диагностирования эспу.

- •19.Определение тестов и тестовых программ. Разновидности и структура тестов. Этапы построениядиагностических тестов.

- •20. Принцип проверки устройства с использованием тестовых программ. Обзор методов и примеры построения диагностических тестов.

- •21. Разработка диагностических справочников для определения неисправностей устройств по результатам прогона тестовых программ. Примеры диагностических справочников.

- •22. Встроенные программные ср-ва диагностирования эспу:диагностическое ядро и диагностируемая часть устр-ва.Резидентный проверяющий тест и режимы его выполнения.

- •23. Понятие самоконтроля микропроцессорных устройств пу.

- •24. Аппаратные средства диагностирования устройств пу. Обнаружение и исправление ошибок при схемном контроле (методы дублирования и сравнения, использование специальных кодов, алгебраический метод)

- •25. Специальные (избыточные) коды: определение, классификация, корректирующая способность. Избыточный код Хэмминга с проверкой на четность.

- •26. Применение кода Хэмминга для обнаружения и исправления одиночных ошибок хранения и передачи инфы.

- •27. Состав малогабаритных приборов для оперативного поиска и локализации неисправностей: тестеры логического анализатора. Сигнатурный анализатор.

- •28. Назначение, принцип действия и применение логического зонда. Проверка работоспособности электронных схем с их применением.

- •29. Назначение и функциональная схема логического анализатора. Сигнатурный анализатор.

- •30. Назначение и принцип работы генератора слов. Основные параметры и типы генераторов слов.

- •31. Назначение и состав диагностического стенда (уфк). Порядок выполнения проверочных операций на стенде.

- •32. Область применение технические данные структурная электрическая схема эспу 2с42-65

- •33. Назначение и технические данные цп. Обращение к памяти в ву.

- •34. Регистр состояния процессора. Внутреннее прерывание программ.

- •35. Организация стека. Блок-схема центрального процессора.

- •36. Режимы работы цп. Схема алгоритма диагностирования цп.

- •37. Типы форматы команд. Методы прямой и косвенной адресации.

- •38. Методы адресации с использованием счетчика команд.

- •39. Устройство и принцип действия субблока озу. Методика наладки озу.

- •40. Состав и емкость субблоков ппзу.

- •41. Устройство и принцип действия субблоков ппзу. Методика наладки ппзу.

- •42. Назначение и состав блока входных и выходных дискретных сигналов.

- •43. Устройство и принцип действия субблока выходных дискретных сигналов.

- •44. Устройство и принцип действия субблока входных дискретных сигналов.

- •45. Состав субблоков, реализующих следящую часть привода подачи в эспу. Назначение и состав субблока запитки датчиков sb-455.

- •46. Субблок оцифровки датчиков: назначение, физический принцип оцифровки дробной части оборота фазы, состав и принцип действия субблока по структурной схеме.

- •47. Состав и принцип действия субблока оцифровки sb-457 по принципиальной схеме: схема формирования импульсов счета, формирование импульсов оборота

- •48. Принцип действия узлов субблока оцифровки по принципиальной схеме: записи, сброса счетчиков полных оборотов фазы и дробной части.

- •49.Принцип действия субблока оцифровки по принципиальной схеме: узла определения движения, схемы выходных буферных регистров, схемы синхронизации, схемы запрета записи, дешифратора адреса.

- •50. Привязка субблока оцифровки к масштабу линейного перемещения

- •51. Назначение и принцип действия по структурной схеме субблока цап блока управления приводом.

- •52. Устройство субблока цап: резисторная схема преобразователей код-напряжение, выходные буферные регистры

- •53. Назначение и состав панели оператора эспу.

- •54. Устройство матрицы клавиатуры эспу

- •55. Усторйство и принцип действия субблока интерфейса клавиатуры по принципиальной схеме

- •56. Устройство и принцип работы блока боси по принципиальной схеме

- •57. Принцип отображения символьной инфы.

- •58. Устройство и принцип действия по принципиальной схеме субблока интерфейса блока связи с боси

- •59. Усторойство и принцип работы блока боси по принципиальной электрической схеме.

- •60. Назначение, состав и принцип действия по принципиальной схеме блока умножения.

- •61. Назначение, состав и принцип действия по принципиальной схеме блока преобразователей кодов.

- •62. Назначение, состав и принцип действия по принципиальной схеме субблока таймера.

- •63. Назначение, состав и принцип действия по принципиальной схеме субблока связи с фсу.

- •64. Назначение, состав и принцип действия по принципиальной схеме субблока связи с перфоратором.

- •65. Назначение, состав и принцип действия по принципиальной схеме субблока генератора опорной частоты.

- •66. Назначение, состав и принцип действия по принципиальной схеме субблока запитки датчиков. Расчетная схема косинусного формирователя.

- •67. Состав блоков стабилизаторов силового блока эспу

- •68. Принцип действия по принципиальной схеме компенсационного стабилизатора.

- •69. Принцип действия по принципиальной схеме импульсного стабилизатора.

- •70. Устройство и принцип действия по принципиальной схеме субблока расширителя магистрали.

49.Принцип действия субблока оцифровки по принципиальной схеме: узла определения движения, схемы выходных буферных регистров, схемы синхронизации, схемы запрета записи, дешифратора адреса.

Из блока пит датчиков через панель х1 поступает аналоговый сигнал который синхр частотой 5 или 2,5мГц на МС D7(К589ХЛ4)универс магистральный коммутатор байтовой инф. Опорный сигнал поступ на делит частоты кот вы на ЖКтриггере МС D2 т.е. обновл ниф происхордит с частотой 1,25мГц. Деление М2 произв с целью что бы след за периодом оцифровки дробн части оборота фаза вып операцию по управл информации в субблоке МС D 9,1 вып на D триггере и формир еденич импульс длительность кот пропорциональна разности фаз м-у опорным и измерит импульсами МС D12,1 выполняет фукцию силектора кот пропуск импульсы частоты пополнения на вход счетчика разряда 10-3 только во время присутствия его на втором входе импульса разности фаз, с вых МС D9.1. Обновления инф счетчика происходит с частотой 1,25мГц. Узел определ направл движ выявляет, произошел или нет и в каком направлении, в промежуток времени 800 мкс между обновлением инф в счетчиках 10-3 - 10-1 полный оборот фазы, и если произошел, пропускает поступ на него импульс ИО на суммирующ, или вычитающий входы счетчика 100 - DD20 типа К155ИЕ6.

Схема дешифратора адреса выполнена на дешифраторе DD5 типа К155ИД4 и логике DD1 типа К155ЛН1. Дешифратор стробируется по входам DD5/2/4 низ-ким уровнем принятого сигнала ДАТЧ, а на адресные входы поданы уровни ад-ресных разрядов А2…А4. На одном из выходов дешифратора (номер выхода соответствует коду адре-са на входе) появляется низкий уровень, и если на этой линии установлена ад-ресная перемычка, то после инверсии на DD1.4 высокий уровень поступает на схему определения «младший-старший». К каким регистрам обращается ЭВМ определяется уровень разряда А1 на входе логики DD15 типа К555ЛА3. При низком уровне адресного разряда А1 на выходе логики DD15/3 появит-ся низкий уровень, который поступит на вход ВК1 регистров DD14 и DD27. При высоком – к регистрам DD33 и DD36.

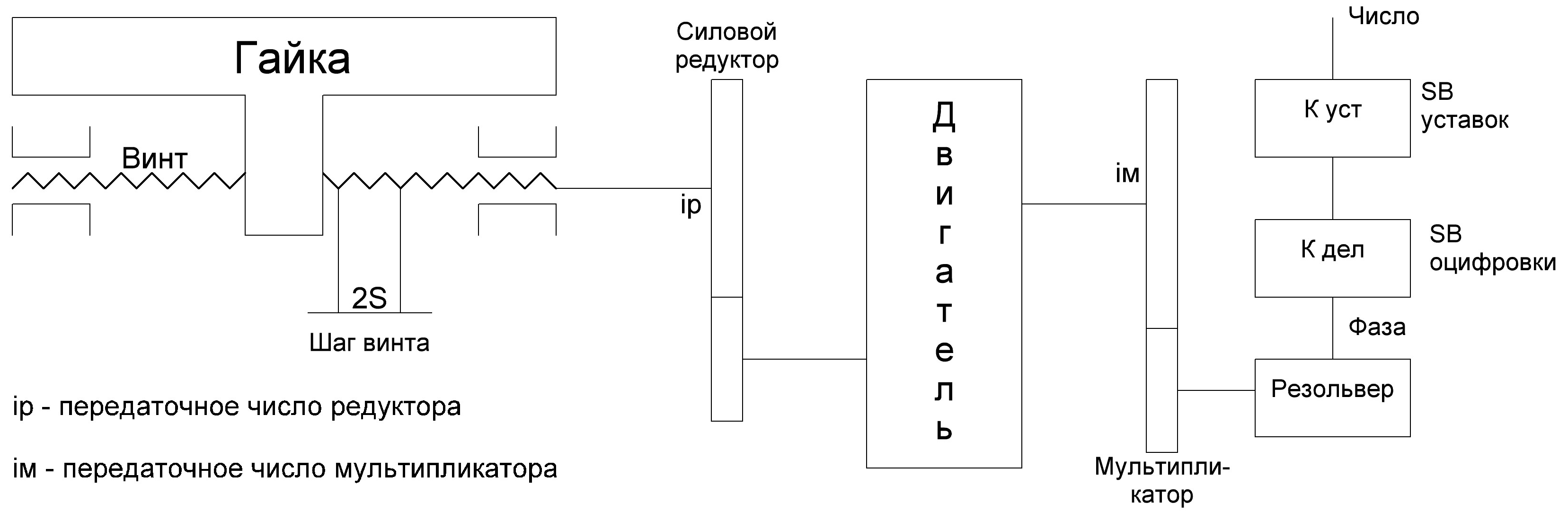

50. Привязка субблока оцифровки к масштабу линейного перемещения

При стыковке ЭСПУ со станком необходимо привести в соответствующие величины реальные перемещения координат с числом поступающих в программируемую часть для расчетов, если принять что дискретность перемещения с которой работает программируемая часть равна 1 мкм то величина перемещения должна быть равна числу поступающих в программируемую часть т.е. если повернуть винт на полный оборот, то при шаге винта S=10мм/об, стол переместится на величину 10мм,такое же число должно поступить в программируемую часть.

51. Назначение и принцип действия по структурной схеме субблока цап блока управления приводом.

Субблок ЦАП(SB-449)-Блок ЦАП содержит 2 цифроаналоговых преобразователя, который осуществляет прием цифровой информации с магистрали станка(адресов А01, А02, А03, А04) и данных(Д0-Д15) задающих конкретное напряжение которое необходимо подать устройству благодаря схемной реализации субблока), запоминание ее в соответствии с адресом ЦАП и преобразования в напряжение соответствующей величины и знака.