- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

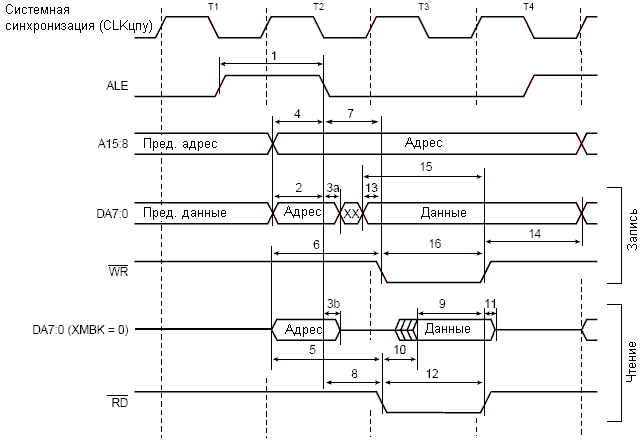

Временная диаграмма внешней памяти данных

Таблица 137. Характеристики внешней памяти данных (4.5 - 5.5В, без состояний ожидания)

|

Обозначение |

Параметр |

Генератор 8МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

16 |

МГц |

1 |

tLHLL |

Длительность импульса ALE |

115 |

|

1.0tCLCL-10 |

|

нс |

2 |

tAVLL |

Действительность адреса А до низкого уровня ALE |

57.5 |

|

0.5tCLCL-5(1) |

|

нс |

3а |

tLLAX_ST |

Удержание адреса после установки низкого уровня на ALE во время записи |

5 |

|

5 |

|

нс |

3b |

tLLAX_LD |

Удержание адреса после установки низкого уровня на ALE во время чтения |

5 |

|

5 |

|

нс |

4 |

tAVLLC |

Действительность адреса С до низкого уровня ALE |

57,5 |

|

0.5tCLCL-5(1) |

|

нс |

5 |

tAVRL |

Действительность адреса до низкого уровня на RD |

115 |

|

1.0tCLCL-10 |

|

нс |

6 |

tAVWL |

Действительность адреса до низкого уровня на WR |

115 |

|

1.0tCLCL-10 |

|

нс |

7 |

tLLWL |

Время после установки низкого уровня на ALE до появления низкого уровня на WR |

47,5 |

67,5 |

0.5tCLCL-15(2) |

0.5tCLCL+5(2) |

нс |

8 |

tLLRL |

Время после установки низкого уровня на ALE до появления низкого уровня на RD |

47,5 |

67,5 |

0.5tCLCL-15(2) |

0.5tCLCL+5(2) |

нс |

9 |

tDVRH |

Готовность данных до появления высокого уровня на RD |

40 |

|

40 |

|

нс |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

75 |

|

1.0tCLCL-50 |

нс |

11 |

tRHDX |

Удержание данных после установки лог. 1 на RD |

0 |

|

0 |

|

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

115 |

|

1.0tCLCL-10 |

|

нс |

13 |

tDVWL |

Врем готовности данных до появления лог. 0 на WR |

42,5 |

|

0.5tCLCL-20(1) |

|

нс |

14 |

tWHDX |

Удержание данных после подачи лог. 1 на WR |

115 |

|

1.0tCLCL-10 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

125 |

|

1.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

115 |

|

1.0tCLCL-10 |

|

нс |

Прим.:

Здесь полагается 50%-ое заполнение синхронизирующих импульсов. Половина периода фактически равна длительности единичного импульса внешнего тактового сигнала на XTAL1.

Здесь полагается 50%-ое заполнение синхронизирующих импульсов. Половина периода фактически равна длительности нулевого импульса внешнего тактового сигнала на XTAL1.

Таблица 138. Характеристики внешней памяти данных с однотактным состоянием ожидания (4.5 - 5.5В)

|

Обозначение |

Параметр |

Генератор 8МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

16 |

МГц |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

200 |

|

2.0tCLCL-50 |

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

240 |

|

2.0tCLCL-10 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

240 |

|

2.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

240 |

|

1.0tCLCL-10 |

|

нс |

Таблица 139. Характеристики внешней памяти данных (4.5 - 5.5В, SRWn1 = 1, SRWn0 = 0)

|

Обозначение |

Параметр |

Генератор 8МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

16 |

МГц |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

325 |

|

3.0tCLCL-50 |

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

365 |

|

3.0tCLCL-10 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

375 |

|

3.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

365 |

|

3.0tCLCL-10 |

|

нс |

Таблица 140. Характеристики внешней памяти данных (4.5 - 5.5В, SRWn1 = 1, SRWn0 = 1)

|

Обозначение |

Параметр |

Генератор 8МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

16 |

МГц |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

325 |

|

3.0tCLCL-50 |

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

365 |

|

3.0tCLCL-10 |

|

нс |

14 |

tWHDX |

Удержание данных после подачи лог. 1 на WR |

240 |

|

2.0tCLCL-10 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

375 |

|

3.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

365 |

|

3.0tCLCL-10 |

|

нс |

Таблица 141. Характеристики внешней памяти данных (2.7 - 5.5В, без состояний ожидания)

|

Обозначение |

Параметр |

Генератор 4МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

8 |

МГц |

1 |

tLHLL |

Длительность импульса ALE |

235 |

|

1.0tCLCL-15 |

|

нс |

2 |

tAVLL |

Действительность адреса А до низкого уровня ALE |

115 |

|

0.5tCLCL-10(1) |

|

нс |

3а |

tLLAX_ST |

Удержание адреса после установки низкого уровня на ALE во время записи |

5 |

|

5 |

|

нс |

3b |

tLLAX_LD |

Удержание адреса после установки низкого уровня на ALE во время чтения |

5 |

|

5 |

|

нс |

4 |

tAVLLC |

Действительность адреса С до низкого уровня ALE |

115 |

|

0.5tCLCL-10(1) |

|

нс |

5 |

tAVRL |

Действительность адреса до низкого уровня на RD |

235 |

|

1.0tCLCL-15 |

|

нс |

6 |

tAVWL |

Действительность адреса до низкого уровня на WR |

235 |

|

1.0tCLCL-15 |

|

нс |

7 |

tLLWL |

Время после установки низкого уровня на ALE до появления низкого уровня на WR |

115 |

130 |

0.5tCLCL-10(2) |

0.5tCLCL+5(2) |

нс |

8 |

tLLRL |

Время после установки низкого уровня на ALE до появления низкого уровня на RD |

115 |

130 |

0.5tCLCL-10(2) |

0.5tCLCL+5(2) |

нс |

9 |

tDVRH |

Готовность данных до появления высокого уровня на RD |

45 |

|

45 |

|

нс |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

190 |

|

1.0tCLCL-50 |

нс |

11 |

tRHDX |

Удержание данных после установки лог. 1 на RD |

0 |

|

0 |

|

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

235 |

|

1.0tCLCL-15 |

|

нс |

13 |

tDVWL |

Время готовности данных до появления лог. 0 на WR |

105 |

|

0.5tCLCL-20(1) |

|

нс |

14 |

tWHDX |

Удержание данных после подачи лог. 1 на WR |

235 |

|

1.0tCLCL-15 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

250 |

|

1.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

235 |

|

1.0tCLCL-15 |

|

нс |

Прим.:

Здесь полагается 50%-ое заполнение синхронизирующих импульсов. Половина периода фактически равна длительности единичного импульса внешнего тактового сигнала на XTAL1.

Здесь полагается 50%-ое заполнение синхронизирующих импульсов. Половина периода фактически равна длительности нулевого импульса внешнего тактового сигнала на XTAL1.

Таблица 142. Характеристики внешней памяти данных (2.7 - 5.5В, SRWn1 = 0, SRWn0 = 1)

|

Обозначение |

Параметр |

Генератор 4МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

8 |

МГц |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

440 |

|

2.0tCLCL-60 |

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

485 |

|

2.0tCLCL-15 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

500 |

|

2.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

485 |

|

2.0tCLCL-15 |

|

нс |

Таблица 143. Характеристики внешней памяти данных (2.7 - 5.5В, SRWn1 = 1, SRWn0 = 0)

|

Обозначение |

Параметр |

Генератор 4МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

8 |

МГц |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

690 |

|

3.0tCLCL-60 |

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

735 |

|

3.0tCLCL-15 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

750 |

|

3.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

735 |

|

3.0tCLCL-15 |

|

нс |

Таблица 144. Характеристики внешней памяти данных (2.7 - 5.5В, SRWn1 = 1, SRWn0 = 1)

|

Обозначение |

Параметр |

Генератор 4МГц |

Переменный генератор |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

||||

0 |

1/tCLCL |

Частота генератора |

|

|

0.0 |

8 |

МГц |

10 |

tRLDV |

Время подготовки данных после установки лог. 0 на RD |

|

690 |

|

3.0tCLCL-60 |

нс |

12 |

tRLRH |

Длительность импульса чтения RD |

735 |

|

3.0tCLCL-15 |

|

нс |

14 |

tWHDX |

Удержание данных после подачи лог. 1 на WR |

485 |

|

2.0tCLCL-15 |

|

нс |

15 |

tDVWH |

Действительность данных до появления лог.1 на WR |

750 |

|

3.0tCLCL |

|

нс |

16 |

tWLWH |

Длительность импульса записи WR |

735 |

|

3.0tCLCL-15 |

|

нс |

Рисунок

156. Временная диаграмма внешней памяти

(SRWn1 = 0, SRWn0 = 0)

Рисунок

156. Временная диаграмма внешней памяти

(SRWn1 = 0, SRWn0 = 0)

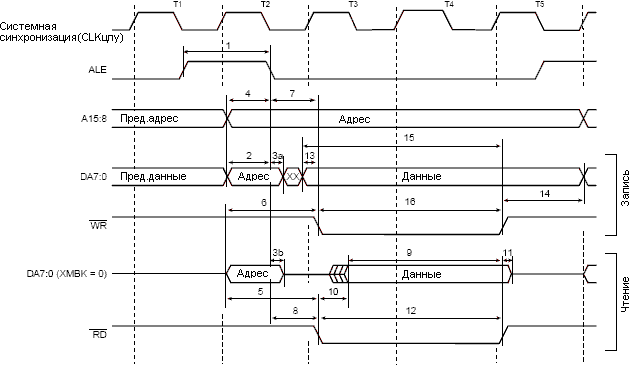

Рисунок

157. Временная диаграмма внешней памяти

(SRWn1 = 0, SRWn0 = 1)

Рисунок

157. Временная диаграмма внешней памяти

(SRWn1 = 0, SRWn0 = 1)

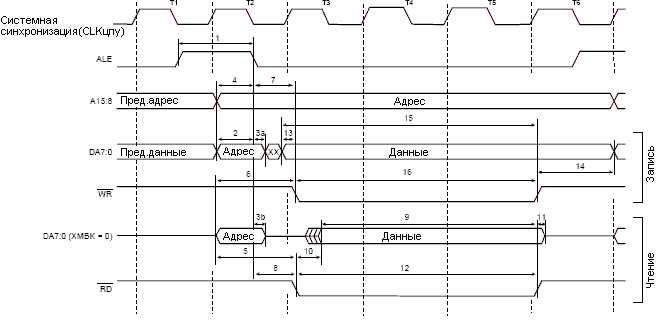

Рисунок

158. Временная диаграмма внешней памяти

(SRWn1 = 1, SRWn0 = 0)

Рисунок

158. Временная диаграмма внешней памяти

(SRWn1 = 1, SRWn0 = 0)

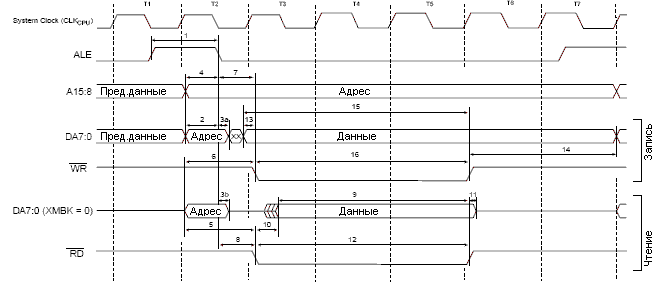

Рисунок

158. Временная диаграмма внешней памяти

(SRWn1 = 1, SRWn0 = 1)(1)

Рисунок

158. Временная диаграмма внешней памяти

(SRWn1 = 1, SRWn0 = 1)(1)

Прим.:

В последнем периоде (T4-T7) импульс ALE присутствует только в том случае, если следующая инструкция осуществляет доступ к ОЗУ (внутреннему или внешнему).