- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

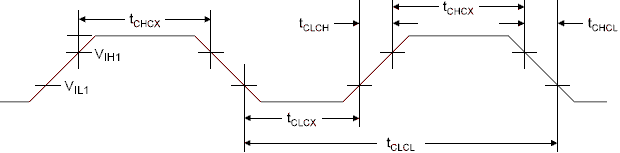

Требования к характеристикам внешнего тактового сигнала

Рисунок

152. Осциллограмма внешнего тактового

сигнала

Рисунок

152. Осциллограмма внешнего тактового

сигнала

Таблица 132. Параметры внешнего тактового сигнала

Обозначение |

Параметр |

VCC = 2.7В…5.5В |

VCC = 4.5В…5.5В |

Ед.изм. |

||

мин. |

макс. |

мин. |

макс. |

|||

1/tCLCL |

Частота генератора |

0 |

8 |

0 |

16 |

МГц |

tCLCL |

Период синхронизации |

125 |

|

62,5 |

|

нс |

tCHCX |

Длительность единичного импульса |

50 |

|

25 |

|

нс |

tCLCX |

Длительность нулевого импульса |

50 |

|

25 |

|

нс |

tCLCH |

Длительность нарастающего фронта |

|

1,6 |

|

0,5 |

мкс |

tCHCL |

Длительность падающего фронта |

|

1,6 |

|

0,5 |

мкс |

tCLCL |

Разброс периодов смежных импульсов |

|

2 |

|

2 |

% |

Таблица 133. Типичные частоты при тактировании от внешней RC-цепи

R, кОм |

C, пФ |

f |

100 |

70 |

TBD(2) |

31,5 |

20 |

TBD(2) |

6,5 |

20 |

TBD(2) |

Прим.:

Сопротивление R должно находиться в пределах 3 кОм…100 кОм, а емкость не менее 20 пФ. Значения C представлены в таблице с учетом емкости вывода микроконтроллера. Емкость вывода может варьироваться в зависимости от типа корпуса.

TBD означает, что точное значение величины находится в состоянии определения.

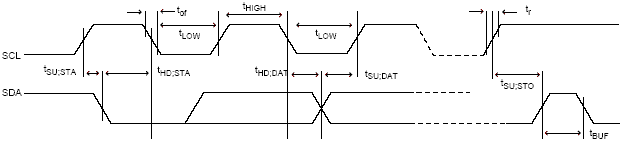

Характеристики двухпроводного последовательного интерфейса

В таблице 134 описываются требования к устройствам, подключаемых к двухпроводной последовательной шине. Двухпроводной последовательный интерфейс ATmega128 отвечает данным требованиям или превосходит их в указанных условиях.

Обозначения параметров показаны на рисунке 153.

Таблица 134. Требования к двухпроводной последовательной шине

Обозн. |

Параметр |

Условия измерения |

Мин. |

Макс. |

Ед.изм. |

VIL |

Входное напряжение низкого уровня |

|

-0.5 |

0.3 VCC |

В |

VIH |

Входное напряжение высокого уровня |

|

0.7 VCC |

VCC + 0.5 |

В |

Vгис(1) |

Гистерезис триггеров Шмитта |

|

0.05 VCC (2) |

- |

В |

VOL (1) |

Выходное напряжение низкого уровня |

Вытекающий ток 3 мА |

0 |

0,4 |

В |

tr (1) |

Время нарастания SDA и SCL |

|

20 + 0.1Cb (3)(2) |

300 |

нс |

tof (1) |

Длительность спада с VIHmin до VILmax |

10 пФ < Cb < 400 пФ(3) |

20 + 0.1Cb (3)(2) |

250 |

нс |

tSP (1) |

Длительность подавляемых импульсов входным фильтром |

|

0 |

50(2) |

нс |

Ii |

Входной ток каждой линии ввода-вывода |

0.1 Vсс < Vi < 0.9 Vсс |

-10 |

10 |

мкА |

Ci (1) |

Емкость каждой линии ввода-вывода |

|

- |

10 |

пФ |

fSCL |

Частота синхронизации SCL |

fCK(4)>макс (16fSCL, 250КГц)(5) |

0 |

400 |

кГц |

Rp |

Значение подтягивающего резистора |

fSCL 100 кГц |

VCC-0,4В ----------- 3 мА |

1000 нс ----------- Cb |

Ом |

fSCL > 100 кГц |

VCC-0,4В ----------- 3 мА |

300 нс ----------- Cb |

Ом |

||

tHD;STA |

Время удержания условия СТАРТ (повторный старт) |

fSCL 100 кГц |

4.0 |

- |

мкс |

fSCL > 100 кГц |

0.6 |

- |

мкс |

||

tLOW |

Длительность нулевого импульса SCL |

fSCL 100 кГц(6) |

4.7 |

- |

мкс |

fSCL > 100 кГц(7) |

1.3 |

- |

мкс |

||

tHIGH |

Длительность единичного импульса SCL |

fSCL 100 кГц |

4.0 |

- |

мкс |

fSCL > 100 кГц |

0.6 |

- |

мкс |

||

tSU;STA |

Время установки условия повторный старт |

fSCL 100 кГц |

4.7 |

- |

мкс |

fSCL > 100 кГц |

0.6 |

- |

мкс |

||

tHD;DAT |

Время удержания данных |

fSCL 100 кГц |

0 |

3.45 |

мкс |

fSCL > 100 кГц |

0 |

0.9 |

мкс |

||

tSU;DAT |

Время установки данных |

fSCL 100 кГц |

250 |

- |

нс |

fSCL > 100 кГц |

100 |

- |

нс |

||

tSU;STO |

Время установки условия СТОП |

fSCL 100 кГц |

4.0 |

- |

мкс |

fSCL > 100 кГц |

0.6 |

- |

мкс |

||

tBUF |

Время освобождения шины между условиями СТОП и СТАРТ |

fSCL 100 кГц |

4.7 |

- |

мкс |

Прим.:

Значение данного параметра у ATmega128 проверено не полностью.

Только для fSCL > 100 кГц

Cb - емкость одной линии шины в пФ.

fCK - тактовая частота ЦПУ

Данное требования относится ко всей работе двухпроводного последовательного интерфейса ATmega128. Другие устройства подключенные к двухпроводной последовательной шине могут отвечать только общим требованиям к fSCL.

Фактическая длительность низкого уровня, генерируемого двухпроводным последовательным интерфейсом ATmega128, составляет (1/fSCL - 2/fCK), таким образом, частота fCK должна быть больше 6 МГц для более точного выполнения требования к длительности низкого уровня при fSCL = 100 кГц.

Фактическая длительность низкого уровня, генерируемого двухпроводным последовательным интерфейсом ATmega128, составляет (1/fSCL - 2/fCK), таким образом, требования к длительности низкого уровня не строго выполняются для fSCL > 308 кГц, когда fCK = 8 МГц. Однако, микроконтроллеры ATmega128, подключенные к шине, могут связываться на полной скорости (400 кГц) между собой, а также с другими устройствами с надлежащим значением tLOW.

Рисунок

153. Временная диаграмма двухпроводной

последовательной шины

Рисунок

153. Временная диаграмма двухпроводной

последовательной шины