- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

Внешняя синхронизация

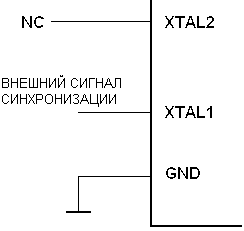

Если необходимо тактировать микроконтроллер от внешнего источника, то его необходимо подключить к выводу XTAL1 (см. рисунок 21). В этом случае внешняя синхронизация должна быть разрешена записью в конфигурационные биты CKSEL значения “0000”. Если запрограммировать конфигурационный бит CKOPT, то между XTAL1 и GND будет подключен внутренний конденсатор номиналом 36 пФ.

Рисунок

21 – Схема подключения внешнего источника

синхронизации

Рисунок

21 – Схема подключения внешнего источника

синхронизации

После выбора данного источника синхронизации длительность задержки при запуске определяется конфигурационными битами SUT как показано в таблице 16.

Таблица 16 – Длительность задержки при запуске при выборе внешней синхронизации

SUT1..0 |

Длительность задержки при выходе из режима выключения и экономичного режима |

Дополнительная задержка после сброса (VCC= 5.0В) |

Рекомендуемые условия для применения |

00 |

6 CK |

- |

Включен детектор питания BOD |

01 |

6 CK |

4.1 мс |

Быстро нарастающее питание |

10(1) |

6 CK |

65 мс |

Медленно нарастающее питание |

11 |

Зарезервировано |

||

После подключения внешнего тактового источника необходимо избегать внезапных изменений его частоты для гарантирования стабильности работы микроконтроллера. Если на следующем такте частота изменится более чем на 2% по сравнению с предыдущим, то поведение микроконтроллера может стать непредсказуемым. Данный механизм реализован для гарантирования нахождения микроконтроллера в состоянии сброса в процессе таких изменений тактовой частоты.

Генератор таймер-счетчика

Выводы генератора таймера-счетчика TOSC1 и TOSC2 предназначены для непосредственного подключения кварцевого резонатора. В этом случае не требуются внешние конденсаторы. Генератор оптимизирован для совместной работы с часовым кварцевым резонатором 32.768 кГц. Подключение внешнего тактового источника к выводу TOSC1 не рекомендуется.

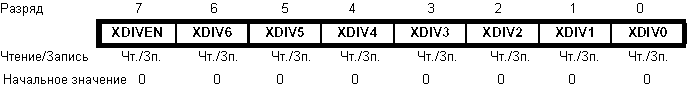

Регистр управления делением XTAL – XDIV

Регистр управления делением XTAL используется для деления частоты тактового источника на одно из значений в диапазоне 2 - 129. Данная функция может использоваться при необходимости оптимизации энергопотребления.

Разряд 7 – XDIVEN: Разрешение деления XTAL

Если в XDIVEN записать лог.1, то тактовые частоты ЦПУ и периферийных модулей (clkI/O, clkADC, clkCPU, clkFLASH) будут поделены на коэффициент, заданный значениями XDIV6 - XDIV0. Данный бит можно программировать в работающем приложении для варьирования тактовой частотой.

Разряды 6..0 – XDIV6..XDIV0: Разряды 6…0 коэффициента деления XTAL

Данные разряды определяют значение коэффициента деления, который вступает в силу после записи лог. 1 в XDIVEN. Если значение данных бит обозначит как d, то результирующая тактовая частота (fCLK) ЦПУ и периферийных модулей может быть найдена по выражению:

![]()

Изменять значение данных разрядов допускается, только если XDIVEN=0. Когда в XDIVEN записывается лог.1, то записываемые одновременно с ней значения XDIV6..XDIV0 будут использоваться как коэффициент деления. Во время записи в XDIVEN лог. 0 одновременно записываемые значения в разряды XDIV6..XDIV0 отклоняются. Поскольку, делитель выполняет снижение входной тактовой частоты микроконтроллера, то после разрешения деления также снижается быстродействие всех периферийных модулей.

Примечание: После разрешения деления тактовой частоты таймер-счетчик 0 может быть использован только в асинхронном режиме. Частота асинхронного источника должна быть не менее чем в 4 раза меньше результирующей (поделенной) частоты синхронизации. В противном случае не гарантируется определение запроса на прерывание и корректность доступа к регистрам таймера-счетчика 0.