- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

Программирование памяти

Биты защиты памяти программ и данных

ATmega128 содержит 6 битов защиты, которые можно оставить в незапрограммированном состоянии ("1") или же запрограммировать ("0") для активизации дополнительных функций, представленных в таблице 117. Стирание бит защиты (установка "1") может быть выполнена только командой стирание кристалла (Chip Erase).

Таблица 116. Байт с битами защиты

Биты защиты |

Разряд |

Описание |

Исходное значение |

|

7 |

- |

1 (незапрограммированный) |

|

6 |

- |

1 (незапрограммированный) |

BLB12 |

5 |

Бит защиты загрузочного сектора |

1 (незапрограммированный) |

BLB11 |

4 |

Бит защиты загрузочного сектора |

1 (незапрограммированный) |

BLB02 |

3 |

Бит защиты загрузочного сектора |

1 (незапрограммированный) |

BLB01 |

2 |

Бит защиты загрузочного сектора |

1 (незапрограммированный) |

LB2 |

1 |

Бит защиты |

1 (незапрограммированный) |

LB1 |

0 |

Бит защиты |

1 (незапрограммированный) |

Прим.: "1" означает незапрограммированное состояние, а "0" - запрограммированное.

Таблица 117. Режимы защиты

Биты защиты памяти |

Тип защиты |

||

Режим LB |

LB2 |

LB1 |

|

1 |

1 |

1 |

Нет защиты памяти. |

2 |

1 |

0 |

Дальнейшее программирование флэш-памяти и ЭСППЗУ отключено при параллельном и последовательном (SPI/JTAG) программировании. Конфигурационные биты защищены при любом способе программирования(1) |

3 |

0 |

0 |

Дальнейшее программирование и проверка флэш-памяти и ЭССПЗУ отключена как при параллельном, так и при последовательном программировании через SPI/JTAG. Конфигурационные биты защищены при любом способе программирования(1) |

Режим BLB0 |

BLB02 |

BLB01 |

|

1 |

1 |

1 |

Нет ограничений действия инструкций SPM или (E)LPM при адресации сектора прикладной программы. |

2 |

1 |

0 |

SPM не записывает данные в сектор прикладной программы. |

3 |

0 |

0 |

SPM не записывает данные в сектор прикладной программы, а выполнение инструкции (E)LPM в загрузочном секторе не позволяет считать данные из сектора прикладной программы. Если векторы прерываний размещены в загрузочном секторе, то при выполнении команд в секторе прикладной программы прерывания отключаются. |

4 |

0 |

1 |

Выполнение (E)LPM в загрузочном секторе не позволяет считать данные из сектора прикладной программы. Если векторы прерываний размещены в загрузочном секторе, то при выполнении команд в секторе прикладной программы прерывания отключаются. |

Режим BLB1 |

BLB12 |

BLB11 |

|

1 |

1 |

1 |

Нет ограничений действия инструкций SPM или (E)LPM при адресации загрузочного сектора. |

2 |

1 |

0 |

SPM не записывает данные в загрузочный сектор. |

3 |

0 |

0 |

SPM не записывает данные в загрузочный сектор, а выполнение инструкции (E)LPM в секторе прикладной программы не позволяет считать данные из загрузочного сектора. Если векторы прерываний размещены в секторе прикладной программы, то при выполнении команд в загрузочном секторе прерывания отключаются. |

4 |

0 |

1 |

Выполнение (E)LPM в секторе прикладной программы не позволяет считать данные из загрузочного сектора. Если векторы прерываний размещены в секторе прикладной программы, то при выполнении команд в загрузочном секторе прерывания отключаются. |

Прим.:

Конфигурационные биты необходимо программировать перед программированием бит защиты.

"1" означает незапрограммированное состояние, а "0" - запрограммированное.

Конфигурационные биты

ATmega128 имеет три конфигурационных байта. Таблицы 118 - 120 кратко описывают функционирование и расположение всех конфигурационных бит. Обратите внимание, что если конфигурационный бит запрограммирован, то при его считывании возвращается лог. 0.

Таблица 118. Расширенный конфигурационный байт

Наименование бита |

Разряд |

Описание |

Исходное значение |

- |

7 |

- |

1 |

- |

6 |

- |

1 |

- |

5 |

- |

1 |

- |

4 |

- |

1 |

- |

3 |

- |

1 |

- |

2 |

- |

1 |

M103C(1) |

1 |

Режим совместимости с ATmega103 |

0 (запрограммированное) |

WDTON(2) |

0 |

Активизация сторожевого таймера |

1 (незапрограммированное) |

Прим.:

См. "Совместимость ATmega103 и ATmega128".

См. "Регистр управления сторожевым таймером - WDTCR".

Таблица 119. Старший конфигурационный байт

Наименование бита |

Разряд |

Описание |

Исходное значение |

OCDEN(4) |

7 |

Включение встроенного блока отладки |

1 (незапрограммированное, функция встроенной отладки отключена) |

JTAGEN(5) |

6 |

Включение JTAG-интерфейса |

0 (запрограммированное, JTAG включен) |

SPIEN(1) |

5 |

Разрешение последовательной загрузки программы и данных |

0 (запрограммированное, программирование через SPI разрешено) |

CKOPT(2) |

4 |

Настройка генератора |

1 (незапрограммированное) |

EESAVE |

3 |

Запрет стирания ЭСППЗУ командой стирание кристалла |

1 (незапрограммированное, стирание кристалла вызывает стирание ЭСППЗУ) |

BOOTSZ1 |

2 |

Выбор размера загрузочного сектора (см. табл. 113) |

0 (запрограммированное) (3) |

BOOTSZ0 |

1 |

Выбор размера загрузочного сектора (см. табл. 113) |

0 (запрограммированное)(3) |

BOOTRST |

0 |

Выбор вектора сброса |

1 (незапрограммированное) |

Прим.:

Конфигурационный бит SPIEN недоступен в режиме последовательного программирования через SPI.

Функционирование конфигурационного бита CKOPT зависит от установок бит CKSEL. См. "Источники синхронизации".

Исходное значение бит BOOTSZ1..0 соответствует выбору максимальному размеру загрузочного сектора. См. таблицу 113.

Не забудьте отключить бит OCDEN перед поставкой готового изделия заказчику, независимо от того какие установки имеют биты защиты и конфигурационный бит JTAGEN. Если бит OCDEN будет запрограммирован, то некоторые части системы синхронизации микроконтроллера останутся в работе при переводе микроконтроллера в экономичные режимы командой sleep. В этом случае микроконтроллер будет потреблять повышенную мощность.

Если интерфейс JTAG оставлен неподключенным, то конфигурационный бит JTAGEN должен быть по возможности отключен. Это позволит избежать статический ток через вывод TDO JTAG-интерфейса.

Таблица 120. Младший конфигурационный байт

Наименование бит |

Разряд |

Описание |

Исходное значение |

BODLEVEL |

7 |

Порог срабатывания супервизора питания |

1 (незапрограммированное) |

BODEN |

6 |

Разрешение супервизора питания |

1 (незапрограммированное, супервизор отключен) |

SUT1 |

5 |

Выбор времени запуска |

1 (незапрограммированное)(1) |

SUT0 |

4 |

Выбор времени запуска |

0 (запрограммированное)(1) |

CKSEL3 |

3 |

Выбор тактового источника |

0 (запрограммированное)(2) |

CKSEL2 |

2 |

Выбор тактового источника |

0 (запрограммированное)(2) |

CKSEL1 |

1 |

Выбор тактового источника |

0 (запрограммированное)(2) |

CKSEL0 |

0 |

Выбор тактового источника |

1 (незапрограммированное)(2) |

Прим.:

Исходные установки SUT1..0 соответствуют выбору максимальному времени старта. Подробности представлены в таблице 14.

Исходные установки CKSEL3..0 соответствуют выбору внутреннего RC-генератора частотой 1 МГц. Подробности представлены в таблице 6.

На состояние конфигурационных бит не оказывает влияния команда стирания кристалла "Chip Erase". Обратите внимание, что доступ к конфигурационным битам заблокирован, если запрограммирован бит защиты LB1. Поэтому, конфигурационные биты необходимо программировать перед программированием бит защиты.

Защита конфигурационных бит

Доступ к конфигурационным битам блокируется, если микроконтроллер перешел в режим программирования и изменение их значений не даст никакого эффекта до тех пор, пока микроконтроллер не выйдет из режима программирования. Данное не распространяется на бит EESAVE и он может быть запрограммирован в любой момент. Доступ к конфигурационным битам также блокируется при подаче питания в нормальном режиме работы (не программировании).

Сигнатурные байты

Все микроконтроллеры Atmel имеют трехбайтный сигнатурный код, который позволяет идентифицировать устройство. Код можно считать как в параллельном, так и в последовательном режимах программирования, в т.ч. когда микроконтроллер защищен. У каждого байта сигнатурного кода имеется свой собственный адрес и назначение.

Для ATmega128 сигнатурными байтами являются:

$000: $1E (идентифицирует производителя: Atmel)

$001: $97 (идентифицирует размер флэш-памяти: 128 кбайт)

$002: $02 (идентифицирует тип микроконтроллера: ATmega128, если байт $001 равен $97)

Калибровочный байт

Внутри ATmega128 хранятся четыре различных калибровочных значений для внутреннего RC-генератора. Данные значения хранятся по адресам 0x000, 0x0001, 0x0002 и 0x0003 и соответствуют частотам генератора 1, 2, 4 и 8 МГц. В процессе сброса в регистр OSCCAL автоматически записывается значение калибровочного байта для частоты 1 МГц. Если используется другая частота, то соответствующее значение должно быть вручную записано в регистр OSCCAL (см. "Регистр калибровки генератора - OSCCAL").

Параметры параллельного программирования, расположение выводов и команды

В данном разделе описывается как у ATmega128 запрограммировать и проверить флэш-память, ЭСППЗУ, биты защиты и конфигурационные биты. Полагается, что длительность импульсов не менее 250 нс, если не имеется других указаний.

Наименование сигналов

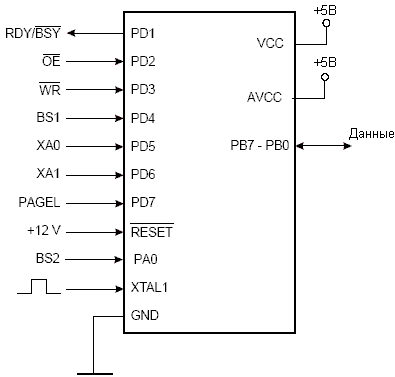

На рисунке 135 и в таблице 121 показывается расположение и назначение выводов ATmega128, которые используются для параллельного программирования. Выводы XA1/XA0 определяют выполняемое действие при положительном фронте на выводе XTAL1 (см. табл. 123).

Подачей импульсов на WR или OE в зависимости от загруженной команды определяется выполняемое действие. Описание команд представлено в таблице 124.

Рисунок

135. Параллельное программирование

Рисунок

135. Параллельное программирование

Таблица 121. Расположение и назначение выводов программирования

Наименование сигнала в режиме программирования |

Наименование вывода |

Направление |

Функция |

RDY/BSY |

PD1 |

Выход |

0 - микроконтроллер занят программированием;1 - микроконтроллер готов к загрузке новой команды |

OE |

PD2 |

Вход |

Разрешение вывода (активный низкий) |

WR |

PD3 |

Вход |

Строб записи (активный низкий) |

BS1 |

PD4 |

Вход |

Выбор байта 1 ("0" выбирает младший байт, "1" выбирает старший байт) |

XA0 |

PD5 |

Вход |

Код функции XTAL, разряд 0 |

XA1 |

PD6 |

Вход |

Код функции XTAL, разряд 1 |

PAGEL |

PD7 |

Вход |

Загрузка страницы данных в память программ и ЭСППЗУ |

BS2 |

PA0 |

Вход |

Выбор байта 2 ("0" выбирает младший байт, "1" выбирает 2-ой старший байт) |

DATA |

PB7-0 |

Вход/выход |

Двунаправленная шина данных (выводит данные, когда OE=0 ) |

Таблица 122. Состояния выводов, которые используются для входа в режим программирования

Вывод |

Обозначение |

Значение |

PAGEL |

Prog_enable[3] |

0 |

XA1 |

Prog_enable[2] |

0 |

XA0 |

Prog_enable[1] |

0 |

BS1 |

Prog_enable[0] |

0 |

Таблица 123. Назначение кодов XA1 и XA0

XA1 |

XA0 |

Выполняемая функция во время импульса на XTAL1 |

0 |

0 |

Загрузка адреса флэш-памяти или ЭСППЗУ (какой байт адреса, старший или младший определяется BS1) |

0 |

1 |

Загрузка данных (какой байт данных, старший или младший определяется BS1) |

1 |

0 |

Загрузка команды |

1 |

1 |

Нет никаких действий (холостой ход) |

Таблица 124. Коды команд

Код команды |

Функция |

1000 0000 |

Стирание кристалла (Chip Erase) |

0100 0000 |

Запись конфигурационных бит |

0010 0000 |

Запись бит защиты |

0001 0000 |

Запись флэш-памяти |

0001 0001 |

Запись ЭСППЗУ |

0000 1000 |

Чтение сигнатурных байт и калибровочного байта |

0000 0100 |

Чтение конфигурационных бит и бит защиты |

0000 0010 |

Чтение флэш-памяти |

0000 0011 |

Чтение ЭСППЗУ |

Таблица 125. Количество слов в странице и количество страниц во флэш-памяти

Размер флэш-памяти |

Размер страницы |

PCWORD |

Кол. страниц |

PCPAGE |

PCMSB |

64 кслов (128 кбайт) |

128 слов |

PC[6:0] |

512 |

PC[15:7] |

15 |

Таблица 126. Количество слов в странице и количество страниц в ЭСППЗУ

Размер ЭСППЗУ |

Размер страницы |

PCWORD |

Кол. страниц |

PCPAGE |

EEAMSB |

4 кбайт |

8 байт |

EEA[2:0] |

512 |

EEA[11:3] |

8 |