- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

Асинхронный прием данных

УСАПП содержит блоки обнаружения данных и синхронизации для управления асинхронным приемом данных. Логика обнаружения синхронизации используется для синхронизации с внутренним генератором скорости связи для обеспечения возможности ввода последовательной посылки с выв. RxD. Логика обнаружения данных осуществляет выборку и фильтрацию (ФНЧ) каждого входящего бита данных, тем самым увеличивая помехоустойчивость приемника. Рабочий диапазон асинхронного приема определяется точностью встроенного генератора скорости связи, точностью скорости входящей посылки и размером посылки (количество бит).

Асинхронный поиск синхронизации

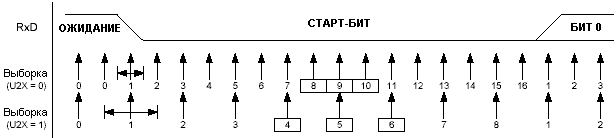

Логика обнаружения синхронизации синхронизирует во времени работу приемника с входящей последовательной посылкой. На рис. 83 иллюстрируется процесс поиска старт-бита во входящей посылке. Частота выборок в 16 раз выше скорости связи для нормального режима и 8 раз выше для режима удвоения скорости. Горизонтальные стрелки иллюстрируют возможный уход синхронизации в процессе выборки. Обратите внимание на более высокую разсинхронизацию во времени при использовании режима удвоения скорости (U2X = 1). Выборки, обозначенные номером 0, соответствуют состоянию ожидания на линии RxD (т.е. при неактивной связи).

Рисунок

83. Выборка старт-бита

Рисунок

83. Выборка старт-бита

Если логика обнаружения синхронизации определяет переход из высокого (состояние ожидания) к низкому (старт) состоянию на линии RxD, то инициируется последовательность действий по обнаружению старт-бита. Примем, что выборка 1 означает первая выборка с нулевым значением. Тогда по выборкам 8, 9, 10 в нормальном режиме и выборкам 4, 5, 6 в режиме удвоения скорости определяется действительность старт-бита (на рисунке эти выборки помещены в рамку). Если две или более из этих выборок имеют единичное состояние (принцип мажоритарного голосования), то старт-бит отклоняется как ложный, а приемник продолжит поиск следующего перехода из 1 в 0. Однако если определен действительный старт-бит, то логика обнаружения синхронизации оказывается засинхронизированной, после чего вступит в силу логика обнаружения данных. Процесс синхронизации повторяется для каждого старт-бита.

Асинхронный поиск данных

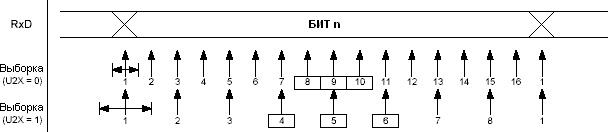

После обнаружения старт-бита начинает работу логика обнаружения данных. Блок обнаружения данных использует цифровой автомат с 16 состояниями в нормальном режиме работы и с 8 состояниями в режиме удвоения скорости. На рисунке 84 показана выборка бит данных и бита паритета. Для каждой выборки указан номер, который соответствует номеру состояния цифрового автомата блока обнаружения данных.

Рисунок

84. Выборка данных и бит паритета

Рисунок

84. Выборка данных и бит паритета

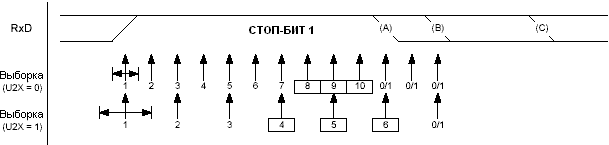

Определение логического уровня принимаемого бита данных происходит с помощью мажоритарного голосования по трем выборкам, расположенных по центру принятого бита. Центральные выборки выделены на рисунке путем размещения их в рамке. Процесс мажоритарного голосования состоит в следующем: если две или все три выборки имеют высокие уровни, то принятый бит фиксируется как лог. 1. Если две или три выборки имеют низкие уровни, то принятый бит фиксируется как лог. 0. Процесс мажоритарного голосования, по сути, представляет собой фильтр низких частот для входящего сигнала с вывода RxD. Процесс обнаружения повторяется до полного завершения приема посылки, в т.ч. первый стоп-бит. Обратите внимание, что приемник определяет только первый стоп-бит посылки, а второй игнорируется. На рисунке 85 отображен процесс выборки стоп-бита и начальный момент возможности обнаружения старт-бита следующей посылки.

Рисунок

85. Выборка стоп-бита и следующего

старт-бита

Рисунок

85. Выборка стоп-бита и следующего

старт-бита

Принцип мажоритарного голосования, рассмотренный на примере стоп-бита, аналогично распространяется и на другие биты в посылке. Если обнаруженный стоп-бит имеет нулевое значение, то устанавливается флаг ошибки посылки FE.

Новое изменение из 1 в 0 будет воспринято как стоп-бит новой посылки, если это изменение произошло после выборки последнего бита, используемого при мажоритарном голосовании. Для режима с нормальной скоростью первая выборка с низким уровнем может находится в позиции, обозначенной А на рисунке 85. Для режима удвоения скорости появление низкого уровня допускается позже (точка В). Точка C соответствует полному завершению передачи стоп-бита. Использование раннего обнаружения старт-бита влияет на рабочий диапазон приемника (допустимое расхождение частот при фиксированном формате посылки).

Рабочий диапазон асинхронной связи

Рабочий диапазон приемника зависит от расхождения между внутренне генерируемой скоростью связи и скоростью принимаемых бит. Если передатчик отправляет посылки на более высокой или более низкой скорости или внутренне-генерируемая скорость связи приемника не соответствует основной частоте (см. табл. 75), то приемник окажется неспособным засинхронизировать посылку по отношению к старт-биту.

Следующие выражения могут использоваться для вычисления отношения скорости принимаемых данных и внутренней скорости приемника:

где

D - сумма количества передаваемых бит данных и бит паритета, D = 5…10;

S - количество выборок в секунду. S = 16/8 в режиме нормальной/удвоенной скорости;

SF - Номер первой выборки используемой для мажоритарного голосования. SF = 8/4 в режиме нормальной/удвоенной скорости;

SM - Номер центральной выборки используемой при мажоритарном голосовании. SM = 9/5 в режиме нормальной/удвоенной скорости;

Rмин - отношение наименьшей скорости принимаемых данных к скорости приемника;

Rмакс - отношение набольшей скорости принимаемых данных к скорости приемника.

В таблицах 75 и 76 приведен список максимальных допустимых погрешностей при генерации скорости приемника. Обратите внимание, что режим нормальной скорости устойчив к более широким изменениям скорости связи.

Таблица 75. Рекомендуемая максимальная погрешность генерации скорости связи приемника в режиме нормальной скорости (U2X = 0)

D (кол. бит данных и паритета) |

Rмин, % |

Rмакс, % |

Общая макс. погрешность, % |

Рекомендуемая максимальная погрешность приемника, % |

5 |

93,20 |

106,67 |

+6.67/-6.8 |

± 3.0 |

6 |

94,12 |

105,79 |

+5.79/-5.88 |

± 2.5 |

7 |

94,81 |

105,11 |

+5.11/-5.19 |

± 2.0 |

8 |

95,36 |

104,58 |

+4.58/-4.54 |

± 2.0 |

9 |

95,81 |

104,14 |

+4.14/-4.19 |

± 1.5 |

10 |

96,17 |

103,78 |

+3.78/-3.83 |

± 1.5 |

Таблица 76. Рекомендуемая максимальная погрешность генерации скорости связи приемника в режиме удвоенной скорости (U2X = 1)

D (кол. бит данных и паритета) |

Rмин, % |

Rмакс, % |

Общая макс. погрешность, % |

Рекомендуемая максимальная погрешность приемника, % |

5 |

94,12 |

105,66 |

+5.66/-5.88 |

± 2.5 |

6 |

94,92 |

104,92 |

+4.92/-5.08 |

± 2.0 |

7 |

95,52 |

104,35 |

+4.35/-4.48 |

± 1.5 |

8 |

96,00 |

103,90 |

+3.90/-4.00 |

± 1.5 |

9 |

96,39 |

103,53 |

+3.53/-3.61 |

± 1.5 |

10 |

96,70 |

103,23 |

+3.23/-3.30 |

± 1.0 |

Рекомендуемая погрешность генератора скорости связи приемника была выбрана исходя из того, что передатчик и приемник в совокупности определяют общую максимальную погрешность. Имеется два возможных источника влияния на погрешность скорости связи приемника. Системная синхронизация (XTAL) приемника всегда имеет некоторую нестабильность в зависимости от напряжения питания и температуры. При использовании кварцевого резонатора для генерации системной синхронизации как правило не возникает проблем, но при использовании керамических резонаторов частота синхронизации может изменяться более чем на 2% в зависимости характеристик выбранного резонатора. Второй источник влияния на погрешность является более управляемым. Требуемую скорость связи не всегда удается получить путем деления частоты синхронизации на целое число. В этом случае необходимо выбрать такое значение UBRR, которое обеспечивает минимально возможную погрешность результирующей частоты.