- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

Генерация тактовых импульсов

Логика генерации тактовых импульсов формирует основную синхронизацию приемника и передатчика. УСАПП поддерживает четыре режима работы синхронизации: нормальная асинхронная, асинхронная с удвоением скорости, ведущая синхронная и подчиненная синхронная. Бит UMSEL в регистре С управления и статуса (UCSRC) позволяют выбрать асинхронную или синхронную работу. Удвоение скорости (только в асинхронном режиме) управляется битом U2X в регистре UCSRA. При использовании синхронного режима (UMSEL = 1) соответствующий бит в регистре направления данных для вывода XCK (DDR_XCK) задает будет ли синхронизация внутренней (ведущий режим) или внешней (подчиненный режим). Вывод XCK активен только при использовании синхронного режима.

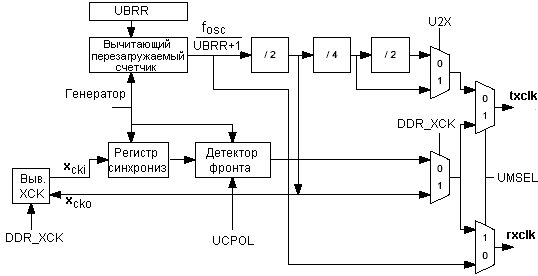

На рисунке 80 показана функциональная схема логики синхронизации.

Рисунок

80. Функциональная схема логики

синхронизации УСАПП

Рисунок

80. Функциональная схема логики

синхронизации УСАПП

Описание сигналов:

txclk - синхронизация передатчика (внутренний сигнал)

rxclk - основная синхронизация приемника (внутренний сигнал)

xcki - вход от вывода XCK (внутренний сигнал). Используется для синхронной подчиненной работы.

xcko - выход синхронизации к выводу XCK (внутренний сигнал). Используется в ведущем синхронном режиме.

fosc - вывод частоты XTAL (системная синхронизация).

Генерация внутренней синхронизации - генератор скорости связи

Внутренняя синхронизация используется для асинхронного и ведущего синхронного режимов работы. Описание в данном параграфе опирается на рис. 80.

Регистр генератора скорости связи (UBRR) и связанный с ним вычитающий счетчик функционируют как программируемый предделитель или генератор скорости связи. Вычитающий счетчик тактируется системной синхронизацией (fosc) и перезагружается значением из регистра UBRR всякий раз при достижении нулевого значения или после записи регистра UBRRL. Тактовый сигнал генерируется всякий раз при достижении счетчиком нулевого значения. Данный тактовый сигнал является тактовым выходом генератора скорости связи (= fosc/(UBRR+1)). Передатчик делит частоту генератора скорости связи на 2, 8 или 16 в зависимости от режима работы. Модули обнаружения синхронизации и данных приемника подключены непосредственно к тактовому выходу генератора скорости связи. Однако, цифровой автомат модулей обнаружения используют 2, 8 или 16 состояний в зависимости от режима, задаваемого битами UMSEL, U2X и DDR_XCK.

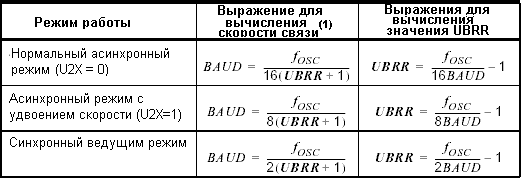

Таблица 74 содержит выражения для вычисления скорости связи (в битах в секунду) и вычисления значений UBRR для каждого из рабочих режимов при использовании внутренне генерируемого тактового источника.

Таблица 74. Выражения для вычисления установок регистра скорости связи

Прим. 1: Скорость связи представлена в битах в секунду (бод).

BAUD - скорость связи (в битах в секунду, бод)

fOSC - частота синхронизации системного генератора

UBRR - Содержимое регистров UBRRH и UBRRL, (0 … 4095)

Примеры значений UBRR для некоторых частот системной синхронизации представлены в таблице 82.

Работа с удвоением скорости связи (U2X)

Скорость передачи данных может быть удвоена, если установить бит U2X в регистре UCSRA. Установка данного бита оказывает действие только в асинхронном режиме. При использовании синхронного режима необходимо установить нулевое значение данного бита.

Установка данного бита приводит к уменьшению коэффициента деления частоты генератора скорости связи с 16 до 8, тем самым удваивая скорость асинхронной связи. Однако следует обратить внимание, что в этом случае приемник сокращает количество выборок с 16 до 8 при обнаружении синхронизации и данных, поэтому, при использовании данного режима необходимо использовать более точные установки скорости связи и более стабильный тактовый источник. Для передатчика удвоение скорости не связано с какими-либо ограничениями.

Внешняя синхронизация

Внешняя синхронизация используется в синхронном подчиненном режиме работы (см. рис. 80).

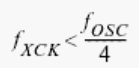

Во избежание возможности возникновения метастабильности вход внешней синхронизации с вывода XCK связан с регистром синхронизации. Выход регистра синхронизации проходит через детектор фронтов, а только затем используется приемником и передатчиком. На данный процесс затрачивается два такта синхронизации ЦПУ и, поэтому, максимальная частота внешней синхронизации на выводе XCK ограничивается следующим выражением:

Обратите внимание, что частота fosc зависит от стабильности системного источника синхронизации. В связи с этим рекомендуется учесть некоторый запас для предотвращения возможности потери данных из-за колебаний частоты.

Режим синхронной связи

Если используется режим синхронной связи (UMSEL = 1), то вывод XCK используется или как вход синхронизации (подчиненный режим) или как выход синхронизации (ведущий режим). Зависимость между тактовыми фронтами и выборкой данных или изменением данных одна и та же. Основной принцип работы заключается в том, что выборка вводимых данных (на RxD) осуществляется фронтом XCK, который противоположен фронту, по которому происходит изменение выходных данных (на TxD).

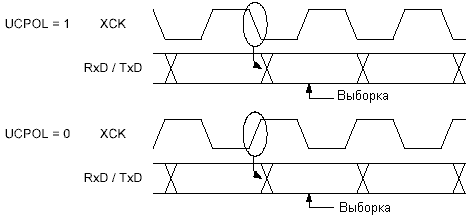

Рисунок

81. Временная диаграмма для синхронного

режима XCK

Рисунок

81. Временная диаграмма для синхронного

режима XCK

Бит UCPOL регистра UCRSC выбирает какой фронт XCK используется для выборки данных, а какой для изменения данных. На рисунке 81 показано, что при UCPOL=0 изменение данных происходит по нарастающему фронту XCK, а выборка по падающему фронту XCK. Если установлен бит UCPOL, то изменение данных происходит по падающему фронту XCK, а выборка по нарастающему фронту XCK.