- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

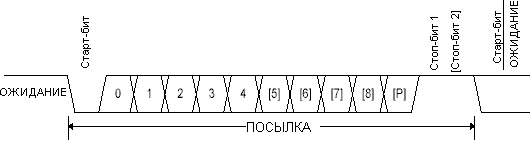

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

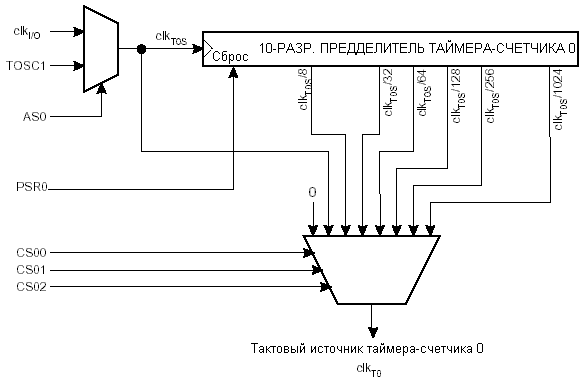

Предделитель таймера-счетчика 0

Рисунок

45. Предделитель таймер-счетчика 0

Рисунок

45. Предделитель таймер-счетчика 0

Тактовый источник таймера-счетчика 0 обозначен как clkT0. По умолчанию clkT0 подключен к системному источнику синхронизации ввода-вывода clkI/O. Путем установки бита AS0 в регистре ASSR таймер-счетчик 0 тактируется асинхронно с вывода TOSC1. Данная функция позволяет использовать таймер-счетчик 0 в качестве часов реального времени (RTC). Если AS=1, то выводы TOSC1 и TOSC2 более не выполняют функции линий порта С, а между ними может быть подключен кварцевый резонатор в качестве отдельного тактового источника таймера-счетчика 0. Генератор оптимизирован под использование кварца на частоту 32768 Гц. Подключение к выводу TOSC1 внешнего тактового источника не рекомендуется.

Предделитель таймера-счетчика 0 позволяет выбрать следующие тактовые сигналы: clkT0S/8, clkT0S/32, clkT0S/64, clkT0S/128, clkT0S/256 и clkT0S/1024. Кроме того, имеется возможность остановить синхронизацию. Установка бита PSR0 в регистре SFIOR сбрасывает предделитель. Данная функция позволяет программисту работать с более прогнозируемым поведением предделителя.

Регистр специальных функций ввода-вывода SFIOR

Разряд |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

TSM |

- |

- |

- |

ACME |

PUD |

PSR0 |

PSR321 |

SFIOR |

Чтение/запись |

Чт./Зп. |

Чт. |

Чт. |

Чт. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

|

Исх. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Разряд 7 - TSM: Режим синхронизации таймера-счетчика

Установка бита TSM активизирует режим синхронизации таймеров-счетчиков. В данном режиме после установки бита PSR0 или PSR321 соответствующий предделитель будет постоянно находиться в сброшенном состоянии. В этом состоянии гарантируется, что все соответствующие таймеры-счетчики будут остановлены и могут быть одинаково настроены без риска изменения состояния одного из них во время конфигурации. Если после этого сбросить бит TSM, то биты PSR0 и PSR321 сбрасываются аппаратно, а таймеры-счетчики начинают счет одновременно.

Разряд 1 - PSR0: Сброс предделителя таймера-счетчика 0

Если данный бит равен лог. 1, то предделитель таймера-счетчика 0 сбрасывается. Данный бит обычно сбрасывается аппаратно сразу после установки. Если данный бит устанавливается, когда таймер-счетчик 0 работает в асинхронном режиме, то он остается равным 1 пока не сбросится предделитель таймера-счетчика 0. Данный бит не сбрасывается аппаратно, если бит TSM=1.

УСАПП

Универсальный синхронный и асинхронный последовательный приемопередатчик (УСАПП) предназначен для организации гибкой последовательной связи.

Отличительные особенности:

Полнодуплексная работа (раздельные регистры последовательного приема и передачи)

Асинхронная или синхронная работа

Ведущее или подчиненное тактирование связи в синхронном режиме работы

Высокая разрешающая способность генератора скорости связи

Поддержка формата передаваемых данных с 5, 6, 7, 8 или 9 битами данных и 1 или 2 стоп-битами

Аппаратная генерация и проверка бита паритета (четность/нечетность)

Определение переполнения данных

Определение ошибки в структуре посылки

Фильтрация шума с детекцией ложного старт-бита и цифровым ФНЧ

Три раздельных прерывания по завершении передачи, освобождении регистра передаваемых данных и завершении приема

Режим многопроцессорной связи

Режим удвоения скорости связи в асинхронном режиме

Два УСАПП

ATmega128 содержит два УСАПП: УСАПП0 и УСАПП1. Описание функционирования обоих УСАПП приведено ниже. УСАПП0 и УСАПП1 имеют раздельные регистры ввода-вывода, что показано в "Сводной таблице регистров". Обратите внимание, что в режиме совместимости с ATmega103 УСАПП1 не доступен, а также нет регистров UBRR0H и UCRS0C. Это означает, что в режиме совместимости с ATmega103 поддерживается только асинхронная работа УСАПП0.

Краткий обзор

На рисунке 79 представлена упрощенная функциональная схема УСАПП. На рисунке жирным шрифтом выделены регистры и выводы УСАПП.

Рисунок

79. Функциональная схема УСАПП

Рисунок

79. Функциональная схема УСАПП

Прим. : Расположение выводов УСАПП см. на рисунке 1, табл. 76 и 39.

На рисунке 79 пунктирной линией выделены три основных блока УСАПП: тактовый генератор, передатчик и приемник. Регистры управления используются всеми блоками. Логика тактового генератора состоит из логики синхронизации, связанной с внешним тактовым входом (используется в подчиненном режиме) и генератора скорости связи. Вывод XCK (синхронизация передачи) используется только в режиме синхронной передачи. Передатчик состоит из одного буфера записи, последовательного сдвигового регистра, генератора паритета и управляющей логики, которая поддерживает различные форматы последовательной посылки. Буфер записи позволяет непрерывно передавать данные без каких-либо задержек между передачей посылок. Приемник является более сложным блоком УСАПП, т.к. в его состав входят модули обнаружения данных и синхронизации. Модули обнаружения необходимы для асинхронного приема данных. Помимо модулей обнаружения в приемник входит устройство проверки паритета, сдвиговый регистр, и двухуровневый приемный буфер (UDR). Приемник поддерживает те же последовательные форматы, что и передатчик, и может определить ошибку в посылке (кадре), переполнение данных и ошибку паритета.

Совместимость УСАПП с УАПП других AVR-микроконтроллеров

УСАПП полностью совместим с УАПП AVR-микроконтроллеров по следующим позициям:

Расположение бит внутри всех регистров УСАПП

Генерация скорости связи

Работа передатчика

Функционирование буфера передатчика

Работа приемника

Однако в схеме буферизации приемника реализовано два улучшения, которые в некоторых случаях может повлиять на совместимость:

Добавлен второй буферный регистр. Два буферных регистра работают как циклический буфер FIFO. Поэтому, UDR необходимо опрашивать только один раз при каждом получении данных! Более важным является тот факт, что флаги ошибок (FE и DOR), а также 9-ый бит данных (RXB8) также буферизованы вместе с данными в приемном буфере. Поэтому, состояние статусных бит необходимо всегда считывать перед чтением регистра UDR. В противном случае состояние флагов ошибок будет потеряно, т.к. будет изменено состояние буфера.

Сдвиговый регистр приемника действует как трехуровневый буфер. Этим обеспечивается возможность сохранения принятых данных в последовательном сдвиговом регистре (см. рисунок 79) до определения нового старт-бита, если буферные регистры заполнены. Таким образом, УСАПП характеризуется более высокой стойкостью к выполнению условия ошибки по переполнению данных (DOR).

У следующих управляющих битах изменены наименования, но сохранены назначение, механизм действия и расположение в регистре:

CHR9 заменен на UCSZ2

OR заменен на DOR