- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

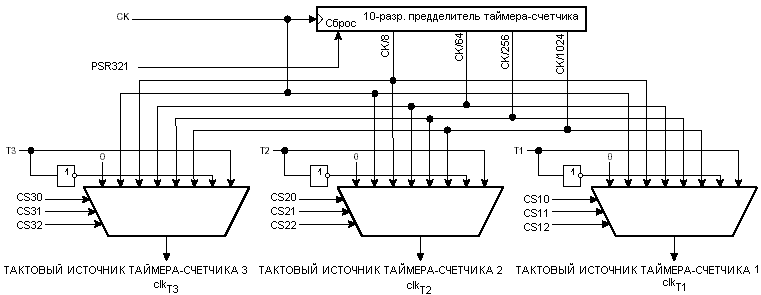

Предделители таймеров-счетчиков 1, 2 и 3

Таймеры-счетчики 1, 2 и 3 используют один и тот же модуль предделителя, но могут использовать различные установки предварительного деления. Приведенное ниже описание распространяется на все упомянутые таймеры.

Внутренний тактовый источник

Тактовый вход таймера-счетчика может быть непосредственно связан с системной синхронизацией, если установить CSn2:0 = 1. В данном случае достигается максимально быстрая работа таймера-счетчика на системной частоте fCLK_I/O. Альтернативно четыре производных тактовых сигнала на выходе предделителя могут использоваться в качестве тактового источника. Поделенный тактовый сигнал имеет частоту fCLK_I/O/8, fCLK_I/O/64, fCLK_I/O/256 или fCLK_I/O/1024.

Сброс предделителя

Предделитель является самым простым нереверсивным счетчиком, т.е. работает независимо от логики выбора синхронизации таймера-счетчика и является общим для таймеров 1, 2 и 3. Поскольку логика выбора синхронизации не влияет на таймер-счетчик, то в случае использования предделителя его состояние будет неопределенным. Как пример можно привести неопределенность, которая возникает после разрешения работы таймера, тактируемого через предделитель с настройкой (6 > CSn2:0 > 1). Количество системных тактов с момента разрешения работы таймера до возникновения первого счетного импульса может быть от 1 до N+1, где N – коэффициент деления предделителя (8, 64, 256 или 1024).

Имеется возможность выполнить программный сброс предделителя для синхронизации его работы с таймером. Однако следует учитывать возможность негативного влияния на работу остальных таймеров, которые используют этот же предделитель. Внешний тактовый источник

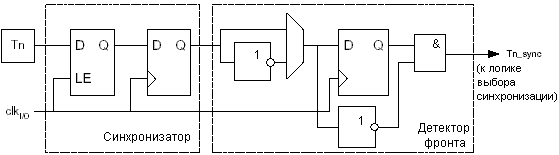

Внешний сигнал, подключенный к выводу Tn, может использоваться как тактовый для таймеров-счетчиков (clkT1/clkT2/clkT3). Вывод Tn опрашивается каждый такт системной синхронизации логикой синхронизации данного вывода. Считанный таким образом сигнал проходит через детектор фронта. На рисунке 59 представлена функциональная схема синхронизации Tn и логики детектора фронта. Регистры тактируются положительным фронтом внутренней системной синхронизации (clkI/O). Детектор фронта генерирует один тактовый импульс clkT1/clkT2/clkT3 при определении положительного (CSn2:0 = 7) или отрицательного (CSn2:0 = 6) фронта.

Рисунок

59 – Функциональная схема синхронизатора

и детектора фронта вывода Tn

Рисунок

59 – Функциональная схема синхронизатора

и детектора фронта вывода Tn

Работа логики синхронизатора и детектора фронта связана с задержкой исходного фронта на выводе Tn на 2.5…3.5 такта системной синхронизации до появления счетного импульса.

Разрешение и запрет тактового входа необходимо выполнять, когда Tn находится в устойчивом состоянии в течение не менее одного такта системной синхронизации, иначе имеется риск генерации ложного тактового импульса синхронизации таймера-счетчика.

Для корректной работы логики преобразования каждый полупериод внешнего тактового сигнала должен быть больше одного периода системной синхронизации. Таким образом, внешний тактовый сигнал должен быть меандром (скважность 2) с частотой минимум вдвое меньшей системной (fExtClk < fclk_I/O/2). Т.к. детектор фронта использует преобразование, то максимальная частота, которую он может определить, равна половине частоты преобразования (теорема преобразования Найквиста). Однако, вследствие изменения частоты системной синхронизации и скважности, вызванных погрешностями тактового генератора (погрешности кварцевого резонатора, керамического резонатора или конденсаторов) рекомендуется, чтобы максимальная частота внешнего тактового сигнала была не более fclk_I/O/2.5.

Частота внешнего тактового сигнала не может быть поделена внутренним предделителем.

Рисунок

60 – Предделитель таймеров-счетчиков

1, 2 и 3

Рисунок

60 – Предделитель таймеров-счетчиков

1, 2 и 3

Прим.: логика синхронизации на входах T3/T2/T1 показана на рисунке 59.

Регистр специальных функций ввода-вывода – SFIOR

Разряд |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

TSM |

- |

- |

- |

ACME |

PUD |

PSR0 |

PSR321 |

SFIOR |

Чтение/запись |

Чт./Зп. |

Чт. |

Чт. |

Чт. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

|

Исх. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Разряд 7 – TSM: Режим синхронизации таймеров-счетчиков

Запись в данный бит лог. 1 активизирует режим синхронизации таймеров-счетчиков. В этом режиме запоминаются значения, записанные в биты PSR0 и PSR321, следовательно, запоминаются состояния соответствующих сигналов сброса предделителей. Этим гарантируется, что все соответствующие таймеры будут остановлены и им можно присвоить одинаковые значения без опасности их модификации в процессе конфигурации. Если в бит TSM записать лог. 0, то биты PSR0 и PSR321 сбросятся аппаратно и таймеры-счетчики начнут счет одновременно.

Разряд 0 – PSR321: Сброс предделителя таймеров-счетчиков 1, 2 и 3

Если данный бит равен лог. 1, то предделитель таймеров-счетчиков 1, 2 и 3 будет сброшен. Данный бит обычно сразу сбрасывается аппаратно за исключением, когда установлен бит TSM. Обратите внимание, что таймеры-счетчики 1, 2 и 3 используют один и тот же предделитель и сброс этого предделителя оказывает влияние на все три таймера.