- •ATmega128, aTmega128l - 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

- •Усапп …………………………………………………………………………………………………..168

- •Ядро центрального процессорного устройства avr

- •Интерфейс внешней памяти

- •Системная синхронизация и тактовые источники

- •Внешняя синхронизация

- •Управление энергопотреблением и режимы сна

- •Режим холостого хода (Idle)

- •Режим уменьшения шумов ацп (adc Noise Reduction)

- •Режим выключения (Power-down)

- •Экономичный режим (Power-save)

- •Дежурный режим (Standby)

- •Расширенный дежурный режим (Extended Standby)

- •Минимизация потребляемой мощности

- •Системное управление и сброс

- •Прерывания

- •Векторы прерываний в aTmega128

- •Порты ввода-вывода

- •Порты в качестве универсального цифрового ввода-вывода

- •Альтернативные функции порта

- •Int0/scl – порт d, разряд 0

- •Описание регистров портов ввода-вывода

- •Внешние прерывания

- •Аналоговый компаратор

- •Введение

- •Доступ к 16-разр. Регистрам

- •Тактовые источники таймера-счетчика 1/3

- •Блок счетчика

- •Блок захвата

- •Блоки сравнения

- •Блок формирования выходного сигнала

- •Режимы работы

- •Временные диаграммы 16-разр. Таймеров-счетчиков

- •Описание регистров 16-разр. Таймеров-счетчиков

- •Предделители таймеров-счетчиков 1, 2 и 3

- •Аналогово-цифровой преобразователь

- •Интерфейс jtag и встроенная отладочная система

- •Модулятор выходов таймеров (ocm1c2)

- •Последовательный периферийный интерфейс - spi

- •Функционирование вывода ss

- •Блок формирования выходного сигнала

- •Временные диаграммы таймера-счетчика 0

- •Описание регистров 8-разрядного таймера-счетчика 0

- •Асинхронная работа таймера-счетчика 0

- •Предделитель таймера-счетчика 0

- •Генерация тактовых импульсов

- •Форматы посылки

- •Инициализация усапп

- •Передача данных - Передатчик усапп

- •Прием данных - Приемник усапп

- •Асинхронный прием данных

- •Многопроцессорный режим связи

- •Описание регистров усапп

- •Примеры установок скоростей связи

- •Двухпроводной последовательный интерфейс twi

- •Формат посылки и передаваемых данных

- •Системы многомастерных шин, арбитраж и синхронизация

- •Обзор модуля twi

- •Описание регистров twi

- •Рекомендации по использованию twi

- •Режимы передачи

- •Программирование памяти

- •Параллельное программирование

- •Последовательное программирование

- •Программирование через интерфейс jtag

- •Электрические характеристики

- •Требования к характеристикам внешнего тактового сигнала

- •Характеристики двухпроводного последовательного интерфейса

- •Характеристики временной диаграммы spi

- •Предварительные данные по характеристикам ацп

- •Временная диаграмма внешней памяти данных

- •Типовые характеристики aTmega128: предварительные данные

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Типовые характеристики aTmega128: предварительные данные (продолжение)

- •Сводная таблица регистров

- •Набор инструкций

- •Информация для заказа

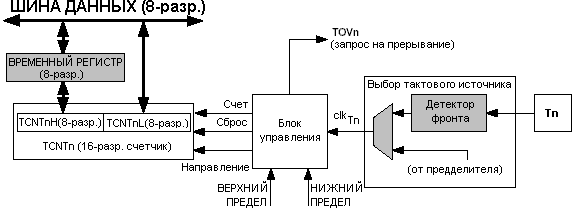

Тактовые источники таймера-счетчика 1/3

Таймер-счетчик может использовать как внешний, так и внутренний тактовые сигналы. Источник тактового сигнала выбирается соответствующей схемой микроконтроллера под управлением бит выбора синхронизации (CSn2:0), которые находятся в регистре В управления таймером-счетчиком (TCCRnB). Более подробная информация по тактовым источникам и предделителю приведена в разделе "Предделители таймера-счетчика 3, таймера-счетчика 2 и таймера-счетчика 1".

Блок счетчика

Основным элементом 16-разр. таймера-счетчика является программируемый реверсивный 16-разрядный счетчик. На рисунке 47 представлена функциональная схема счетчика и окружающих его элементов.

Рисунок

47 – Функциональная схема счетчика

Рисунок

47 – Функциональная схема счетчика

Описание внутренних сигналов:

Счет – Инкрементирует или декрементирует состояние TCNTn на 1.

Направление – Задает прямой счет (инкрементирование) или обратный счет (декрементирование).

Сброс – Сброс TCNTn (установка всех разрядов к лог. 0).

clkTn – Синхронизация таймера-счетчика.

Верхний предел – Сигнализирует о достижении TCNTn максимального значения.

Нижний предел – Сигнализирует о достижении TCNTn минимального значения (нуля).

Содержимое 16-разр. счетчика разбито на две 8-разр. ячейки, расположенных в памяти ввода-вывода: Старший байт счетчика (TCNTnH) , в котором хранятся старшие 8-разрядов счетчика, и младший байт счетчика (TCNTnL), в котором хранятся младшие 8-разрядов. ЦПУ не имеет непосредственного доступа к регистру TCNTnH. Если ЦПУ выполняет доступ к TCNTnH, то фактически обращение происходит к временному регистру. Во временный регистр копируется значение TCNTnH, если выполняется чтение регистра TCNTnL и в TCNTnH копируется содержимое временного регистра, если выполняется запись в TCNTnL. Такой механизм реализован для считывания/записи 16-разр. значения счетчика за один такт ЦПУ в условиях 8-разр. шины данных. Следует обратить внимание, что в некоторых случаях запись в регистр TCNTn во время счета счетчиком будет давать непредсказуемый результат. Такие случаи описаны в последующих параграфах.

В зависимости от используемого режима работы каждый такт синхронизации таймера clkTn счетчик будет сбрасываться, инкрементироваться или декрементироваться. Сигнал clkTn может быть внешним или внутренним, что задается битами выбора синхронизации (CSn2:0). Если тактовый источник не задан (CSn2:0 = 0), то таймер останавливается. Однако содержимое TCNTn остается доступным ЦПУ независимо от наличия синхронизации на clkTn. Если ЦПУ выполняет запись в TCNTn, то тем самым блокируется (запись имеет более высокий приоритет) любое действие счетчика: сброс или счет.

Алгоритм счета определяется значением бит режима работы таймера (WGMn3:0), расположенных в регистрах А и В управления таймером-счетчиком (TCCRnA и TCCRnB). Имеется четкая связь между алгоритмом счета счетчика и формой генерируемого на выходе OCnx сигнала. Боле подробная информация об этом приведена в “Режимы работы 16-разр. таймеров-счетчиков”.

Установка флага переполнения таймера-счетчика (TOVn) происходит в зависимости выбранного с помощью бит WGMn3:0 режима работы. Флаг TOVn может использоваться для генерации прерывания ЦПУ.