- •1. Элементы алгебры логики. Введение

- •1.1. Основные понятия алгебры логики.

- •1.2. Операции алгебры логики.

- •1.2.1. Инверсия (логическое отрицание).

- •1.2.2. Конъюнкция (логическое умножение).

- •1.2.3. Дизъюнкция (логическое сложение).

- •1.2.4. Операция Шеффера («и-не»).

- •1.2.5. Операция Пирса («или-не»).

- •1.2.6. Операция сложения по модулю два.

- •1.3.5. Законы (формулы) поглощения.

- •1.3.6. Законы (формулы) склеивания.

- •2. Цифровые интегральные микросхемы.

- •2.1. Параметры цифровых микросхем.

- •2.2. Микросхемы ттл-логики.

- •2.3. Дешифраторы, шифраторы.

- •2.3. Сумматоры и вычитатели.

- •2.4. Мультиплексоры. Демультиплексоры.

- •2.5.Узлы перекосов.

- •2.6.Триггеры.

- •2.6.1. Назначение и классификация триггерных устройств.

- •2.6.3. Асинхронный rs-тригтер с инверсными входами.

- •2.6.4. Синхронный rs-триггер.

- •2.7. Регистры и счетчики.

- •2.8. Регистры.

- •2.8.Двоичные счетчики.

- •3. Классификация интегральных микросхем.

- •Заключение

- •Элементы алгебры логики.

2.2. Микросхемы ттл-логики.

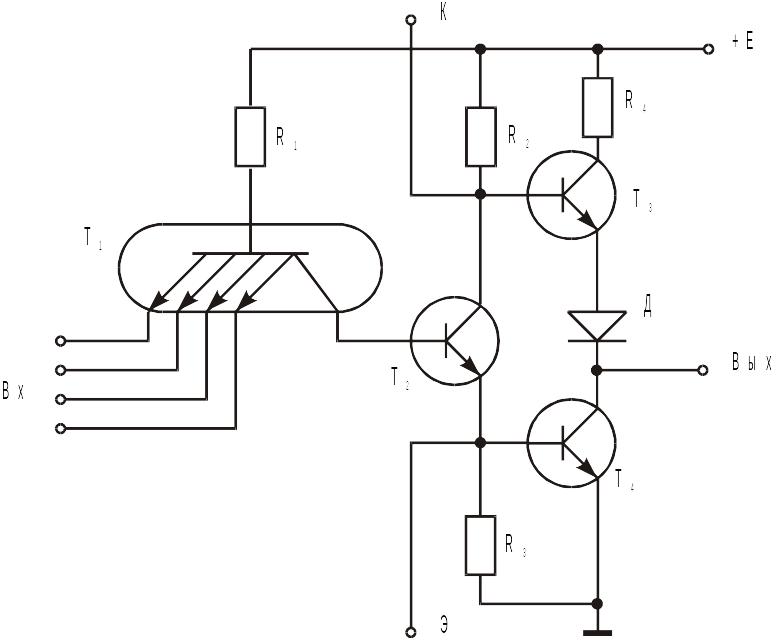

Принцип построения базового элемента: транзисторно-транзисторная логика (ТТЛ). Базовые элементы ТТЛ строятся на основе многоэмиттерного транзистора, выполняющего роль логической схемы, и сложного инвертора. Число вариантов построения элементов ТТЛ велико. Один из вариантов построения элементов рассматриваемого типа приведен на рис. 4.

Рис. 4. Базовый элемент ТТЛ.

Элемент ТТЛ работает следующим образом. Когда на все входы многоэмитторного транзистора Т1 подан сигнал логической «1» все эмиттерные переходы входного транзистора (Т1) закрыты, ток от источника +Е через резистор R1 и открытый коллекторный переход транзистора Т1 поступает на базу транзистора Т2. Транзистор Т2 открывается. Ток, протекающий через открытый транзистор Т2 по цепи: «+» источника питания (+Е), резистор R2, коллектор-эмиттер открытого транзистора Т2, резистор R3, корпус, создает на резисторе R3 падение напряжения, под действием которого транзистор Т4 открывается, обеспечивая низкий уровень выходного напряжения (напряжение коллектора открытого транзистора Т4). Транзистор Т3 - закрыт, так как напряжение коллектора открытого транзистора Т2 мало. Диод Д служит для повышения порога открывания транзистора Т3.

При наличии хотя бы на одном входе сигнала «0» открывается соответствующий эмиттерный переход входного транзистора Т1, и ток от источника +Е через открытый переход поступает в выходную цепь источника сигнала «0». Напряжение на коллекторе Т1 (базе Т2) уменьшается, транзистор Т2 закрывается, напряжение на эмиттере Т2 уменьшается, что приводит к закрыванию транзистора Т4, а напряжение на коллекторе Т2 увеличивается, что приводит к отпиранию транзистора Т3. В результате на выходе обеспечивается уровень «1». Таким образом, рассмотренный элемент выполняет логическую функцию «И-НЕ». Резистор R4 предназначен для ограничения тока через открытый транзистор Т3 при коротком замыкании выхода. Благодаря применению сложного инвертора (Т2, Т3, Т4, Д) рассмотренный элемент ТТЛ имеет малое выходное сопротивление и в состоянии «1» и в состоянии «0», что позволяет увеличивать ток, отдаваемый в нагрузку, то есть повысить нагрузочную способность.

2.3. Дешифраторы, шифраторы.

Дешифраторы — это логические цепи со многими выходами, предназначенные для перевода двоичного (двоично-десятичного и т. п.) когда в единичный позиционный код. На каждом из выходов сигнал равен единице (или нулю) только при определенном сочетании входных сигналов. В общем случае полный дешифратор имеет п входов и 2n выходов.

Одноступенчатый, или линейный, дешифратор представляет собой набор цепей «И», входы и выходы которых являются соответственно входами и выходами дешифратора.

Двухступенчатые дешифраторы состоят из дешифраторов первой ступени, воспринимающих непосредственно входные сигналы, и дешифраторов второй ступени, на входы которых подаются сигналы с выходов дешифраторов первой ступени (а также могут подаваться и сами входные сигналы).

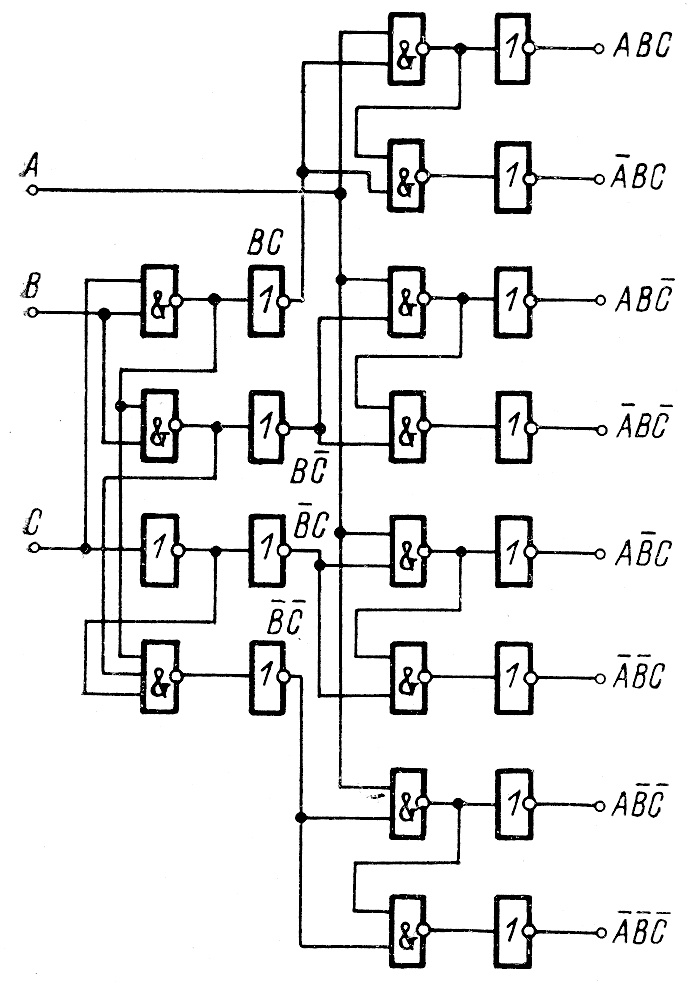

На рис. 46 показан двухступенчатый полный дешифратор на 3 входа и 8 выходов. Первая ступень в нем состоит из одного дешифратора, воспринимающего сигналы В и С. На входы дешифратора второй ступени поданы как выходные сигналы дешифратора первой ступени, так и входной сигнал А.

Двухступенчатый дешифратор n ≥ 4 входных переменных целесообразно выполнять с двумя дешифраторами первой ступени, один из которых воспринимает т входных сигналов, а второй п-т входных сигналов, причем т = п/2. В этом случае дешифратор второй ступени представляет собой набор из 2n двухвхо-довых ячеек «И».

В общем случае дешифраторы могут иметь и больше двух ступеней. Наибольшее возможное количество ступеней n-входового дешифратора равно п-1. Именно столько ступеней имеет пирамидальный дешифратор. В частности, дешифратор рис. 46 является пирамидальным. Сравнение дешифраторов может быть произведено по количеству входов всех цепей «И», составляющих дешифратор (каждая цепь «И», естественно, может включать в себя несколько ячеек «НЕ-И» или «НЕ-ИЛИ»), Линейный (одноступенчатый) дешифратор требует для своего построения 2п ячеек «И», каждая из которых должна иметь п входов. Следовательно, общее количество входов в этом случае будет N1 = n-2n.

Двухступенчатый дешифратор, состоящий из двух линейных дешифраторов первой ступени (на один из которых подано т, а на другой п-т выходных сигналов) и линейного дешифратора второй ступени, состоит из схем «И», имеющих следующее суммарное количество входов:

![]()

В этом соотношении предполагается, что m > 1 и (п-m) > 1. Если же один из двух дешифраторов первой ступени отсутствует (т = 1 или п-т = 1), то соответствующий член полученного соотношения опускается.

Для пирамидального дешифратора, содержащего п-1 линейных дешифраторов, построенных на основе двухвходовых ячеек «И», общее количество входов Nn-1 всех ячеек «И» можно определить по следующей формуле:

![]()

Ниже приведена табл. 2.3, в которой показано количество входов цепей «И», необходимых для построения линейных, двухступенчатых и пирамидальных дешифраторов различной сложности.

Из таблицы видно, что при количестве входов 2…3 целесообразно строить линейный дешифратор, а при 4 и более входах более экономичным является двухступенчатый дешифратор.

Рис. 5. Двухступенчатый дешифратор на 3 входа и 8 выходов.

Таблица 2.3

-

Число входов

дешифратора

Число выходов

дешифратора

Число входов цепей «И»

линейный дешифратор

двухступенчатый дешифратор

пирамидальный дешифратор

2

3

4

5

6

7

8

4

8

16

32

64

128

256

8

24

64

160

384

896

204

8

24

48

96

176

344

640

8

24

56

120

248

504

1016