Регистр (цифровая техника)

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств.

Основой построения регистров являются D-триггеры, RS-триггеры.

Операции в регистрах

Типичными являются следующие операции:

приём слова в регистр;

передача слова из регистра;

поразрядные логические операции;

сдвиг слова влево или вправо на заданное число разрядов;

преобразование последовательного кода слова в параллельный и обратно;

установка регистра в начальное состояние (сброс).

Классификация регистров

Регистры классифицируются[1] по следующим видам:

накопительные (регистры памяти, хранения)[2][3];

сдвигающие[4][5][6][7][8][9][10][11][12][13][14].

В свою очередь сдвигающие регистры делятся:

по способу ввода-вывода информации:

параллельные - запись и считывание информации происходит одновременно на все входы и со всех выходов[15];

последовательные - запись и считывание информации происходит в первый триггер, а та информация, которая была в этом триггере, перезаписывается в следующий - то же самое происходит и с остальными триггерами[16][17];

комбинированные;

по направлению передачи информации:

однонаправленные;

реверсивные[18][19].

по основанию системы счисления

двоичные

троичные

десятичные

Типы регистров

Регистры различают по типу ввода (загрузки, приёма) и вывода (выгрузки, выдачи) информации:

С последовательным вводом и выводом информации

С параллельным вводом и выводом информации

С параллельным вводом и последовательным выводом. Например: SN74LS165J(N), SN74166J(N), SN74LS166J(N)

С последовательным вводом и параллельным выводом. Например: SN7416J(N), SN74LS164J(N), SN74LS322J(N), SN74LS673J(N)

Использование триггеров с защёлками с тремя состояниями на выходе, увеличенная (по сравнению со стандартными микросхемами серии) нагрузочная способность позволяют использовать (в микропроцессорных системах с магистральной организацией) регистры непосредственно на магистраль в качестве регистров, буферных регистров, регистров ввода-вывода, магистрального передатчика и т. д. без дополнительных схем интерфейса.

Параллельные регистры

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления. Пример схемы статического регистра, построенного на триггерах типа D с прямыми динамическими входами, имеющего входы сброса и выходы с третьим состоянием, управляемые сигналом EZ.

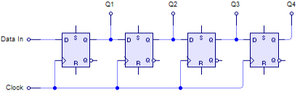

Сдвигающие (последовательные) регистры

Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала. В однотактных регистрах со сдвигом на один разряд вправо слово сдвигается при поступлении синхросигнала. Вход и выход последовательные (англ. Data Serial Right, DSR).

Согласно требованиям синхронизации в сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры могут за время действия разрешающего уровня синхросигнала переключиться неоднократно, что недопустимо. Появление в межразрядных связях логических элементов, и тем более, логических схем неединичной глубины упрощает выполнение условий работоспособности регистров и расширяет спектр типов триггеров, пригодных для этих схем. Многотактные сдвигающие регистры управляются несколькими синхропоследовательностями. Из их числа наиболее известны двухтактные с основным и дополнительным регистрами, построенными на простых одноступенчатых триггерах, управляемых уровнем. По такту С1 содержимое основного регистра переписывается в дополнительный, а по такту С2 возвращается в основной, но уже в соседние разряды, что соответствует сдвигу слова. По затратам оборудования и быстродействию этот вариант близок к однотактному регистру с двухступенчатыми триггерами.

Примеры:

SN74ALS164 (КР1533ИР8) — восьмиразрядный сдвиговый регистр с последовательной загрузкой и параллельной выгрузкой. Оснащён двумя входами, A и B, что позволяет заперев один из них (установив на нём низкий уровень напряжения по положительному фронту тактового импульса), осуществлять ввод данных в последовательном коде по другому входу.

SN74ALS165 (КР1533ИР9), SN74ALS166 (КР1533ИР10) — восьмиразрядный сдвиговый регистр с последовательной выгрузкой, работающий в двух режимах: параллельной загрузки и сдвига,

SN74198 (КР1533ИР13) — восьмиразрядный реверсивный сдвиговый регистр, имеющий четыре режима работы: параллельная загрузка, сдвиг влево, сдвиг вправо и блокировка.

SN74LS295 (КР1533ИР16) — четырёхразрядный реверсивный сдвиговый регистр с тремя состояниями выходов, имеющий четыре режима работы: параллельная загрузка, сдвиг влево, сдвиг вправо и блокировка.

Регистры процессора

Основная статья: Регистры процессора

По назначению регистры процессора различаются на:

аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода;

флаговые — хранят признаки результатов арифметических и логических операций;

общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса;

индексные — хранят индексы исходных и целевых элементов массива;

указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стэка);

сегментные — хранят адреса и селекторы сегментов памяти;

управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.

Троичные регистры

Основная статья: Троичный компьютер#Узлы троичных ЭВМ

Троичные регистры строятся на троичных триггерах. Как и троичные триггеры, троичные регистры могут быть разных троичных систем кодирования троичных данных (троичных разрядов): трёхуровневая однопроводная, двухуровневая двухразрядная двухпроводная, двухуровневая трёхразрядная одноединичная трёхпроводная, двухуровневая трёхразрядная однонулевая трёхпроводная и др. Троичные трёхразрядные одноединичные N-разрядные регистры данных описаны в .

На

рисунке справа приведена схема

девятиразрядного параллельного

статического стробируемого троичного

регистра данных на трёх трёхразрядных

параллельных статических стробируемых

троичных регистрах данных в трёхбитной

одноединичной системе троичных логических

элементов (линии с обозначением "3В"

- трёхпроводные), имеющего ёмкость в

показательной позиционной троичной

системе счисления ![]() чисел

(кодов).

чисел

(кодов).

Регистр процессора — блок ячеек памяти, образующий сверхбыструю оперативную память (СОЗУ) внутри процессора; используется самим процессором и большой частью недоступен программисту: например, при выборке из памяти очередной команды она помещается в регистр команд (англ.), к которому программист обратиться не может.

Имеются также регистры, которые в принципе программно доступны, но обращение к ним осуществляется из программ операционной системы, например, управляющие регистры и теневые регистры дескрипторов сегментов. Этими регистрами пользуются в основном разработчики операционных систем.

Существуют также так называемые регистры общего назначения (РОН), представляющие собой часть регистров процессора, использующихся без ограничения в арифметических операциях, но имеющие определенные ограничения, например в строковых. РОН, не характерные для эпохи мейнфреймов типа IBM/370[1] стали популярными в микропроцессорах архитектуры X86 — i8085, i8086 и последующих[2].

Специальные регистры[3] содержат данные, необходимые для работы процессора — смещения базовых таблиц, уровни доступа и т. д.

Часть специальных регистров принадлежит устройству управления, которое управляет процессором путём генерации последовательности микрокоманд.

Доступ к значениям, хранящимся в регистрах, как правило, в несколько раз быстрее, чем доступ к ячейкам оперативной памяти (даже если кеш-память содержит нужные данные), но объём оперативной памяти намного превосходит суммарный объём регистров (объём среднего модуля оперативной памяти сегодня составляет 1-4 Гб[4], суммарная «ёмкость» регистров общего назначения/данных для процессора Intel 80386 и более новых 32 битов * 8 = 256 бит).

Счётчик команд

IP

IP (англ. Instruction Pointer) — регистр, содержащий адрес-смещение следующей команды, подлежащей исполнению, относительно кодового сегмента CS в процессорах семействаx86.

Регистр IP связан с CS в виде CS:IP, где CS является текущим кодовым сегментом, а IP — текущим смещением относительно этого сегмента.

Регистр IP является 16-разрядным регистром-указателем. Кроме него, в состав регистров этого типа входят SP (англ. Stack Pointer — указатель стека) и BP (англ. Base Pointer — базовый указатель).

Принцип работы

Например, CS содержит значение 2CB5[0]H, в регистре IP хранится смещение 123H.

Адрес следующей инструкции, подлежащей исполнению, вычисляется путем суммирования адреса в CS (сегменте кода) со смещением в регистре IP:

2CB50H + 123H = 2CC73H

Таким образом, адрес следующей инструкции для исполнения равен 2CC73H.

При выполнении текущей инструкции процессор автоматически изменяет значение в регистре IP, в результате чего регистровая пара CS:IP всегда указывает на следующую подлежащую исполнению инструкцию.

EIP

Начиная с процессора 80386 была введена 32-разрядная версия регистра-указателя — EIP (англ. Instruction Pointer). В данном случае IP является младшей частью этого регистра (первые 16 разрядов). Принцип работы EIP в целом схож с работой регистра IP. Основная разница состоит в том, что в защищённом режиме, в отличие от реального режима, регистр CS является селектором (селектор указывает не на сам сегмент в памяти, а на его дескриптор сегмента в таблице дескрипторов).

RIP

В 64-разрядных процессорах используется свой регистр-указатель инструкций — RIP.

Младшей частью этого регистра является регистр EIP.

На основе RIP в 64-разрядных процессорах введён новый метод адресации RIP-relative. В остальном работа RIP аналогична работе регистра EIP.

Триггер

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно биполярные и полевые транзисторы), в прошлом — электромагнитные реле,электронные лампы. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС). Используются, в основном, в вычислительной технике для организации компонентов вычислительных систем: регистров, счётчиков,процессоров, ОЗУ.