Режим прямого доступа к памяти

Многие МС имеют в своем составе ВУ с высокой скоростью передачи больших массивов информации (например, накопители на гибких магнитных дисках). В этом случае обмен данными с ВУ организуется в режиме прямого доступа к памяти (ПДП). Суть режима заключается в том, чтобы осуществить обмен информацией между ВУ и памятью МС, минуя микропроцессор. Для организации режима ПДП в МП предусмотрен диалоговый обмен управляющими сигналами между ВУ и МП.

Когда ВУ инициирует запрос на ПДП, микропроцессор приостанавливает выполнение основной программы и переводит буферы шин адреса и данных в высокоимпедансное состояние, практически означающее отключение шин ША и ШД от микропроцессора. Шинами начинает управлять контроллер ПДП, организуя обмен данными между ВУ и памятью МС.

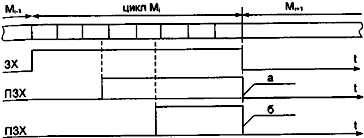

Инициирование ПДП осуществляет контроллер установкой на выводе ЗХ микропроцессора сигнала высокого уровня. В наиболее простом варианте обмена данными высокий уровень сигнала ЗХ сохраняется до окончания передачи массива данных. Все это время текущий машинный цикл после прохождения всех тактов находится в режиме ожидания окончания ПДП. Об окончании обмена контроллер ПДП сообщает снятием сигнала ЗХ, после чего начинается выполнение цикла М1 очередной команды. Но в режиме ПДП может осуществляться и передача в память МС и отдельных байтов информации. МП реагирует на высокий уровень сигнала ЗХ в текущем машинном цикле, если этот уровень стабилизировался за 180 не до нарастающего фронта Ф2 (рис. 4).

Рис. 4 - Режим прямого доступа к памяти

Напомним, что в такте Т1 цикла М1 МП только указал на ША адрес ячейки памяти или внешнего регистра, но обмен данными производится только в такте ТЗ. Поэтому разрешение ПДП сигналом ПЗХ и отключение ША и ШД возможно только в такте ТЗ (рис. 4, а), после чего МП переходит в режим ожидания окончания ПДП. Если же в текущем машинном цикле используются такты Т4 и Т5, то формирование сигнала ПЗХ происходит в такте Т5. После окончания ПДП микропроцессор всегда вводит такт Т1 следующего машинного цикла. В качестве контроллера, организующего обмен данными в режиме ПДП, в МПК К580 имеется контроллер ПДП КР580ВТ57.

Режим останова

Как указывалось, МП работает в циклическом режиме, когда после выполнения команды МП инициирует цикл М1 — чтение кода операции очередной команды. Остановить естественный процесс функционирования возможно специальной командой останова HLT, которая выполняется за четыре такта следующем образом.

В машинном цикле М1, состоящем из четырех тактов Т1-нТ4, производятся выборка и дешифрирование команды, а в цикле М2 осуществляется собственно выполнение команды. В такте Т1, цикла М2 микропроцессор выдает на шину адреса содержимое счетчика PC, а на шину данных — байт состояния с установленным битом D3 подтверждения останова. В такте Т2 по нарастающему фронту сигнала Ф2 с максимальной выдержкой 200 не внутренние буферы шин адреса и данных переводятся в высокоимпедансное состояние, а по нарастающему фронту сигнала Ф1 в следующем такте формируется высокий уровень сигнала ожидания ОЖ. Выполнение программы прекращается и в состоянии останова микропроцессор может находиться как угодно долго. Из состояния останова МП выводится следующими способами:

путем подачи сигнала высокого уровня на вход сброса СБР с продолжительностью не менее трех периодов синхронизации. Когда на линии СБР после этого устанавливается низкий уровень, то по нарастающему фронту сигнала Ф1 генерируется внутренний сигнал сброса. Он загружает в счетчик PC нули и заставляет устройство управления сформировать следующий такт Т1 машинного цикла М1 выборки кода операции. Следовательно, МП обращается к ячейке памяти, которая обычно является начальным адресом подпрограммы;

путем подачи сигнала высокого уровня на вход прерывания ЗПР.

Микропроцессор реагирует на этот сигнал только в том случае, если установлен внутренний триггер прерываний (РПР=1). Следовательно, при необходимости нового запуска микропроцессора из состояния останова сигналом ЗПР до команды HLT необходимо разрешить прерывание командой EI. Реагируя на сигнал ЗПР, микропроцессор вводит цикл М1 выборки команды RST. Если же микропроцессор остановлен и РПР = 0, то единственным средством запуска оказывается сигнал СБР.

Особенностью режима останова является возможность входа в режим ПДП по наличию высокого уровня сигнала ЗХ. Запрос на ПДП не будет удовлетворяться только в том случае, если был уже подан сигнал ЗПР (запрос на прерывание), но не было еще подтверждения прерывания сигналом РПР. После подтверждения прерывания возможен вход в режим ПДП. Таким образом, микропроцессор может работать в различных режимах информационного обмена. Выбор режима определяется быстродействием внешнего устройства и объемом передаваемых данных. Для поддержки каждого из режимов в составе микропроцессорного комплекта предусмотрены специальные интерфейсные микросхемы.