- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

2.3 Функция "или", логическое сложение

Следующим простейшим элементом является схема, реализующая операцию логического умножения "ИЛИ":

F(x1, x2) = x1 x2 ,

где символ обозначает функцию логического сложения (дизъюнкцию). Иногда эта же функция записывается в другом виде:

F(x1, x2) = x1 x2 = x1 + x2 = x1 | x2

То же самое действие можно записать при помощи таблицы истинности, приведённой в таблице 2.4. В формуле, приведенной выше, использовано два аргумента. Поэтому элемент, выполняющий эту функцию, имеет два входа. Такой элемент обозначается "2ИЛИ". Для элемента "2ИЛИ" таблица истинности будет состоять из четырех строк (22 = 4).

Таблица 2.4 – Таблица истинности схемы, выполняющей

логическую функцию "2ИЛИ"

x1 |

x2 |

F |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

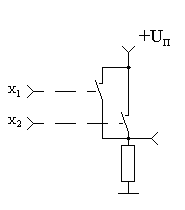

Как и в случае, рассмотренном для схемы логического умножения, воспользуемся для реализации схемы логического элемента "2ИЛИ" идеализированными ключами с электронным управлением. На этот раз соединим ключи параллельно. Эквивалентная схема, реализующая таблицу истинности 2.4, приведена на рисунке 2.6. Как видно из приведённой схемы, уровень логической единицы появится на её выходе, как только будет замкнут любой из ключей.

Рисунок 2.6 – Эквивалентная схема, реализующая логическую функцию "2ИЛИ"

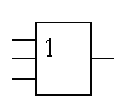

Так как функция логического суммирования может быть реализована устройствами, собранными по разным принципиальным схемам, то для обозначения этой функции используется свое условно-графическое обозначение. На условно-графическом изображении логического элемента "ИЛИ" используется специальный символ "1", как это приведено на рисунке 2.7.

Рисунок 2.7 – Условно-графическое изображение схемы, выполняющей логическую функцию "2ИЛИ"

Подобным образом описывается и функция логического сложения трёх переменных:

F(x1, x2) = x1 x2 x3

Её таблица истинности будет содержать уже восемь строк (23=4). Таблица истинности трёхвходовой схемы логического умножения "3ИЛИ" приведена в таблице 1.5, а условно-графическое изображение на рисунке 2.8. В схеме, построенной по принципу схемы, приведённой на рисунке 2.6, придётся добавить третий ключ.

Рисунок 2.8 – Условно-графическое изображение схемы, выполняющей логическую функцию "3ИЛИ"

Таблица 1.5 – Таблица истинности схемы, выполняющей

логическую функцию "3ИЛИ"

x1 |

x2 |

x3 |

F |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Теперь, после того, как мы рассмотрели принципы построения логических элементов, можно подробно остановиться на особенностях реализации логических элементов в различных схемотехнических решениях.