- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

16.1 Генераторы с цифровым управлением (nco)

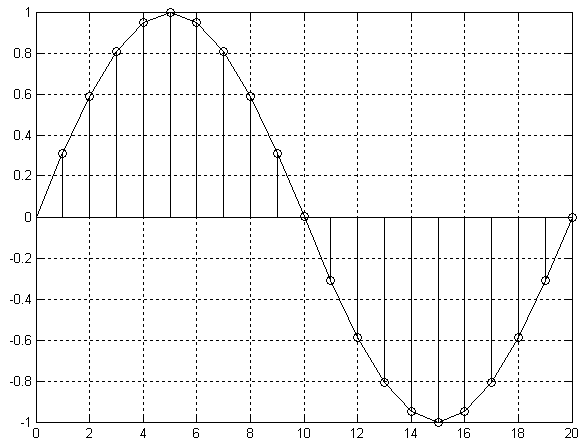

Для формирования синусоидального радиосигнала в цифровом виде можно воспользоваться ПЗУ с записанными в него значениями функции синуса. При считывании из него этих значений через равномерные промежутки времени, на выходе цифро-аналогового преобразователя можно наблюдать синусоидальный сигнал. Пример подобной формы сигнала приведен на рисунке 16.2. На этом рисунке кружочками обозначены значения напряжения на выходе цифро-аналогового преобразователя. По оси абсцисс отложен номер отсчета цифрового сигнала. Цифровое значение отсчета сигнала считывается из ячейки ПЗУ. Фильтр низкой частоты позволяет сгладить дискретность сигнала на выходе цифро-аналогового преобразователя. На рисунке 16.2 этот сигнал показан сплошной линией, соединяющей дискретные отсчеты сигнала.

Рисунок 16.2 – Временная диаграмма сигнала на выходе фазового аккумулятора

Как видно из приведенного рисунка, значение сигнала на выходе цифрового генератора в каждый момент времени определяется номером отсчета сигнала. Частоту полученного синусоидального сигнала можно изменять несколькими способами.

Первый и наиболее очевидный способ заключается в изменении тактовой частоты устройства прямого цифрового синтеза. Однако такой способ изменения частоты выходного сигнала неудобен, так как приводит к необходимости применять в качестве тактового генератора синтезатор частот.

Известно, что стабильность частоты колебания, вырабатываемого синтезатором, зависит от диапазона его перестройки. Это означает, что не существует синтезаторов с большим диапазоном перестройки частоты выходного колебания, которые обладают хорошими спектральными характеристиками.

Еще одним очень существенным недостатком приведенного способа настройки частоты цифрового генератора является то, что синтезатор частот не может мгновенно изменить свою частоту. Некоторое время после изменения частоты настройки синтезатора его частота будет колебаться около нового значения.

Второй способ перестройки частоты заключается в том, что при поступлении очередного тактового импульса можно считывать значения синусоидального сигнала из постоянного запоминающего устройства не из соседних ячеек, а пропуская одно или несколько значений отсчетов синусоидального сигнала.

Если мы будем считывать значения синусоидального сигнала через одну ячейку памяти, то полностью период синусоидального сигнала на выходе аналого-цифрового преобразователя будет получен за время в два раза меньшее относительно первоначально рассмотренного случая. В результате частота формируемого синусоидального сигнала увеличится вдвое.

Если мы будем выдавать на выход цифрового генератора содержимое каждой третьей ячейки ПЗУ синусоидального сигнала, то для завершения одного периода этого сигнала нам потребуется втрое меньшее количество тактов. А это означает, что период такого сигнала будет в три раза короче периода сигнала, полученного при считывании всех ячеек ПЗУ.

Итак, получается, что мы можем регулировать частоту выходного синусоидального сигнала, просто изменяя коэффициент счета входных импульсов. При этом номер отсчета синусоидального сигнала можно считать его фазой, а так как в процессе работы схемы номер отсчета постоянно увеличивается, то устройство, осуществляющее это действие, можно назвать аккумулятором (накопителем) фазы.

Фазовый аккумулятор обычно выполняется на арифметическом двоичном сумматоре и регистре, запоминающем результат суммирования. На один из входов сумматора подадим содержимое накапливающего регистра, а на другой вход будем подавать шаг изменения фазы. Структурная схема фазового аккумулятора приведена на рисунке 16.3.

Рисунок 16.3 – Структурная схема фазового аккумулятора

Если на вход фазового аккумулятора будем подавать единицу, то эта схема будет работать как обычный двоичный счетчик. При подаче на вход этой схемы двойки числа на выходе накапливающего регистра будут изменяться через два. При подаче на вход числа пять, при поступлении очередного тактового импульса, содержимое аккумулятора будет изменяться на пять единиц.

Даже если на вход фазового аккумулятора подать число ноль, то мы получим нулевое приращение фазы, то есть получим нулевую частоту (постоянный ток). Итак, изменением числа на входе фазового аккумулятора можно регулировать частоту синусоидального сигнала, формируемого на его выходе.

Теперь определим требования к параметрам блоков, входящих в состав фазового аккумулятора. Сначала определим количество ячеек постоянного запоминающего устройства, входящего в состав фазового аккумулятора. Количество ячеек ПЗУ будет определять минимальную частоту, которую мы сможем сформировать фазовым аккумулятором. Чем больше количество ячеек постоянного запоминающего устройства, тем ниже эта частота и, соответственно, меньше шаг перестройки синусоидального генератора прямого цифрового синтеза.

Рассмотрим конкретный пример. Пусть тактовая частота фазового аккумулятора будет 40 МГц. Тогда, если выбрать количество ячеек ПЗУ равным 4096, то мы сможем получить минимальную частоту 10 кГц. Современные микросхемы ПЗУ при приемлемой стоимости могут достигать объема 65536 ячеек. При использовании таких ПЗУ для хранения отсчетов функции синуса точность настройки частоты цифрового генератора возрастет до 610 Гц.

Теперь оценим необходимую разрядность ячеек постоянного запоминающего устройства. Для этого определим разность между значениями синуса, хранящимися в соседних ячейках памяти. Разность определим в точке наибольшего изменения функции синуса:

= sin(2×/4069) – sin(0) = sin(2×/4096) = 1,53×10–3

Эта разность соответствует точности одиннадцатиразрядного числа. Одиннадцатиразрядное число обеспечивает точность представления 0,98×10–3. Это означает, что для хранения значений синусов в постоянном запоминающем устройстве с 4096 ячейками памяти достаточно одиннадцати- двенадцатиразрядной точности. Для хранения значений синуса в ПЗУ с 65536 ячейками памяти потребуются уже пятнадцатиразрядные ячейки.

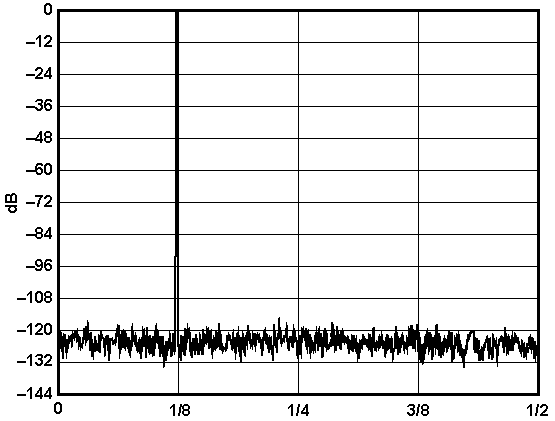

При использовании для хранения синуса постоянного запоминающего устройства с шестнадцатиразрядными ячейками можно реализовать динамический диапазон устройства прямого цифрового синтеза до 96 дБ (приблизительно по 6 дБ на каждый разряд). Это значительно превышает динамический диапазон аналоговых устройств. Динамический диапазон устройства в целом будет ограничиваться аналоговыми цепями, поэтому увеличивать разрядность ячеек ПЗУ синуса выше шестнадцати разрядов не имеет смысла.

В качестве иллюстрации возможностей рассмотренной схемы, на рисунке 16.4 приведен спектр сигнала, сформированного цифровым синусоидальным генератором.

Точно также не имеет смысла увеличивать количество ячеек в этом ПЗУ. Кто сомневается, может провести расчеты по приведенной выше методике. Какой смысл хранить в соседних ячейках одинаковые значения?! Так что же, мы не можем получить шаг перестройки синусоидального генератора, реализованного на фазовом аккумуляторе, меньший рассчитанного выше значения? Да нет же, можем.

Рисунок 16.4 – Структурная схема фазового аккумулятора с уменьшенным шагом настройки частоты

Теперь определим требования к разрядности накапливающего регистра и сумматора. На первый взгляд разрядность этих устройств должна совпадать с разрядностью шины адреса постоянного запоминающего устройства, то есть не превышать шестнадцати разрядов. Однако это не так.

Для этого достаточно увеличить разрядность сумматора и накапливающего регистра, входящий в состав фазового аккумулятора а на адресные входы постоянного запоминающего устройства подавать старшие разряды результата суммирования, как это показано на рисунке 16.5.

Рисунок 16.5 – Структурная схема фазового аккумулятора с уменьшенным шагом настройки частоты

В результате применения сумматора с разрядностью, большей разрядности адресной шины постоянного запоминающего устройства, в накапливающем регистре фаза может изменяться с любым сколь угодно малым шагом. При этом код напряжения на выходе ПЗУ будет изменяться только тогда, когда изменение значения синуса превысит шаг квантования цифро-аналогового преобразователя.

При использовании шага изменения фазы, меньшего разрядности адресной шины ПЗУ, возможно дробное соотношение периода синуса и периода накопления фазы, равной 360 (переполнения фазового аккумулятора). В этом случае возможно формирование синусоидального сигнала с периодом, отличающимся в соседних интервалах времени. Однако средняя частота генерируемого синусоидального сигнала будет точно равна заданному значению.