- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

15.4 Статические оперативные запоминающие устройства (озу)

В устройствах цифровой обработки сигналов для хранения отсчетов входного или выходного сигналов широко используются параллельные регистры, однако в ряде случаев требуется осуществлять обработку информации в последовательном виде. В этом случае информация с выходов регистров не требуется одновременно, поэтому входные отсчеты можно хранить в устройствах памяти, подобных по структуре постоянным запоминающим устройствам.

Устройства памяти, в которых в качестве запоминающих ячеек используются параллельные регистры, называются статическими ОЗУ, т.к. информация в них сохраняется все время, пока к микросхеме подключено питание.

Так как в устройствах последовательной обработки отсчеты цифрового сигнала не нужны одновременно, то в ОЗУ можно воспользоваться механизмом адресации, который уже рассматривался ранее при объяснении принципов работы ПЗУ.

В микросхемах статических ОЗУ присутствуют две операции: запись и чтение. Для их выполнения можно использовать различные шины данных (как это делается в сигнальных процессорах), но чаще используется одна и та же шина. Это позволяет экономить выводы микросхем, подключаемых к этой шине, и легко осуществлять коммутацию сигналов между различными устройствами.

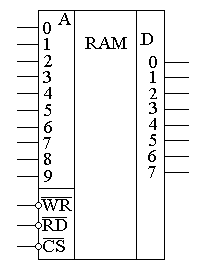

Схема статического ОЗУ приведена на рисунке 15.24. Вход и выход микросхемы в этой схеме объединены при помощи шинного формирователя. Естественно, что схемы реальных ОЗУ будут иными, чем приведенная на этом рисунке. Тем не менее, она позволяет понять, как работает реальное ОЗУ статического типа. Условное графическое обозначение ОЗУ на схемах приведено на рисунке 15.25.

Рисунок 15.24 – Структурная схема ОЗУ

Рисунок 15.25 – Условное графическое обозначение ОЗУ

На схеме рисунке 15.25 для обозначения того, что используется инвертированный сигнал или сигнал с активным низким уровнем, над именем цепи проставляется черта. К сожалению, в обычном тексте затруднительно использовать такую же черту. Поэтому для обозначения таких сигналов в книге используется два способа: символ подчеркивания перед именем цепи (_WR) или символ ‘#’ после имени (WR#).

Сигнал записи WR# позволяет записать логические уровни, присутствующие на информационных входах, во внутреннюю ячейку ОЗУ. Сигнал чтения RD# позволяет выдать содержимое внутренней ячейки памяти на информационные выходы микросхемы. В приведенной на рисунке 15.25 схеме невозможно одновременно производить операцию записи и чтения, но это в большинстве случаев и не нужно.

Конкретная ячейка микросхемы, в которую будет записываться информация, выбирается при помощи двоичного кода — адреса ячейки. Объем памяти микросхемы зависит от количества ячеек, содержащихся в ней. Количество адресных выводов микросхемы ОЗУ однозначно определяется количеством находящихся в ней ячеек памяти. Исходя из этого, количество ячеек памяти M в микросхеме можно определить по количеству адресных выводов N. Для этого необходимо возвести число 2 в степень, равную количеству адресных выводов микросхемы:

M = 2N.

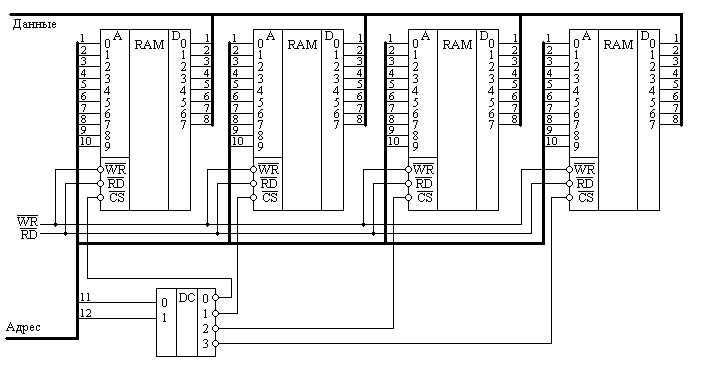

Вывод выбора кристалла CS позволяет объединять несколько микросхем для увеличения объема памяти ОЗУ. Пример объединения четырех микросхем ОЗУ с помощью дополнительного дешифратора адреса приведен на рисунке 15.26. При этом общий объем памяти запоминающего устройства увеличивается в четыре раза.

Рисунок 15.26 – Схема ОЗУ, построенного на нескольких микросхемах памяти

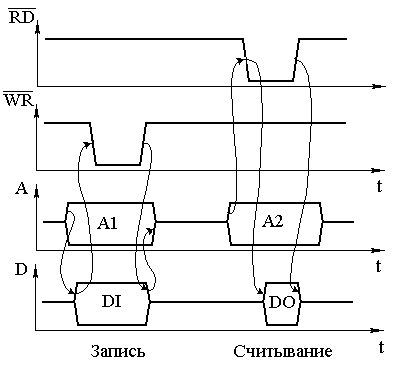

Временные диаграммы чтения данных из статического ОЗУ, совпадают, с временными диаграммами для рассмотренного ранее ПЗУ. Временные диаграммы записи в статическое ОЗУ и чтения из него приведены на рисунке 15.27.

Рисунок 15.27 – Временная диаграмма обращения к ОЗУ

На рисунке 15.27 стрелочками показана последовательность, в которой должны формироваться управляющие сигналы. На этом рисунке RD — это сигнал чтения; WR — сигнал записи; A — сигналы шины адреса (так как отдельные биты в шине адреса могут принимать разные значения, то показаны пути перехода двоичного сигнала как в единичное, так и в нулевое состояние); DI — входная информация, предназначенная для записи в ячейку ОЗУ, расположенную по адресу A1; DO — выходная информация, считанная из ячейки ОЗУ, расположенной по адресу A2.