- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

12.3 Умножители частоты

Цепи фазовой подстройки частоты часто используются для умножения частоты. Раньше для этой цели использовались схемы генераторов гармоник с последующим выделением соответствующей гармоники узкополосным фильтром.

Намного лучше для этой цели подходит схема фазовой автоподстройки частоты. В этой схеме относительно просто можно изменять коэффициент умножения частоты изменением коэффициента деления в цепи обратной связи. Для умножения частоты внутри микросхем используется либо цифровая, либо полностью цифровая схема фазовой автоподстройки частоты.

Умножители частоты в настоящее время обычно используются для увеличения внутренней тактовой частоты больших интегральных микросхем. В этих микросхемах цифровая схема фазовой автоподстройки частоты получила название аналогового умножителя тактовой частоты, а полностью цифровая схема ФАПЧ получила название цифрового умножителя частоты.

Для увеличения тактовой частоты цифровых микросхем чаще используется полностью цифровая схема умножения частоты, а для смешанных схем или схем, предназначенных для цифровой обработки сигналов предпочтительнее использование аналогового умножителя частоты. Это связано со спектральной чистотой выходного сигнала. Аналоговая схема обеспечивает более стабильное колебание, но при этом медленнее выходит на рабочий режим.

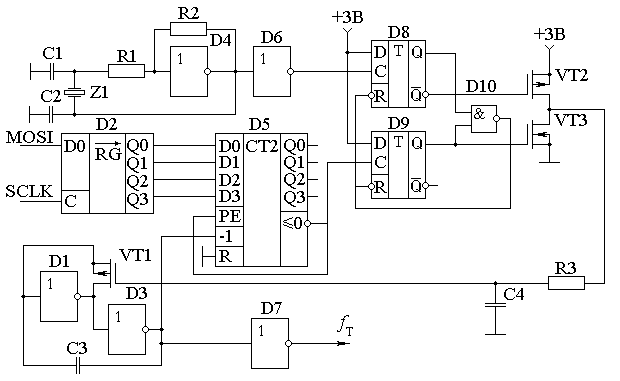

Пример принципиальной схемы аналогового умножителя тактовой частоты приведен на рисунке 12.18.

Рисунок 12.18 – Принципиальная схема аналогового умножителя частоты

В этой схеме опорный генератор с кварцевой стабилизацией частоты реализован на логических элементах D4 и D6. Генератор, управляемый напряжением, реализован на элементах D1 и D3. В качестве регулировочного элемента использован полевой транзистор VT1. Фазовый компаратор реализован на микросхемах D7, D8 и D10. Полосу захвата цепи фазовой автоподстройки определяет фильтр низкой частоты, реализованный на конденсаторе C4.

Данный умножитель частоты допускает только шестнадцать ступеней регулировки тактовой частоты, однако для целей задания тактовой частоты цифровой микросхемы, такого набора частот вполне достаточно. Код, определяющий коэффициент умножения в схеме, изображенной на рисунке 12.18, вводится через SPI порт, собранный на сдвиговом регистре D2. Особенности применения этого порта мы уже рассматривали ранее.

В более сложных схемах умножителей частоты вводятся делители между опорным генератором и фазовым компаратором. Это позволяет реализовывать дробные коэффициенты умножения частоты.

12.4 Частотные детекторы, построенные на основе фапч

Частотные детекторы, построенные на основе элементов задержки, обычно реализуют широкую полосу детекторной характеристики. Однако используемые в реальных радиосистемах частотно-модулированные колебания обычно являются узкополосными. Поэтому для приема частотно-модулированных радиосигналов чаще используют частотные детекторы, построенные на основе схемы фазовой автоподстройки частоты.

В схеме частотного детектора не используется фазовый компаратор. Здесь лучше подходит схема фазового детектора, так как на ее выходе сигнал пропорционален фазе принимаемого колебания. Пример схемы частотного детектора, построенного на основе схемы фазовой автоподстройки частоты, приведен на рисунке 12.19.

Рисунок 12.19 – Пример схемы частотного детектора, построенного на основе схемы фазовой автоподстройки частоты

В данной схеме частотный детектор реализован на основе фазового детектора. Как мы уже определили ранее, функции фазового детектора может выполнять логический элемент "исключающее ИЛИ". Генератор управляемый напряжением собран на инверторах D1 и D2, а подстройку его частоты осуществляет транзистор VT1.

При изменении частоты входного сигнала схема фазовой автоподстройки вынуждена подстраивать ГУН на эту же частоту. При этом естественно изменяется напряжение на затворе транзистора VT1. То есть напряжение в этой точке будет соответствовать отклонению частоты входного сигнала от своего номинального значения, а значит, вся схема в целом будет осуществлять детектирование частотно-модулированного сигнала.

Полоса детектируемого сигнала в приведенной схеме будет зависеть от крутизны регулировочной характеристики генератора, управляемого напряжением и коэффициента усиления фазового детектора, выполненного на логическом элементе D3.

До сих пор рассматривались цифровые устройства, которые предназначены для управления устройствами связи. Не менее важны цифровые устройства, способные осуществлять обработку аналоговых сигналов непосредственно в цифровом виде. При обработке сигналов в цифровом виде появляется своя специфика и следует ее учитывать при разработке соответствующих устройств. Именно этим вопросам и будут посвящены последующие главы.