- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

12.2 Схемы определения ошибки по частоте

В качестве фазового детектора в цепи фазовой автоподстройки частоты могут быть использованы различные схемы. Схемы частотных и фазовых детекторов широко используются в аналоговой технике. Это могут быть хорошо известные схемы фазовых детекторов, построенные на диодах. В качестве фазового детектора прекрасно может работать аналоговый умножитель, хорошо известный в аналоговой схемотехнике.

Однако в большинстве случаев в таких схемах используются трансформаторы, что делает такие схемы неудобными для массового производства, поэтому имеет смысл попытаться найти решение при помощи цифровых микросхем.

Цифровой фазовый детектор

В аналоговых схемах наилучшими характеристиками обладают фазовые детекторы, построенные на основе умножителя. Составим таблицу истинности умножителя, сигнал на входе и выходе которого может принимать только два значения — единицу и минус единицу. Использование таких значений позволяет интерпретировать сигнал на входе умножителя как знак аналогового сигнала. Полученная таблица истинности умножителя знаков приведена в таблице 12.1.

Таблица 12.1 – Таблица истинности умножителя знаков

X1 |

X2 |

Y |

–1 |

–1 |

1 |

–1 |

1 |

–1 |

1 |

–1 |

–1 |

1 |

1 |

1 |

Если теперь символ "–1" обозначить как "0", то мы увидим, что полученная таблица истинности совпадает с инвертированной таблицей истинности логического элемента "исключающее ИЛИ". Для сравнения в таблице 12.2 приведена таблица истинности логического элемента "исключающее ИЛИ".

Таблица 12.2 – Таблица истинности элемента "исключающее ИЛИ"

X1 |

X2 |

Y |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

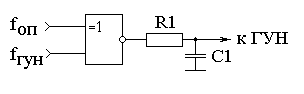

Инверсия выходного сигнала в нашем случае не имеет принципиального значения. В случае необходимости мы всегда можем использовать дополнительный инвертор или изменить схему включения регулировочного элемента в генераторе управляемом напряжением. Это означает, что логический элемент "исключающее ИЛИ" вполне может быть использован в качестве фазового детектора. Схема цифрового фазового детектора приведена на рисунке 12.5.

Рисунок 12.5 – Схема цифрового фазового детектора

Для проверки рассмотрим три варианта сигналов, поступающих на вход фазового детектора, построенного на основе схемы "исключающего ИЛИ". В первом варианте сигналы на входах фазового детектора полностью синфазны. Временные диаграммы сигналов на входе и выходе логического элемента "исключающее ИЛИ" приведены на рисунке 12.6.

Рисунок 12.6 – Временные диаграммы синфазных сигналов

Анализируя эти сигналы можно сделать вывод, что при синфазных напряжениях на входах фазового детектора, построенного на логическом элементе "исключающее ИЛИ" на выходе присутствует нулевое напряжение.

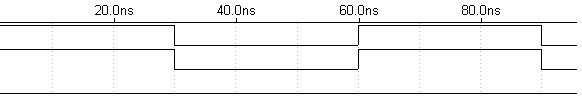

Теперь подадим на входы фазового детектора сигналы, сдвинутые друг относительно друга на 15. Временные диаграммы сигналов с таким сдвигом фазы на входе и выходе логического элемента "исключающее ИЛИ" приведены на рисунке 12.7.

Рисунок 12.7 – Временные диаграммы сигналов, сдвинутых по фазе на 15

В этом случае на выходе логического элемента "исключающее ИЛИ" появляются импульсы с частотой, равной частоте входных сигналов. Длительность формируемых импульсов пропорциональна сдвигу фаз входных сигналов. Если проинтегрировать этот сигнал, то можно получить напряжение, пропорциональное фазовому сдвигу между входными сигналами.

Подадим на входы фазового детектора сигналы, сдвинутые друг относительно друга на 165. Временные диаграммы сигналов на входе и выходе логического элемента "исключающее ИЛИ" приведены на рисунке 12.8.

Рисунок 12.8 – Временные диаграммы сигналов, сдвинутых по фазе на 165

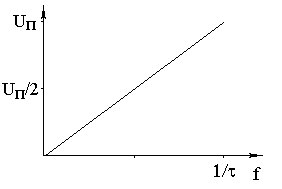

Как и ожидалось, скважность сигнала на выходе фазового детектора изменилась. Теперь напряжение на выходе сглаживающей RC цепочки близко к напряжению питания. Можно построить зависимость напряжения на выходе схемы детектора от сдвига фаз на ее входе. Эта зависимость приведена на рисунке 12.9.

Рисунок 12.9 – Зависимость напряжения на выходе фазового детектора

от сдвига фаз входных колебаний

Анализируя эту зависимость можно сделать вывод, что фазовый детектор, построенный на основе логического элемента "исключающее ИЛИ" обладает прекрасной линейностью преобразования разность фаз — напряжение и вполне может заменить аналоговый фазовый детектор.

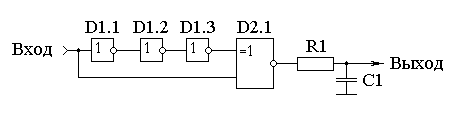

Цифровой частотный детектор

Частотный детектор обычно строится на основе фазового детектора. Для этого необходимо преобразовать изменение частоты входного сигнала в изменение его фазы. В цифровых детекторах это преобразование может быть осуществлено обычной задержкой входного сигнала. В качестве элемента задержки можно воспользоваться обыкновенным инвертором. Принципиальная схема частотного детектора, реализованного в соответствии с этим принципом, приведена на рисунке 12.10.

Рисунок 12.10 – Принципиальная схема частотного детектора,

построенного на логических элементах

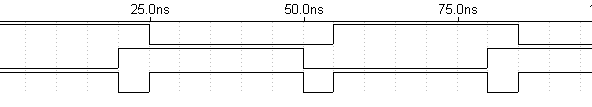

Для того чтобы понять, как работает эта схема рассмотрим временные диаграммы сигналов на входах и выходе логического элемента "исключающее ИЛИ", приведённые на рисунке 12.11.

Рисунок 12.11 – Временные диаграммы сигналов на входах и выходе логического элемента "исключающее ИЛИ"

По приведённым временным диаграммам видно, что длительность импульсов на выходе логического элемента "исключающее ИЛИ" зависит от задержки использованного инвертора. При этом их период зависит от частоты входного колебания. Это означает, что скважность импульсов, а, следовательно, и напряжение на выходе интегрирующей RC цепочки определяется частотой входного колебания.

Частотная зависимость напряжения на выходе исследуемой схемы цифрового детектора приведена на рисунке 12.12.

Рисунок 12.12 – Частотная зависимость напряжения на выходе схемы цифрового частотного детектора

По приведённой на рисунке 12.12 частотной зависимости видно, что цифровой частотный детектор обладает прекрасной линейностью. Линейность зависит в основном от длительности фронтов импульсов.

Так как время задержки одиночного инвертора составляет единицы или десятки наносекунд, то рабочая полоса частотного детектора составляет сотни или десятки мегагерц соответственно. При этом крутизна его частотной характеристики получается недостаточной для большинства практических применений. Например, не позволяет использовать данный детектор для демодуляции частотно-модулированных сигналов.

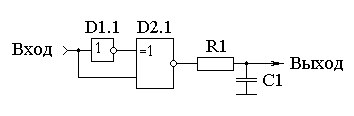

Увеличить крутизну частотной характеристики частотного детектора можно, увеличив время задержки сигналов на входе умножителя, собранного на основе логического элемента "исключающее ИЛИ". Так как в одном корпусе микросхемы обычно находится несколько инверторов, то можно увеличить количество инверторов, использующихся в качестве элементов задержки, практически не увеличивая занимаемой площади печатной платы. Подобная схема частотного детектора приведена на рисунке 12.13.

Рисунок 12.13 – Принципиальная схема частотного детектора,

построенного на трёх инверторах

Частотная зависимость этого детектора приведена на рисунке 12.14. Преобразование частоты в напряжение на выходе схемы можно производить на трёх участках этой зависимости.

Рисунок 12.14 – Частотная зависимость напряжения на выходе схемы цифрового частотного детектора

Крутизна частотной характеристики увеличилась втрое. Во столько же раз уменьшился частотный диапазон одного участка. Можно сделать вывод, что крутизна частотной зависимости частотного детектора зависит от величины задержки на входе умножителя, собранного на логическом элементе "исключающее ИЛИ". При этом, чем больше крутизна этой зависимости, тем в меньшем диапазоне частот работает цифровой частотный детектор.

Фазовый компаратор

При работе в цепи фазовой автоподстройки ошибка по фазе может приводить к неточной настройке синтезатора. Это связано с принципиальной работой фазового детектора — он вырабатывает напряжение, использующееся для настройки ГУН. Для удержания ГУН на заданной частоте необходим постоянный сдвиг фаз межу опорным колебанием и подстраиваемым колебанием, вырабатываемым ГУН. Устранить этот недостаток можно при использовании схемы фазового компаратора.

Фазовый компаратор позволяет формировать напряжение не пропорциональное фазе, а соответствующее знаку фазы, то есть на его выходе может быть три значения напряжения: отставание по фазе, опережение по фазе и точное совпадение по фазе входных колебаний.

Если проинтегрировать такое напряжение на конденсаторе, то при отставании фазы колебания с выхода ГУН (частота на выходе ГУН меньше требующегося значения), напряжение на конденсаторе будет уменьшаться. При опережении фазы колебания с выхода ГУН фазы опорного колебания (частота на выходе ГУН больше требующегося значения), напряжение на конденсаторе будет увеличиваться. Один из вариантов реализации схемы фазового компаратора приведен на рисунке 12.15.

Рисунок 12.15 – Принципиальная схема фазового компаратора

Для построения фазового компаратора в этой схеме используются два D‑триггера. На тактовые входы этих триггеров подаются опорное и подстраиваемое колебания. При подаче на вход схемы высокого потенциала, в триггер записывается единичное значение. При записи единичных значений в оба триггера триггеры обнуляются сигналом, формируемым микросхемой D2.

В результате, в процессе работы схемы фазового компаратора при опережении фазы опорного колебания импульсы будут формироваться на выходе триггера D1.1, при опережении фазы подстраиваемого колебания импульсы появятся на выходе триггера D1.2. При точном совпадении фаз опорного и подстраиваемого колебания импульсы на выходе обоих триггеров будут настолько короткими, что ими можно пренебречь.

Импульсы с выходов триггера D1.1 подаются на заряжающий конденсатор C1 ключ, собранный на транзисторе VT1, а импульсы с выхода триггера D1.2 подаются на разряжающий конденсатор C1 ключ, собранный на транзисторе VT2. В результате, напряжение на конденсаторе C1 будет оставаться неизменным только при точном совпадении фазы опорного и подстраиваемого колебаний.

Временные диаграммы сигналов на входах и выходах фазового компаратора при различном соотношении фаз опорного и подстраиваемого колебаний приведены на рисунке 12.16.

Рисунок 12.16 – Временные диаграммы сигналов на входах и выходах

триггеров, входящих в состав фазового компаратора:

а — опорное колебание опережает подстраиваемое по фазе;

б — подстраиваемое колебание опережает опорное по фазе;

в — колебания совпадают по фазе

Обычно для управления варикапами, входящими в состав генератора управляемого напряжением (ГУН), требуются напряжения, большие напряжения питания цифровых микросхем (порядка 12 … 15 В). В таких случаях на выходе фазового компаратора, схема которого приведена на рисунке 12.15, требуется усилитель. В некоторых случаях можно обойтись без усилителя, если воспользоваться диодными ключами, как это показано на принципиальной схеме, приведённой на рисунке 12.17.

Рисунок 12.17 – Принципиальная схема фазового компаратора с диодными ключами

В приведённой на рисунке 12.17 схеме фазового компаратора заряд ёмкости C1 производится через резистор R5, а разряд этой ёмкости производится через резистор R4 и полностью открытый транзистор VT1. Использование различных резисторов в цепи заряда и разряда конденсаторов позволяет независимо регулировать время перестройки синтезатора вниз и вверх по частоте.

На этом можно завершить обзор элементов, входящих в состав схемы фазовой подстройки частоты и перейти к рассмотрению конкретных примеров использования схем ФАПЧ.