- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

11 Синхронные последовательные порты

При работе с современными цифровыми и аналого-цифровыми микросхемами достаточно важным вопросом является количество внешних выводов используемых микросхем. В большинстве случаев именно количество выводов определяет габариты микросхемы. Чем больше выводов — тем больше габариты корпуса микросхемы, а, следовательно, и габариты всего проектируемого устройства в целом. Именно поэтому в современных микросхемах стараются минимизировать количество внешних выводов.

Максимально минимизировать количество выводов микросхемы с цифровым управлением можно при использовании последовательной передачи различных бит через один и тот же вывод микросхемы. Для того чтобы можно было снова разделить биты на приёмном конце, используются специальные сигналы — сигналы синхронизации. Они могут передаваться через отдельные выводы микросхемы или совмещаться с передаваемыми информационными битами.

Цифровые устройства, формирующие совокупность информационных и синхронизирующих сигналов или способные принимать эту совокупность называются последовательными портами. Последовательные порты встраиваются в состав микросхем однокристальных приёмников, синтезаторов частот, аналого-цифровых и цифро-аналоговых преобразователей, ну и естественно они входят в состав современных сигнальных процессоров и микроконтроллеров.

При разработке новых видов схем с использованием программируемых логических или программируемых аналоговых схем использование последовательных портов тоже может значительно уменьшить количество выводов микросхемы требуемое для обмена информацией между различными блоками.

11.1 Ssi интерфейс (dsp порт)

Структура синхронного последовательного интерфейса в основном определяется типом данных, передаваемых по этому порту. При обработке сигналов требуется между микросхемами передавать непрерывные потоки информации. Обработкой данных обычно занимаются цифровые сигнальные процессоры (DSP), поэтому последовательные порты, предназначенные для передачи цифровой информации с максимальной скоростью, часто называются DSP портами.

Какие данные могут образовывать непрерывные потоки. Чаще всего это звуковые или видеосигналы, хотя в качестве сигнала, образующего непрерывный поток данных, могут выступать сигналы измерения биотоков живого организма или сигналы геомагнитных измерений. Как можно определить из определения природы таких сигналов, источником цифрового потока должен быть аналого-цифровой преобразователь (АЦП). Если микросхема (не сигнальный процессор) является приёмником цифрового потока данных, то в ее состав обычно входит цифро-аналоговый преобразователь (ЦАП).

При преобразовании аналоговой информации в цифровую форму и наоборот очень важно обеспечить стабильность тактового сигнала. Только в этом случае можно избежать искажений исходного или формируемого сигнала. Такой сигнал тактовой синхронизации обычно вырабатывается специальными термостабилизированными (или термокомпенсированными) высокостабильными кварцевыми генераторами, питаемыми от отдельного стабилизатора питания.

Скорость передачи информации в цифро-аналоговый или аналого-цифровой преобразователь должна быть строго согласована по времени со скоростью передачи по каналу связи (последовательному порту). Именно поэтому сигналы синхронизации, необходимые для работы DSP порта, вырабатываются из входного высокостабильного тактового сигнала самой микросхемой аналого-цифрового или цифро-аналогового преобразователя и подаются на сигнальный процессор или программируемую логическую интегральную схему.

Проще всего преобразовать число, представленное в параллельном коде, в последовательный вид можно при помощи сдвигового регистра. При этом на приёмном конце важно знать момент, когда производится запись в этот регистр. Знание этого момента времени позволит определить, какой из передаваемых бит является старшим значащим разрядом, а какой — младшим. Так как поток двоичной информации передаётся постоянно, то сигналы записи в регистр будут подаваться с одним и тем же периодом.

Выходной двоичный код бит за битом можно снимать с последнего выхода сдвигового регистра. Для того чтобы на приёмном конце этот сигнал принимался без ошибок, каждый бит должен сопровождаться синхронизирующим импульсом. При этом чтобы отличать синхросигналы друг от друга, импульсы, сопровождающие информационные биты, стали называть тактовой синхронизацией (CLK), а сигнал, отмечающий момент записи в регистр — кадровой синхронизацией (FS).

Сигналы кадровой и тактовой синхронизации должны быть жестко связаны между собой, поэтому они обычно формируются из одного высокостабильного колебания при помощи цифрового счётчика.

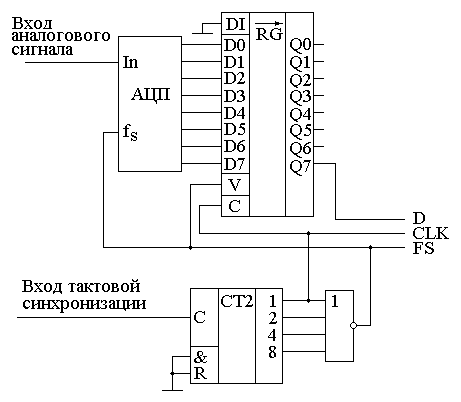

Давайте рассмотрим пример передачи восьмиразрядного последовательного слова. В качестве источника цифрового потока используем аналого-цифровой преобразователь. Получившаяся в результате схема синхронного последовательного порта приведена на рисунке 11.1.

Как видно из приведенной схемы, на вход двоичного счётчика подаются импульсы от генератора высокостабильных колебаний. Из этих импульсов вырабатывается сигнал тактовой синхронизации, который подается на выход схемы и одновременно поступает на вход синхронизации передающего сдвигового регистра.

Рисунок 11.1 – Схема передающей части последовательного DSP-порта

Логический элемент "4ИЛИ-НЕ", подключенный к выходу четырёхразрядного счётчика формирует импульсы кадровой синхронизации с частотой в восемь раз меньшей частоты тактовой синхронизации.

Такую частоту можно было бы получить с выхода "8" двоичного счётчика, но нам требуется длительность импульса, равная длительности импульса тактовой синхронизации. Логический элемент "4ИЛИ" позволяет декодировать нулевое состояние счётчика. В результате этого на его выходе длительность импульса равна длительности импульсов тактовой синхронизации, а сам импульс появляется в самом начале кадра передачи данных с выхода АЦП.

В свою очередь длительность импульсов на выводе CLK равна периоду сигнала тактовой синхронизации, так как этот сигнал снимается с выхода младшего разряда двоичного счётчика.

Кадр передачи данных начинается с параллельной записи результата преобразования АЦП в передающий сдвиговый регистр. Для этого импульс кадровой синхронизации подаётся на вход параллельной записи в регистр сдвига. В приведённой на рисунке 11.1 схеме предполагается, что запись в регистр осуществляется по переднему фронту этого импульса.

Этот же импульс кадровой синхронизации подаётся на вход синхронизации аналого-цифрового преобразователя. Внутренняя схема АЦП выполнена так, чтобы аналого-цифровое преобразование начиналось по заднему фронту импульса. Такой подбор схем АЦП и регистра сдвига позволяет сначала записать результат в регистр, а затем начать новое преобразование аналогового сигнала в цифровую форму по одному и тому же импульсу синхронизации.

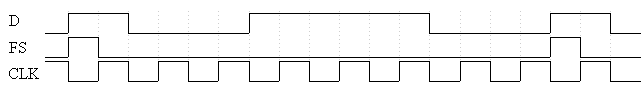

Пример временных диаграмм сигналов данных и сопровождающих их сигналов тактовой и кадровой синхронизации на выходе последовательного DSP-порта приведен на рисунке 11.2.

Рисунок 11.2 – Временные диаграммы сигналов на выходе синхронного последовательного DSP‑порта

В приведенных на рисунке 11.2 временных диаграммах осуществляется передача двоичного числа 100111002. При этом запись информации в последовательный регистр производится по сигналу кадровой синхронизации FS. В этот момент на выходе Q7 регистра сдвига появляется старший бит результата преобразования. Начиная от этого момента, начинают отсчитываться импульсы тактовой синхронизации CLK.

Приведенный на схеме рисунке 11.1 регистр осуществляет сдвиг своего содержимого по заднему фронту этих импульсов. В результате на выходе Q7, а значит на выводе порта D, последовательно один за другим будут появляться биты передаваемого двоичного числа.

Для безошибочной передачи информации последовательного порта по соединительным линиям, в приёмный регистр эти данные должны записываться по переднему фронту импульсов CLK, так как именно этот фронт совпадает с серединой битового интервала. Это позволит избежать искажений, возникающих на фронтах передаваемой информации.

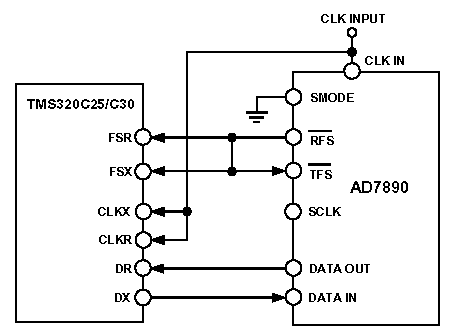

Как уже говорилось ранее, DSP-порты предназначены для передачи данных между аналого-цифровыми (или цифро-аналоговыми) преобразователями и сигнальными процессорами. В качестве примера рассмотрим схему соединения между собой АЦП AD7890 и сигнального процессора TMS320C25. Упрощённая структурная схема соединения этих микросхем приведена на рисунке 11.3.

На этой схеме используется двунаправленный последовательный порт. Синхронизация всей схемы осуществляется от внешнего высокостабильного генератора импульсов (вход CLK INPUT). Так как порт двунаправленный, то есть два сигнала кадровой синхронизации: RFS — сигнал кадровой синхронизации приёмника и TFS — сигнал кадровой синхронизации передатчика. У сигнального процессора им соответствуют два вывода кадровой синхронизации: FSR — сигнал кадровой синхронизации приёмника и FSX — сигнал кадровой синхронизации передатчика.

Рисунок 11.3 – Упрощённая схема соединения микросхемы АЦП с последовательным выходом и сигнального процессора

В приведенной на рисунке 11.3 схеме используется одна и та же скорость передачи данных, как в приёмнике, так и в передатчике. Поэтому все выводы кадровой синхронизации соединены между собой и все синхронизируются от сигнала кадровой синхронизации, формируемого микросхемой AD7890 на выводе RFS.

В качестве сигнала тактовой синхронизации последовательного порта используется сигнал внешнего генератора опорной частоты. Он подаётся на входы тактовой синхронизации сигнального процессора как приёмника CLKR, так и передатчика CLKT.

Выводы передачи данных соединены соответственно своему назначению, вывод передатчика АЦП DATA OUT соединён с входом приёмника сигнального процессора DR, а вывод передатчика сигнального процессора DT соединён с входом приёмника АЦП DATA IN.

Теперь давайте рассмотрим ещё один широко распространённый синхронный последовательный порт — SPI интерфейс.