- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

8.2 Регистры

Регистром называется последовательное или параллельное соединение нескольких триггеров. Регистры обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические, так и статические D триггеры (триггеры-защелки). Количество триггеров в составе регистра определяет его разрядность. В качестве отдельных микросхем обычно используются четырех- или восьмиразрядные триггеры.

Параллельные регистры.

Название параллельного регистра связано с тем, что входы и выходы всех триггеров в этой схеме используются независимо. Входы синхронизации всех триггеров соединены параллельно. Это приводит к тому, что информация в них записывается одновременно.

Параллельный регистр используется для одновременного запоминания многоразрядных двоичных (или недвоичных) чисел (ведь не будем же мы записывать отдельные разряды одного и того же числа записывать в различные моменты времени).

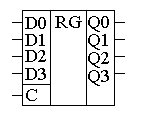

Количество триггеров, входящих в состав параллельного регистра определяет его разрядность. Принципиальная схема четырёхразрядного параллельного регистра приведена на рисунке 8.27, а его условно-графическое обозначение – на рисунке 8.28. В условно-графическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом триггере (разряде) регистра. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условно-графического обозначения символами RG.

Рисунок 8.27 – Схема параллельного регистра

В приведённом на рисунке 8.28 условно-графическом обозначении параллельного регистра инверсные выходы триггеров не показаны. В микросхемах регистров инверсные выходы триггеров часто не выводятся наружу для экономии количества выводов корпуса.

Рисунок 8.28 – Условно-графическое обозначение параллельного регистра

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто устанавливается инвертор.

Следует отметить, что назначение разрядов является условным. Если по каким либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно сделать. При перенумерации входов регистров нужно не забыть, точно таким же образом, изменить номера выходов параллельного регистра.

Для реализации параллельного регистра можно использовать как триггеры со статическим входом синхронизации, так и с динамическим. В переводной литературе при использовании для построения параллельного регистра триггеров-защелок (триггеров со статическим входом синхронизации) этот регистр, в свою очередь, называют регистром-защелкой.

При использовании регистров со статическим входом тактирования удаётся достичь максимального быстродействия цифровой схемы, однако при этом следует соблюдать осторожность, так как при воздействии на вход синхронизации C единичного потенциала логические сигналы со входов такого регистра будут свободно проходить на его выходы. При использовании статических регистров в схеме обычно используется двухтактная синхронизация, подобная рассмотренной в главе, посвященной одновибраторам.

Промышленностью выпускаются четырёхразрядные и восьмиразрядные микросхемы параллельных регистров. Для построения восьмиразрядных микросхем обычно используются регистры со статическим входом синхронизации. В качестве примера восьмиразрядных параллельных статических регистров можно назвать такие микросхемы, как К580ИР22 и 1533ИР33 (иностранный аналог 74ACT573).

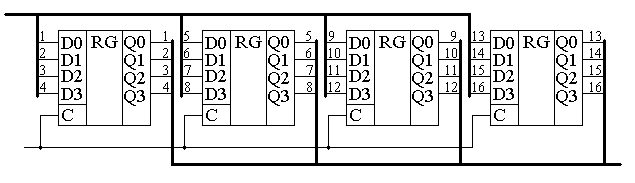

При решении практических задач часто требуется разрядность параллельных регистров большая восьми. В таком случае можно увеличивать разрядность регистров параллельным соединением готовых микросхем. Принципиальная схема параллельного соединения четырёх регистров приведена на рисунке 8.29.

Рисунок 8.29 – Увеличение разрядности параллельного регистра

В схеме, приведенной на рисунке 8.29, реализован 24-х разрядный параллельный регистр. При необходимости, входной ток, потребляемый этой схемой по входу тактовой синхронизации, может быть уменьшен при помощи усилителя. В качестве усилителя сигнала тактовой синхронизации можно применить обыкновенный инвертор.

Последовательные регистры.

Кроме параллельного соединения триггеров для построения регистров используются последовательное соединение этих элементов. Схемы, в которых триггеры соединены последовательно, называются последовательными регистрами.

Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

Принципиальная схема последовательного регистра, собранного на основе D‑триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 8.30.

Рисунок 8.30 – Схема последовательного регистра

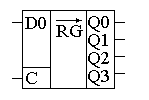

В этом регистре выход первого триггера соединён с входом второго, выход второго триггера соединён с входом третьего и т.д. Условно-графическое изображение рассмотренного последовательного регистра приведено на рисунке 8.31.

Рисунок 8.31 – Условно-графическое обозначение последовательного регистра на принципиальных схемах

Входы синхронизации в последовательных регистрах, как и в параллельных, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного регистра.

Преобразование последовательного кода в параллельный производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход D0. Каждый бит сопровождается отдельным тактовым импульсом, который поступает на вход синхронизации C.

После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере и поступает на его выход, а так как он соединён с входом второго триггера, то и на его вход.

После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. Одновременно следующий бит запоминается в первом триггере.

После поступления четвертого тактового импульса в триггерах регистра будут записаны уровни бит, которые последовательно присутствовали на входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах.

Пусть на вход регистра поступает сигнал, временная диаграмма которого изображена на рисунке 8.32, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 8.7.

На рисунке 8.32 вместе с логическими уровнями записываются значения бит, которые передаются по соединительной линии или присутствуют на выходах сдвигового регистра.

В таблице 8.7 символом X обозначено неопределенное значение, возникающее в триггерах регистра при включении питания или оставшееся от предыдущего цикла работы схемы.

D |

|

1 |

|

|

0 |

|

|

1 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

0 |

|

1-первый бит |

0 – второй бит |

1 – третий бит |

1 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

0 |

|

0 |

|

|

1-первый бит |

0 – второй бит |

1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

0 |

|

0 |

|

|

0 |

|

|

1-первый бит |

0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

1 |

|

Рисунок 8.32 - Временная диаграмма работы сдвигового регистра

Таблица 8.7 – Состояние выходов сдвигового регистра

-

выход № такта

1

2

3

1

Q0

1

0

1

1

Q1

X

1

0

1

Q2

X

X

1

0

Q3

X

X

X

1

Универсальные регистры.

Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы. Это связано с необходимостью записи в регистр параллельного двоичного кода при преобразовании параллельного кода в последовательный.

Переключение регистра из параллельного режима работы в последовательный и наоборот осуществляется при помощи мультиплексора (коммутатора). Использование коммутатора позволяет подключать входы триггеров регистра либо к внешним выводам микросхемы, либо к выходу предыдущего триггера.

Напомним, что двухвходовый мультиплексор можно реализовать при помощи логических элементов "2И‑2ИЛИ". Элементы "И" при этом работают в качестве электронных ключей, а элементы "ИЛИ" объединяют их выходы.

Схема универсального последовательно-параллельного регистра с использованием коммутаторов на логических элементах "2И‑2ИЛИ" приведена на рисунке 8.33. В этой схеме для переключения регистра из последовательного режима работы в параллельный используется вход V. Подача на этот вход единичного потенциала превращает схему в параллельный регистр. При этом на входы ключей, подключенных к информационным входам D, подаётся единичный потенциал. Это приводит к тому, что сигналы с входов параллельной записи данных поступают на входы логических элементов "ИЛИ", а на входы ключей, подключенных к выходам предыдущих триггеров, подаются нулевые потенциалы. То есть на выходах этих ключей будут присутствовать нулевые потенциалы, и они не будут мешать работе.

Рисунок 8.33 – Принципиальная схема универсального последовательно-параллельного регистра

Подача на вход V нулевого потенциала приводит к отключению входов параллельных данных от входов триггеров. Сигналы же с выхода предыдущего триггера свободно проходит через верхние логические элементы "И" на вход последующего триггера, так как на его второй вход подаётся единичный потенциал.

Инверторы на входах V и C использованы для усиления входного сигнала по току. В результате применения такого решения входной ток микросхемы будет равен не суммарному току четырёх логических элементов" И", а входному току инвертора.

Условно-графическое изображение универсального регистра, принципиальная схема которого показана на рисунке 8,33, приведено на рисунке 8.34. Вход последовательного ввода данных на этом рисунке обозначен как DI и отделён от других групп входов чертой. Точно так же выделены в отдельные группы и входы управления V и синхронизации C.

Рисунок 8.34 – Условно-графическое обозначение универсального регистра на принципиальных схемах