- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

6.3 Декодеры

Декодеры (дешифраторы) позволяют преобразовывать одни виды бинарных кодов в другие. Например, преобразовывать позиционный двоичный код в линейный восьмеричный или шестнадцатеричный. Преобразование бинарных кодов производится по правилам, описываемым в таблицах истинности, поэтому построение принципиальных схем дешифраторов не представляет трудностей. Для построения схемы дешифратора можно воспользоваться правилами построения схемы для произвольной таблицы истинности, рассмотренными ранее.

Десятичный дешифратор.

Рассмотрим пример построения декодера из двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Сигнал с этих выводов можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру. Таблица истинности такого декодера приведена в таблице 6.3.

Таблица 6.3 – Таблица истинности десятичного декодера.

|

Входы |

Выходы |

||||||||||||

№ комбинации |

8 |

4 |

2 |

1 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

3 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

4 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

5 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

6 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

7 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

9 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Десятичный код, записанный в таблице истинности 6.3, иногда называют линейным десятичным кодом. Точно таким же образом можно составить таблицу истинности и для восьмеричного декодера. В этом случае на его выходе будет присутствовать линейный восьмеричный код.

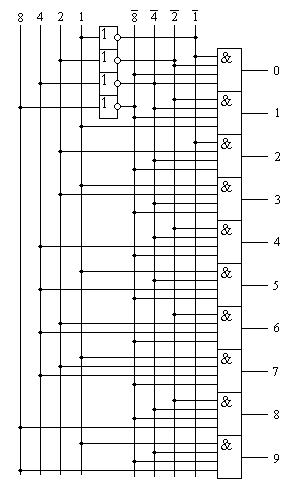

Принципы построения цифровой схемы по произвольной таблице истинности были рассмотрены в предыдущих главах. В соответствии с ними получим схему десятичного декодера, таблица истинности которого записана в таблице 6.3. Полученная в результате синтеза принципиальная схема десятичного дешифратора приведена на рисунке 6.9.

Рисунок 6.9 – Принципиальная схема двоично-десятичного декодера

Как видно на этой схеме для реализации каждой строки таблицы истинности потребовалась схема "4И". Схема "ИЛИ" не потребовалась, так как в таблице истинности на каждом выходе присутствует только одна единица, а значит объединять выходы логических элементов "И" не требуется.

Дешифраторы выпускаются в виде отдельных микросхем или используются в составе других микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ.

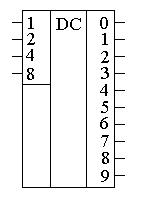

На рисунке 6.10 приведено условно-графическое обозначение двоично-десятичного дешифратора. На этом рисунке изображено обозначение дешифратора, полная принципиальная схема которого приведена на рисунке 6.9.

Рисунок 6.10 – Условно-графическое обозначение двоично-десятичного дешифратора

Точно таким же образом можно получить принципиальную схему и для любого другого декодера (дешифратора). Наиболее распространены схемы восьмеричных и шестнадцатеричных дешифраторов. Для индикации такие дешифраторы в настоящее время практически не используются. В основном они используются как составная часть более сложных цифровых модулей.

Семисегментный дешифратор.

Для отображения десятичных и шестнадцатеричных цифр часто используется семисегментный индикатор. Внешний вид семисегментного индикатора и обозначение его сегментов приведено на рисунке 6.11.

Рисунок 6.11 – Внешний вид семисегментного индикатора и название его сегментов

Для отображения на таком индикаторе цифры 0 достаточно зажечь сегменты a, b, c, d, e, f. Для изображения цифры 1 зажигают сегменты b и c. Точно таким же образом можно получить изображения всех остальных десятичных или шестнадцатеричных цифр. Все комбинации двоичных кодов, позволяющих сформировать изображения цифр (и некоторых букв) получили название семисегментного кода.

Составим таблицу истинности дешифратора, который позволит преобразовывать двоичный (а точнее двоично-десятичный) код в семисегментный. Пусть сегменты индикатора зажигаются нулевым потенциалом. Тогда таблица истинности семисегментного дешифратора примет вид, приведенный в таблице 6.4. Конкретное значение сигналов на выходе дешифратора зависит от схемы подключения сегментов индикатора к выходу микросхемы. Эти схемы будут рассмотрены позднее, в главе, посвящённой отображению различных видов информации.

Таблица 6.4 – Таблица истинности семисегментного декодера.

|

Входы |

Выходы |

|||||||||

№ комбинации |

8 |

4 |

2 |

1 |

a |

b |

c |

d |

e |

f |

g |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

4 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

5 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

6 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

7 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

9 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

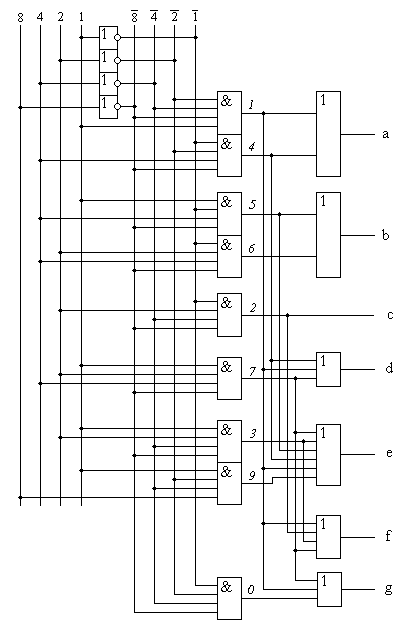

В соответствии с принципами построения схемы по произвольной таблице истинности реализуем принципиальную схему семисегментного декодера, работающую в соответствии с таблицей истинности, записанной в таблице 6.4. На этот раз не будем подробно расписывать процесс разработки схемы. Для проверки того, как вы разобрались в алгоритме разработки цифровых схем, попробуйте самостоятельно получить эту схему. Полученная в результате такого синтеза принципиальная схема семисегментного дешифратора приведена на рисунке 6.12.

Для облегчения понимания принципов работы приведённой на рисунке 6.12 схемы на выходе логических элементов "И" показаны номера строк таблицы истинности, реализуемые ими. Например, на выходе сегмента ‘a’ логическая единица появится только при подаче на вход комбинации двоичных сигналов 0001 (1) и 0100 (4). Это осуществляется объединением соответствующих цепей элементом "2ИЛИ". На выходе сегмента ‘b’ логическая единица появится только при подаче на вход комбинации двоичных сигналов 0101 (5) и 0110 (6), и так далее.

Рисунок 6.12 – Принципиальная схема семисегментного дешифратора

В настоящее время семисегментные дешифраторы выпускаются в виде отдельных микросхем или используются в виде готовых блоков в составе других микросхем. Условно-графическое обозначение микросхемы семисегментного дешифратора приведено на рисунке 6.13.

Рисунок 6.13 – Условно-графическое обозначение семисегментного дешифратора

В качестве примера семисегментных дешифраторов можно назвать такие микросхемы отечественного производства как К176ИД3. Они предназначены для подключения газоразрядных индикаторов. В современных цифровых схемах семисегментные дешифраторы обычно входят в состав больших интегральных схем.