- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

Законы отрицания.

Закон дополнительных элементов:

х+х=1

х*х=0

Двойное отрицание:

![]()

![]()

![]()

![]()

Выражения этих законов широко используется для минимизации логических схем. Если удаётся выделить из общего выражения логической функции такие подвыражения, то можно сократить необходимое количество входов элементов цифровой схемы, а иногда и вообще свести всё выражение к логической константе.

Закон отрицательной логики:

![]()

![]()

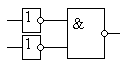

Закон отрицательной логики справедлив для любого числа переменных. Этот закон позволяет реализовывать логическую функцию "И" при помощи логических элементов "ИЛИ "и наоборот: реализовывать логическую функцию "ИЛИ" при помощи логических элементов "И". Это особенно полезно в ТТЛ схемотехнике, так как там легко реализовать логические элементы "И", но при этом достаточно сложно реализуются логические элементы "ИЛИ". Благодаря закону отрицательной логики можно достаточно просто реализовывать элементы "ИЛИ" на логических элементах "И". На рисунке 6.3 показана реализация логического элемента "2ИЛИ" на элементе "2И-НЕ" и двух инверторах.

Рисунок 6.3 – Логический элемент "2ИЛИ", реализованный

на элементе "2И-НЕ"

То же самое можно сказать и о схеме монтажного "ИЛИ". В случае необходимости его можно превратить в монтажное "И", применив инверторы на входе и выходе этой схемы.

Комбинационные законы.

Комбинационные законы алгебры логики во многом соответствуют комбинационным законам обычной алгебры, но есть и отличия.

Закон тавтологии (многократное повторение):

![]()

![]()

Применение этого закона зависит от цели. Его можно использовать для минимизации схемы, если такое выражение получается в результате преобразований исходного логического выражения.

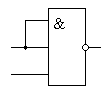

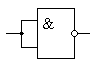

Этот же закон позволяет использовать логические элементы с большим количеством входов в качестве элементов с меньшим количеством входов. Например, можно реализовать двухвходовую схему "2И" на элементе "3И", как это показано на рисунке 6.4. или использовать схему "2И‑НЕ" в качестве обычного инвертора, как это показано на рисунке 6.5.

Рисунок 6.4 – Схема "2И-НЕ", реализованная на элементе "3И-НЕ"

Рисунок 6.5. – Схема "НЕ", реализованная на элементе "2И-НЕ"

Однако следует предупредить, что объединение нескольких входов увеличивает входные токи логического элемента и его ёмкость, что увеличивает ток потребления предыдущих элементов и отрицательно сказывается на быстродействии цифровой схемы в целом.

Для уменьшения числа входов в логическом элементе лучше воспользоваться законом одинарных элементов, как это было показано выше.

Закон переместительности.

a+b+c+d = a+c+b+d

В случае применения этого закона можно сократить площадь печатной платы за счет того, что в ряде случаев можно одни выводы логического элемента заменить на другие. В результате можно избежать переходов на другой слой или сократить длину проводников.

Закон сочетательности.

a+b+c+d = a+(b+c)+d = a+b+(c+d)

Этот закон позволяет составлять многовходовые логические элементы из логических элементов с меньшим количеством входов. Причем комбинации элементов могут быть самыми разнообразными

Закон распределительности.

х1(х2+ х3)= х1 х2 + х1 х3

х1 + х2 х3 =(х1+х2) (х1+х3)

Докажем это выражение:

(х1+х2) (х1+х3)=х1х1+х1х3+х1х2+х2 х3=

= х1 (1+ х3 + х2)+ х2х3 = х1+х2х3