- •Схемотехника цифровых устройств Учебное пособие Новосибирск

- •Кафедра сапр

- •Введение

- •1 Параметры цифровых микросхем

- •1.1 Уровни логического нуля и единицы

- •1.2 Входные и выходные токи цифровых микросхем

- •1.3 Параметры, определяющие быстродействие цифровых микросхем

- •1.4 Описание логической функции цифровых схем

- •2 Основные логические функции и элементы

- •2.1 Функция "не", инвертор

- •2.2 Функция "и", логическое умножение

- •2.3 Функция "или", логическое сложение

- •3 Основные схемотехнические решения цифровых микросхем

- •Диодно-транзисторная логика (дтл);

- •3.1 Диодно-транзисторная логика (дтл)

- •3.2 Транзисторно-транзисторная логика (ттл)

- •3.3 Логика на комплементарных моп транзисторах (кмдп)

- •4 Согласование цифровых микросхем между собой

- •4.1 Согласование микросхем из различных серий между собой

- •Согласование 3- и 5- вольтовых ттл микросхем.

- •Согласование 3- вольтовых ттл микросхем и 2,5- вольтовых кмоп микросхем.

- •4.2 Регенерация цифрового сигнала

- •5 Арифметические основы цифровой техники

- •5.1 Системы счисления

- •5.2 Преобразование чисел из одной системы счисления в другую

- •6 Комбинационные цифровые схемы

- •6.1 Законы алгебры логики

- •Закон одинарных элементов.

- •Законы отрицания.

- •Комбинационные законы.

- •Закон тавтологии (многократное повторение):

- •Правило поглощения.

- •Правило склеивания.

- •6.2 Построение цифровой схемы по произвольной таблице истинности

- •6.3 Декодеры

- •6.4 Шифраторы

- •Универсального кодера.

- •6.5 Мультиплексоры

- •6.6 Демультиплексоры

- •7 Генераторы

- •7.1 Усилительные параметры кмоп инвертора

- •7.2 Осцилляторные схемы

- •7.3 Мультивибраторы

- •7.4 Особенности кварцевой стабилизации частоты генераторов

- •7.5 Одновибраторы

- •8 Цифровые схемы последовательностного типа

- •8.1 Триггеры

- •8.2 Регистры

- •8.3 Счётчики

- •9 Индикаторы

- •9.1 Малогабаритные лампочки накаливания

- •9.2 Газоразрядные лампы

- •9.3 Светодиодные индикаторы

- •9.4. Динамическая индикация

- •9.5 Жидкокристаллические индикаторы

- •10 Разработка цифрового устройства на примере электронных часов

- •10.1 Разработка структурной схемы часов

- •10.2 Разработка принципиальной схемы часов

- •11 Синхронные последовательные порты

- •11.1 Ssi интерфейс (dsp порт)

- •11.2 Spi порт

- •11.3 I2с порт

- •12 Синтезаторы частоты

- •12.1 Схемы фазовой подстройки частоты

- •12.2 Схемы определения ошибки по частоте

- •12.3 Умножители частоты

- •12.4 Частотные детекторы, построенные на основе фапч

- •13 Цифровая обработка сигналов

- •13.1 Структурная схема цифрового устройства обработки сигнала

- •13.2 Особенности аналого-цифрового и цифро-аналогового преобразования

- •Критерии дискретизации по котельникову

- •Погрешность хранения

- •Погрешность выборки

- •Погрешность временного положение стробирующего импульса

- •13.3 Фильтры для устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •13.4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •13.5 Статическая передаточная функция ацп и цап и погрешности по постоянному току

- •13.6 Погрешности преобразования переменного тока

- •Искажения и шум в идеальном n-разрядном ацп

- •14 Виды аналого-цифровых преобразователей

- •14.1 Параллельные ацп

- •14.2 Последовательно-параллельные ацп

- •14.3 Ацп последовательного приближения

- •15 Основные блоки микросхем цифровой обработки сигналов

- •15.1 Двоичные сумматоры

- •15.2 Цифровые умножители

- •15.3 Постоянные запоминающие устройства

- •15.4 Статические оперативные запоминающие устройства (озу)

- •15.5 Цифровые фильтры

- •16 Реализация передатчиков радиосигналов в цифровом виде

- •16.1 Генераторы с цифровым управлением (nco)

- •16.2 Микросхемы прямого цифрового синтеза (dds)

- •16.3 Квадратурные модуляторы (Up converter)

- •16.4 Интерполирующие цифровые фильтры

- •17 Реализация радиоприёмников в цифровом виде

- •17.1 Цифровые преобразователи частоты

- •17.2 Цифровой квадратурный демодулятор

- •17.3 Децимирующие фильтры

- •Список литературы

- •Часть 1. Учебное пособие. Новосибирск , 2006.

- •630102, Новосибирск, ул. Кирова, 86.

3.3 Логика на комплементарных моп транзисторах (кмдп)

Микросхемы на комплементарных парах транзисторов строятся на основе МОП транзисторов с n- и p-каналами. В этих схемах один и тот же потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом.

Простейший логический КМОП элемент – это инвертор. Его схема приведена на рисунке 3.15. При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через микросхему не протекает. При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток через микросхему не протекает.

Рисунок 3.15 – Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах

На схеме, приведённой на рисунке 3.15, для упрощения понимания принципов работы микросхемы, не показаны защитные и «паразитные» диоды. Особенностью микросхем на комплементарных МОП транзисторах является то, что эти микросхемы в статическом режиме практически не потребляют ток.

Потребление тока происходит только в момент переключения микросхемы из единичного состояния в нулевое и наоборот. Этим током перезаряжается паразитная ёмкость нагрузки цифровой микросхемы.

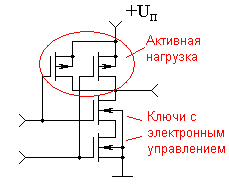

Схема логического элемента "И-НЕ" на КМОП микросхемах практически совпадает с эквивалентной схемой логического элемента "И" на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Это приводит к инверсии сигнала на выходе логического элемента. Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах приведена на рисунке 3.16.

В этой схеме можно было бы применить в верхнем плече обыкновенный резистор, однако при формировании напряжения низкого уровня схема постоянно потребляла бы ток. Вместо этого, в приведённой на рисунке 3.16 схеме, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе логического элемента требуется сформировать высокий потенциал, то нагрузочные p‑МОП транзисторы открываются, а если низкий – то закрываются.

Рисунок 3.16 – Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах

В приведённой на рисунке 3.16 схеме ток от источника питания на выход микросхемы будет поступать через один из транзисторов нагрузки, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты, ток от источника питания поступать не будет, и на выходе микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме инвертора, приведённой на рисунке 3.15, если хотя бы один из транзисторов верхнего плеча будет открыт, то соответствующий транзистор нижнего плеча будет тоже закрыт. Поэтому в статическом состоянии ток от источника питания логическим элементом потребляться не будет.

Условно-графическое изображение такого логического элемента показано на рисунке 3.5, а его таблица истинности приведена в таблице 3.1. В таблице 3.1 входы обозначены как x1 и x2, а выход – F.

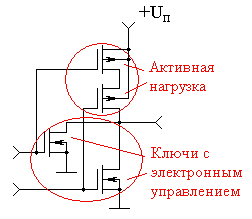

Логический элемент "ИЛИ-НЕ", выполненный на КМОП транзисторах, представляет собой параллельное соединение ключей с электронным управлением. Отличие от схемы "2ИЛИ", рассмотренной ранее, заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Это приводит к инверсии выходного сигнала. Вместо резистора в качестве нагрузки используются p-МОП транзисторы. Принципиальная схема элемента "2ИЛИ-НЕ", выполненного на комплементарных МОП транзисторах приведена на рисунке 3.17.

Рисунок 3.17 – Принципиальная схема элемента "2ИЛИ-НЕ", выполненного на комплементарных МОП транзисторах

В схеме логического элемента "2ИЛИ-НЕ" в качестве нагрузки используются последовательно включенные p-МОП транзисторы. В ней ток от источника питания будет поступать на выход микросхемы, только если все транзисторы в верхнем плече будут открыты, т.е. если сразу на всех входах будет присутствовать низкий потенциал (уровень логического нуля). Если же хотя бы на одном из входов будет присутствовать уровень логической единицы, то верхнее плечо будет закрыто, и ток от источника питания поступать на выход микросхемы не будет.

Таблица истинности, реализуемая схемой, приведенной на рисунке 3.17, соответствует таблице 3.2, а условно-графическое обозначение этого элемента приведено на рисунке 3.7.

В настоящее время именно КМОП микросхемы получили наибольшее развитие. Причём наблюдается постоянная тенденция к снижению напряжения питания этих микросхем. Первые серии КМОП микросхем, такие как К1561 (зарубежный аналог C4000В) обладали достаточно широким диапазоном изменения напряжения питания (3..18В). При понижении напряжения питания у конкретной КМОП микросхемы понижается её предельная частота работы и наоборот (на этом явлении основан так называемый разгон современных центральных процессоров персональных компьютеров). В дальнейшем, по мере совершенствования технологии производства, появились улучшенные КМОП микросхемы с лучшими частотными свойствами. Однако для этого потребовались транзисторы с меньшими линейными размерами, что привело к меньшим допустимым напряжениям питания.

Особенности применения КМОП микросхем.

Первой и основной особенностью КМОП микросхем является большое входное сопротивление этих микросхем. В результате на вход этой цифровой микросхемы может наводиться любое паразитное напряжение, в том числе и равное половине напряжения питания, и храниться на нём достаточно долго.

При подаче на вход КМОП микросхемы половины напряжения питания открываются транзисторы, как в верхнем, так и в нижнем плече выходного каскада микросхемы, в результате микросхема начинает потреблять недопустимо большой ток и в результате может выйти из строя. Поэтому входы цифровых КМОП микросхем ни в коем случае нельзя оставлять неподключенными.

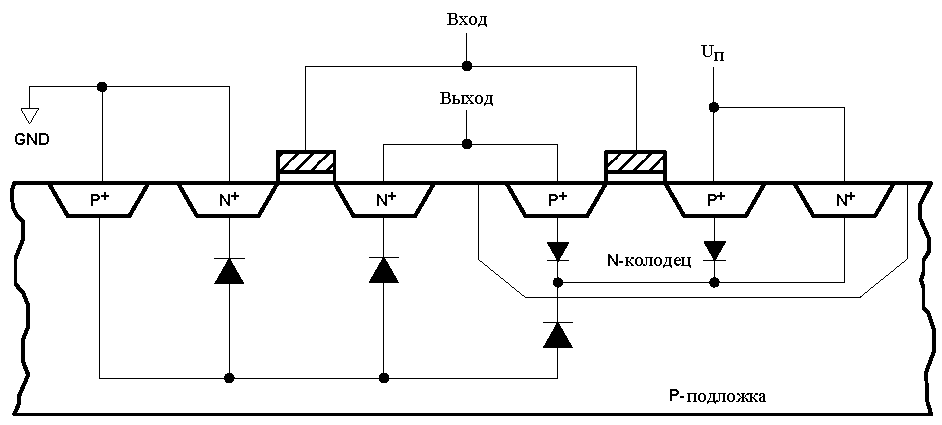

Второй особенностью КМОП микросхем является то, что они могут работать при отключенном питании (если подавать на входы этих микросхем логические сигналы). Однако работают они в таком режиме чаще всего неправильно. Эта особенность связана с конструкцией входного каскада КМОП микросхем. Конструкция КМОП инвертора приведена на рисунке 3.18, а полная схема КМОП инвертора с учетом защитных и паразитных диодов приведена на рисунке 3.19.

Рисунок 3.18 – Конструкция КМОП инвертора

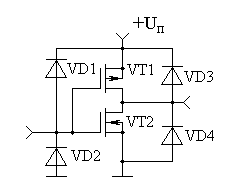

Рисунок 3.19 – Полная схема КМОП инвертора.

К сожалению, каждое преимущество КМОП микросхем при определённых условиях может оказаться недостатком. Так как сопротивление изоляции затвора МОП транзистора очень велико, то на затворе может наводиться очень высокий статический потенциал. Этим потенциалом изоляция затвора транзистора может быть пробита. Поэтому для защиты входного каскада от пробоя статическим электричеством в схему базового элемента были введены диоды VD1 и VD2. Это приводит к тому, что при подаче на вход микросхемы высокого потенциала он через диод VD1 попадёт на шину питания микросхемы, и так как КМОП микросхема потребляет достаточно малый ток, то она начнёт работать. Однако в ряде случаев тока для надёжной работы схемы может не хватить. В результате микросхема может работать неправильно. Вывод: при неправильной работе микросхемы тщательно проверьте питание микросхемы, особенно выводы корпуса. При плохо пропаянном выводе корпуса микросхемы его потенциал будет отличаться от потенциала общего провода схемы.

Третья особенность работы КМОП микросхем связана с существованием паразитных диодов VD3 и VD4 (см. рисунок 3.19). Эти диоды, при неправильно подключенном источнике питания, могут быть пробиты (микросхемы ТТЛ выдерживают кратковременную переполюсовку питания). Для защиты микросхем от переполюсовки питания следует в цепи питания предусмотреть защитный диод. Это относится и к ТТЛ микросхемам.

Четвёртая особенность КМОП микросхем – это протекание импульсного тока по цепи питания при переключении микросхемы из нулевого состояния в единичное и наоборот. В результате при замене ТТЛ микросхем на аналогичные КМОП микросхемы резко увеличивается уровень помех. В ряде случаев это важно, и приходится отказываться от применения КМОП микросхем в пользу ТТЛ или BICMOS.

Ещё одно неприятное явление в КМОП микросхемах связано с паразитными структурами, образующимися в полупроводнике. Если внимательно посмотреть на рисунок 3.18, то можно увидеть, что между источником питания и корпусом образуется паразитная p‑n‑p+-n структура. При превышении напряжения на входе микросхемы над напряжением питания в n карман может инжектироваться достаточное количество дырок для того, чтобы этот n карман исчез. В результате через микросхему будет протекать ничем не ограниченный ток. Теперь уже этот ток будет инжектировать в n-карман дополнительные положительные заряды. Процесс становится неуправляемым и может быть прекращён только снятием напряжения питания. Это явление получило название защёлкивания. К подобному эффекту может привести подача на вход микросхемы отрицательного напряжения. Поэтому при проектировании схемы цифрового блока следует принимать меры для того, чтобы напряжение на входе микросхемы находилось в пределах от потенциала общего провода до напряжения питания.

Логические уровни КМОП микросхем.

Логические уровни КМОП микросхем существенно отличаются от логических уровней ТТЛ микросхем. При отсутствии тока нагрузки напряжение на выходе КМОП микросхемы совпадает с напряжением питания (логический уровень единицы) или с потенциалом общего провода (логический уровень нуля). При увеличении тока нагрузки напряжение логической единицы может уменьшаться до двух третьих от напряжения питания.

Для современных КМОП микросхем требования по логическим уровням более жесткие. Допустимый уровень напряжения на выходе цифровой КМОП микросхемы серии SN74HC при пятивольтовом питании показан на рисунке 3.20.

Рисунок 3.20 – Уровни логических сигналов на выходе цифровых КМОП микросхем

Как уже отмечалось ранее, изменение напряжения на входе цифровой микросхемы по сравнению с выходом обычно допускается в больших пределах. Для КМОП микросхем определен 30% запас по напряжению. Границы уровней логического нуля и единицы для КМОП микросхем при пятивольтовом питании приведены на рисунке 3.21.

Рисунок 3.21 – Уровни логических сигналов на входе цифровых КМОП микросхем

При уменьшении напряжения питания, границы логического нуля и логической единицы можно определить точно так же, как и на рисунке 3.21 (разделить напряжение питания на 3).

Семейства КМОП микросхем.

Первые КМОП микросхемы не имели защитных диодов на входе, поэтому их монтаж представлял значительные трудности. Затворы МОП транзисторов при монтаже часто пробивались статическим электричеством. Это семейство цифровых микросхем серии К172. В следующем, улучшенном семействе микросхем серии К176 были включены защитные диоды. Эти микросхемы достаточно распространены и в настоящее время. Серия К1561 завершает развитие первого поколения КМОП микросхем. В этом семействе было достигнуто быстродействие микросхем на уровне 90нс и диапазон изменения напряжения питания 3..15В. Зарубежный аналог этих микросхем – C4000В.

Дальнейшим развитием КМОП микросхем стала серия SN74HC. Эти микросхемы отечественного аналога не имеют. Они обладают быстродействием 27нс и могут работать в диапазоне напряжений 2..6В. Эти микросхемы совпадают по конструктивному исполнению и функциональному ряду с ТТЛ микросхемами, но не совместимы с ними по логическим уровням, поэтому одновременно были разработаны микросхемы серии SN74HCT (отечественный аналог – К1564), совместимые с ТТЛ микросхемами и по логическим уровням.

В это время в радиоэлектронной аппаратуре наметился переход на трёхвольтовое питание. Для него были разработаны микросхемы SN74ALVC с временем задержки сигнала 5,5 нс и диапазоном питания 1,65…3,6 В. Эти же микросхемы способны работать и при 2,5- вольтовом питании. Время задержки сигнала при таком напряжении питания увеличивается до 9 нс.

В настоящее время наиболее перспективным семейством КМОП микросхем считается семейство SN74AUC с временем задержки сигнала 1,9 нс и диапазоном напряжения питания 0,8…2,7 В.