ОРГАНИЗАЦИЯ ВВОДА – ВЫВОДА.

В большинстве применений наряду с вычислительными возможностями и экономическими показателями МПС большое значение имеют её средства обмена информации с разнообразными периферийными устройствами. Эти средства образуют подсистему ВВ, включающую в себя аппаратные и программные средства интерфейса с периферийными устройствами, а также информацию, участвующую в обмене. При анализе подсистемы ВВ необходимо рассмотреть способы организации ВВ, форматы команд и данных, структуру шин, наличие прерываний, способа доступа к памяти и временные соотношения ВВ.

Широкое распространение МПС заставило несколько расширить содержание понятия периферийного устройства. Традиционные периферийные устройства ЭВМ широкого назначения представляются как нечто что то громоздкое , сложное, дорогое и сравнительно медленно действующее оборудование. В настоящее время под периферийным устройством понимают любое цифровое устройство, которое может обмениваться информацией с МПС: разнообразные счетчики, индикаторы, клавиатура, цифровые датчики, преобразователи форм представления информации и др.

Анализ подсистемы ВВ осложняется тем обстоятельством, что в каждом МП семействе применяются уникальная организация ВВ, различные конфигурации схем и и типы устройств. Однако можно выделить некоторые общие принципы, характерные для большинства МПС:

Обмен ведется отдельными битами (последовательный интерфейс), либо полными словами данных (параллельный интерфейс);

Действия по обмену информацией обычно синхронизуются от системного генератора синхронизации.

При подключении к системе нескольких периферийных устройств МП должен генерировать специальный сигнал выбора периферийного устройства.

Медленные периферийные устройства обмениваются информацией по мере ее готовности.

Быстрые периферийные устройства обмениваются непосредственно с памятью без участия МП.

Между МП периферийными устройствами передаётся информация двух видов:

А) Управляющие данные

Б) Собственно данные (информационные сообщения)

Управляющие данные от системы, инициирующие действия, связанные с обменом данных называются приказами (управляющими словами, командными словами, командами).

Управляющие данные от периферийных устройств называются словами состояния (управления).

Каждый юит слова состояния сигнализирует от определенной ситуации, сложившейся в устройстве, например, о готовности устройства к обмену данными, об возникновении ошибки при передачи и др.

Состояние периферийного устройства в больших вычислительных системах представляется байтом состояния, а для МПС обычно достаточно одного бита, называемого битом (флажком) готовности. Если он содержит 1, то устройство готово к обмену, а если 0 – устройство не может участвовать в обмене, например оно выключено, занято выполнением предыдущей операции.

Разработка аппаратных средств и программирование УВВ представляет собой наиболее сложный и трудоемкий этап проектирования МПС.

А) Общая организация ввода-вывода

Для МПС разработано три основные режима ввода-вывода:

Программно-управляемый (нефорсированный) ВВ означает, что все действия по обмену информацией инициируются прикладной программой, а периферийным устройствам отводиться пассивная роль сигнализации о своей готовности к обмену.

Сначала необходимо считать и проанализировать акт готовности устройства и если оно не готовок обмену, система должна ожидать, не выполняя полезных функций. Непроизводительные потери времени на ожидания могут оказаться неприемлемыми для систем, работающих в реальном времени.

ВВ по прерываниям, называемый также форсированным ВВ, подразумевает, что действия по обмену информацией инициируют сами периферийные устройства, генерируя сигналы прерывания или запросов а обслуживания. При восприятии сигнала прерывания МП приостанавливает выполнение текущей программы, временно запоминает состояние (как минимум запоминается PSW и PC), идентифицирует прерывающее устройство и осуществляет обмен информацией.

После завершения обмена восстанавливается состояние прерванной программы и возобновляется ее дальнейшее выполнение. В данном режиме на ВВ расходуется гораздо меньше времени МП, чем в программно-управляемом ВВ, поэтому система может выполнить больше полезной работы или обслужить больше периферийных устройств.

Отметим, что в обоих рассмотренных режимах непосредственное управление ВВ осуществляет МП.

Некоторые периферийные устройств, чаще всего устройства внешней памяти имеют такую большую скорость передачи, что пропускной способности МП даже в режиме ВВ по прерываниям недостаточно. Интерфейс с такими устройствами реализуется в режиме ПДП. В этом режиме на время передачи действия МП приостанавливаются и он отключается от ША и ШД. Инициирование и управление обменом информацией между периферийными устройствами и системой памятью осуществляет контроллер ПДП.

Информация между МПС и периферийными устройствами передается по линиям D7-D0 ШД. Подключение периферийных устройств к ШД осуществляется через порты ВВ, которые становятся неотъемлемой частью устройства. Между портами ВВ и устройствами могут включаться буферные согласующие схемы, характеристики которых определяются особенностям каждого устройства.

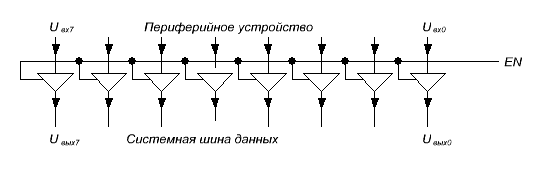

Параллельный порт ввода

Параллельный порт ввода имеет 8 тристабильных буферов, управляемых (стробируемых) H-активным сигналом разрешения EN. Если на линии EN действует H-уровень, выходные сигналы порта повторяют логические уровни на входах и вводимое слово передается на шину данных. Если на линии EN действует L-уровень, тристабильные буферы переводятся в высокоимпедансное состояние и периферийное устройство отключается от шины данных.

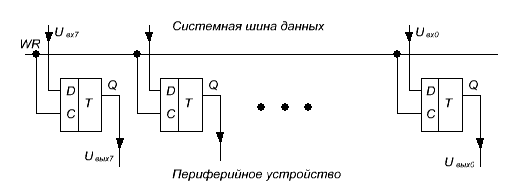

Параллельный порт вывода организован на D-триггерах, т. к. сигналы выводимых сигналов действуют на ШД в течение короткого временног интервала. Управляющий сигнал записи WR подается на входы синхронизации C всех триггеров.

Параллельный порт вывода

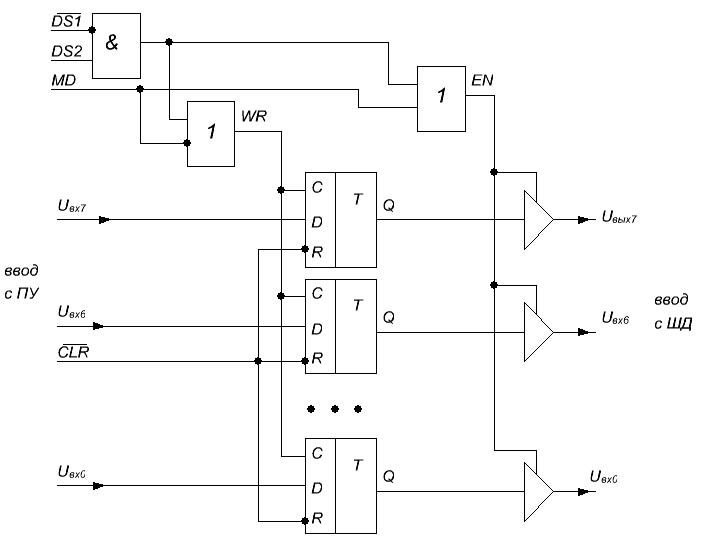

Широкое распространение получили микросхемы универсальных портов ВВ, которые в зависимости от значения управляющего сигнала задания режима могут работать как порт ввода или порт вывода.

Универсальный порт вывода

Для организации порта ввода входы Uвх7-0 подключаются к выходным линиям ПУ, выходы Uвых7-0 к системной шине данных, а на вход МД подается L-уровень. Сигнал WR=1 и D-триггеры оказываются прозрачными для входных данных. Стробирование тристабильных буферов осуществляется при совпадении L-уровня на линии DS1# и H-уровня на DS2.

Режим порта вывода достигается при подключении входов Uвх7-0 к системной ШД, выходов Uвых7-0 – к выходным линиям ПУ и подаче на вход MD H-уровня. В данной конфигурации EN=1 и тристабильные буферы постоянно разрешены. Запись в D-триггеры производиться при совпадении DS1#=0 и DS2=1. L-активный сигнал сброса CLR приводит все триггеры регистра в нулевое состояние. Сброс портов вывода выполняется в процессе инициализации МПС до включения периферийных устройств, иначе непредсказуемое начальное содержание порта может нарушить правильную работу подключенного к нему устройства.

В МПС применяются два основных способа ВВ.

Изолированный (или аккумуляторный) (IBM PC)

Отображенный на память (MAC)

Отличающиеся адресацией и выбором портов ВВ.

Система команд МП К580 с изолированным ВВ включает в себя двухбайтные команды ввода IN и вывода OUT, в которых второй байт <B2> представляет собой адрес порта ввода или вывода. Следовательно, общее число портов ВВ в отдельности не превышает 256, а адреса их изолированы от адресного пространства памяти. При выполнении команда IN данные из адресуемого порта ввода загружаются в A, а команда OUT записывает содержимое А в адресуемый порт ввода-вывода. Управляющие сигналы I/OR# и I/OW#, генерируемые в цикле М3 команд IN и OUT, определяют момент и направление передачи данных.

ВВ с отображением на память не требуют специальных команд и управляющих сигналов, предназначенных для ВВ. Порты ВВ считаются ячейками адресного пространства памяти, и все команды с обращением к памяти, содержащие адреса портов, превращаются в команды ВВ: команды загрузки осуществляют ввод, а команды запоминания – вывод. Момент выполнения собственно ввода и вывода определяют соответственно сигналы MEMR# и MEMR#.

При анализе обоих способов ВВ оказывается, что ни один из них не имеет явных преимуществ, перед другим, однако ВВ с отображением на память считается более гибким и универсальным. К его достоинствам относиться большой набор команд для ВВ, почти неограниченное число портов ВВ и отсутствие специальных управляющих сигналов.

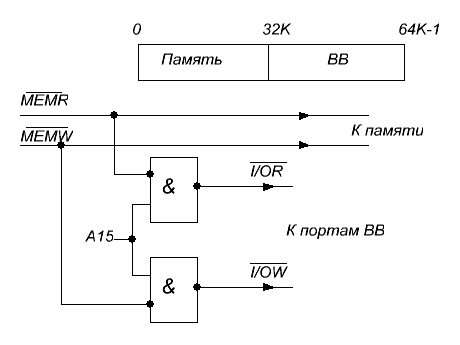

При необходимости, в МПС на базе МП К580 несложно реализовать ВВ с отображением на память. В общем случае портам ВВ присваиваются 16-битные адреса и вводятся соответствующие схемы дешифрации. Если в МПС достаточно памяти емкостью 32Кбайт, адресное пространство удобно разделить на 2 области:

Памяти с адресами от 0 (32К-1)

ВВ с адресами от 32К до (64К-1)

Другими словами, эти области отличаются значениями старшего бита A15:

A15: 0 – область памяти

1 – область ВВ

Формирование сигналов I/OR# и I/OW# осуществляется так:

Формирование сигналов I/OR# и I/OW#

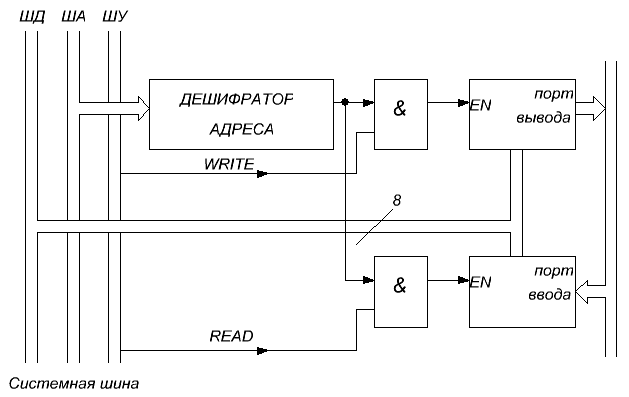

Подключение порта в схеме прямого ввода/вывода

Дешифратор адреса в общем случае представляет 8-входную схему сравнения в изолированном ВВ или 16-входную схему сравнения при организации ВВ с отображения на память. Дешифратор формирует активный выходной сигнал, когда на ША действует сигналы адреса данного порта ввода или вывода.

При совпадении выходного сигнала дешифратора и управляющего сигнала READ тристабильные буферы разрешены (EN-1) и вводимые данные от ПУ передаются на ШД. Отметим, что линией READ является линия MEMR# (ВВ с отображением на память).

Аналогично осуществляется подключение порта в схеме прямого вывода. Обозначенной на рисунке линией WRITE фактически является линия I/OW# или MEMW#.

Подключение порта в схеме прямого ввода

Подключение порта в схеме прямого вывода

Двунаправленный (комбинированный) вв

Фактически объединены рассмотренные выше схемы прямого ввода и вывода. Заметим, что наличие одного дешифратора адреса свидетельствует о том, что адреса портов ввода и вывода одинаковые. Данный интерфейс применяется в ПУ типа пишущей машинки, которые могут выполнить операции ввода и вывода.

В приведенных схемах прямого ВВ дешифратор адреса должен реагировать на полный адрес и иметь соответствующее число входов. Специализированные МПС обычно имеют небольшое число ПУ и схему дешифратора адреса можно упростить. Пусть, например, в МПС достаточно 8 портов вывода и 8 порто в ввода. Тогда для адресации портов ВВ целесообразно применить код 1-38 с шеснадцатиричными адресами 01, 02, 04, …, 80. При таком кодировании адресов для выбора порта необходимо анализировать состояние только одной линии адреса, а отдельная линия дешифратора становиться не нужной. Рассмотренная схема адресации называется адресацией с линейным выбором.

Линейный выбор можно реализовать и в МПС, в которых применяется метод ВВ с отображением на память. Если, например, области памяти и ВВ различаются значением старшего бита A15 адреса, то в оставшихся битах для адресации портов ВВ следует применять код 1-из-15.

Отметим, что двухходовая схема совпадения встроена в схему универсального порта ВВ. На вход DS1# подается L-активный сигнал считывания или записи, а на вход DS2 подключается выход дешифратора адреса. В МПС с линейным выбором универсальный порт подключается к системной шине без дополнительных схем дешифрирования.

Комбинированный ввод вывод

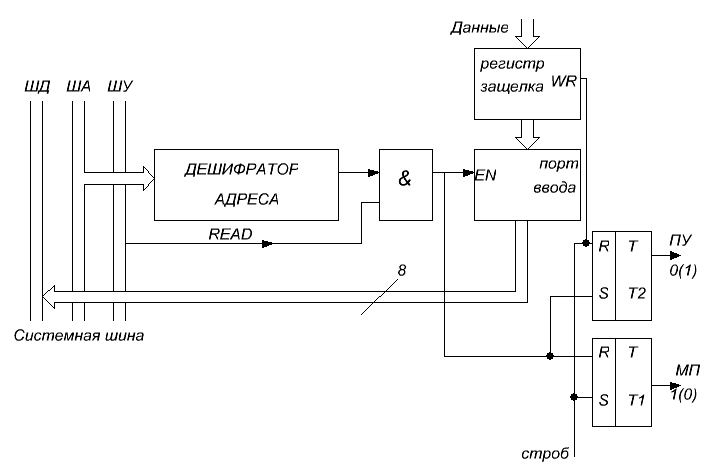

Стробируемый вв (вв с прерываниями)

В схеме стробируемого ввода входные данные от ПУ сопровождаются стробом (коротким импульсным сигналом) ввода. Строб загружает данные во входной регистр-защелку и устанавливает триггер Т1, единичный выход которого сигнализирует МП о наличие данных. Когда МП осуществляет ввод и генерируется сигнал READ, содержимое регистра защелки через ШД загружается в А. Кроме того, сигнал READ устанавливает триггер Т2, единичный сигнал которого подтверждает устройству ввода восприятие данных и сбрасывает триггер Т1.

Прямой выход триггера Т1 соединяется со входом прерывания МП и практически представляет собой бит готовности устройства ввода.

Стробированный ввод

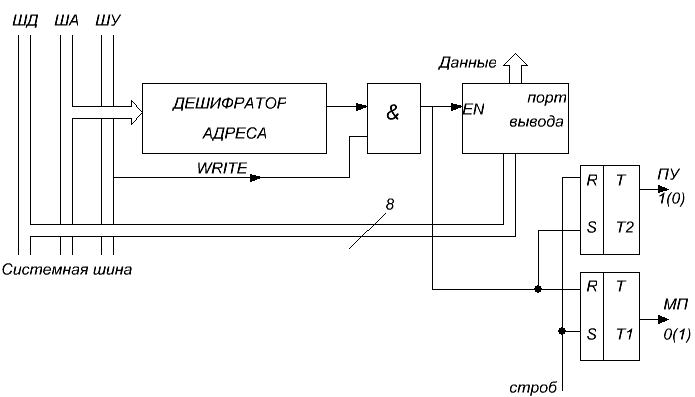

Аналогично реализуется стробируемый вывод.

Стробированный вывод

Когда МП записывает данные в порт вывода, устанавливается триггер Т2 и генерируется сигнал для устройства вывода о необходимости приема данных. Устройство воспринимает данные и подтверждает (квитирует) прием стробом, который сбрасывает триггер Т2 и устанавливает Т1.

Сигнал с выхода Т1 поступает на вход прерывания МП и извещает его о возможности вывода следующего слова данных. И в этой схеме состояние триггера Т1 представляет собой бит готовности устройства вывода.