- •Назначение системы

- •2. Описание лабораторной установки

- •2.1. Устройство и принцип работы составных частей лабораторной мпс

- •2.2. Общее описание структуры лабораторной мпс

- •2.3. Основные сведения о работе лабораторной мпс

- •3. Организация обмена информацией в микроЭвм

- •3.1. Описание микропроцессора кр 580 вм 80а

- •3.2. Слово состояния мп и системная шина управления

- •3.3. Извлечение кода команды, данных из памяти или внешнего устройства

- •3.4. Запись данных в память или внешнее устройство

- •3.5. Выполнение команд по циклам и программ по шагам

- •4. Работа с мпс

- •4.1. Описание клавиатуры

- •4.2. Описание функция системного монитора

- •4.2.1. Индикация и изменение содержимого памяти (п)

- •4.2.2. Индикация и изменение содержимого регистров (рг)

- •4.2.3. Передача управления программе пользователя (ст)

- •4.2.4. Определение контрольной суммы массива памяти (кс)

- •4.2.5. Заполнение массива памяти константой (зк)

- •4.2.6. Перенесение массива памяти в адресном пространстве (пм)

- •4.2.7. Прерывание выполнения программы

- •5. Программирование мпс

- •5.1. Язык Ассемблера микропроцессора кр 580 вм 80a

- •1. Группа команд однобайтовых пересылок

- •2. Группа команд двухбайтовых переделок

- •3. Группа команд ввода/вывода

- •4. Группа команд обмена байтами

- •После выполнения команды в а будет число

- •6. Группа команд арифметических и логических операций с двумя операндами

- •7. Команды сдвигов содержимого аккумулятора

- •8. Команды передачи управления и работы с подпрограммами

- •9. Специальные команды

- •5.2. Получение машинных кодов команд

3.3. Извлечение кода команды, данных из памяти или внешнего устройства

Выполнение любой команды состоит из выполнения определенного количества машинных циклов, характерных для этой команды, циклов может быть от 1 до 5.

Первым машинным циклом при выполнении любой команды всегда является цикл выбора команды, то есть чтения кода команды из памяти (табл. 3.1). Этот цикл имеет специальное обозначение М1.

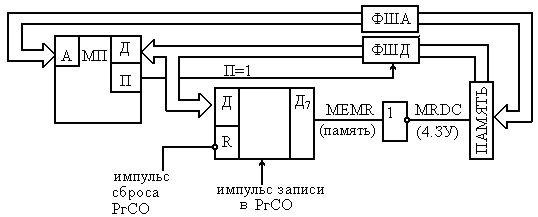

Схема чтения кода команды или данных из памяти показаны на рис. 3.3.

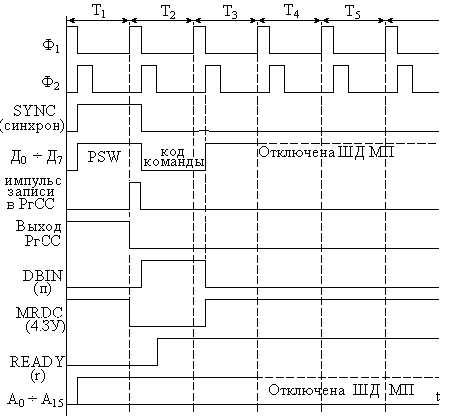

Цикл М1 является основным циклом. Его подробное рассмотрение дает представление о взаимодействии интерфейсных сигналов. Анализ процессов цикла М1 будем проводить по машинным тактам. Соответствующие временные диаграммы представлены на рис. 3.4.

На такте T1 программный счетчик PC в МП выдает на ША МП адрес ячейки памяти, из которой будет считываться код команды. При этом МП автоматически увеличивает на единицу значение числа, записанного в РС, но на ША будет сохраняться предыдущее значение счетчика PC до наступления следующего машинного цикла.

Рисунок 3.3 Схема чтения кода или данных из памяти.

Рисунок 3.4 - Временная диаграмма цикла М1 чтения кода команды из памяти

По положительному фронту импульса Ф2 формируется сигнал SYNC (СИНХР) и выдается слово состояния (PSW) на ШД МП. Сигнал DBIN(П) при этом равен нулю, что переключает двунаправленный формирователь ШД в направление передачи от МП в системную шину. Это гарантирует, что на входе PrСС присутствует именно слово состояния, в не какая-либо другая информация из системной ШД.

На

такте T2

формируется импульс записи в РгСС и

слово состояния записывается в регистр.

Одновременно с окончанием SYNC

формируется единичное значение сигнала

DBIN

(ПРИЕМ), переключающее двунаправленный

формирователь ШД в направление передачи

информации из системной ШД в МП.

Одновременно формируется сигнал

![]() (

(![]() ),

рис.3.3.

),

рис.3.3.

Поскольку адрес в памяти был установлен ранее, то по сигналу происходит считывание кода команды и передача его через ФШД в МП. На этом же такте Т2 анализируется состояние сигналов READYП (ГОТОВ), HOLDП(3.3x) и HLTACC (Об. ост.). Если к моменту появления отрицательного фронта Ф2 на такте Т2 не выполнится условие READYП=1, то МП на такте Т3 переходит в режим ожидания, в котором будет находиться до тех пор, пока на входе READYП не появится единичный сигнал.

В лабораторной установке это свойство используется для создания шагового режима исполнения команд.

На такте T3 в момент отрицательного фронта сигнала Ф1 производится запись кода команды в МП. Положительным фронтом Ф2 оканчивается сигнал DBIN(П), вырабатывается импульс сброса в 0 всех разрядов регистра РгСС и оканчивается сигнал ( ).

На тактах Т4 и Т5 происходит дешифрация кода команды. Отличие машинных циклов чтения данных из памяти, стека или ВУ по сравнению с циклом М1 заключается лишь в том, что МП будет воспринимать двоичные коды, выбираемые им из памяти не как коды команд, а как данные, сопутствующие этим кодам команд.

3.4. Запись данных в память или внешнее устройство

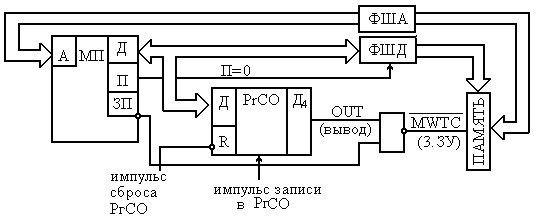

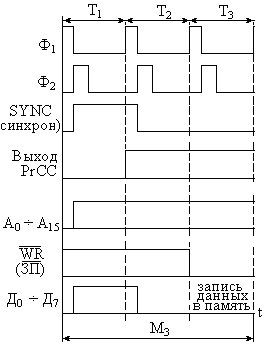

Процесс записи данных в память иллюстрируется на схеме, показанной на рис. 3.5 и временных диаграммах на рис. 3.6. Временные диаграммы описывают только цикл М3 записи в память. Сам цикл М3 входит в группу циклов, составляющих команду. Например: команда пересылки константы 01 в ячейку памяти описывается в условных обозначениях как

MVI M, 01

Эта команда выполняется за три цикла: М1, М2 и М3.

Во время этого цикла происходят следующие действия.

На такте Т1 по положительному фронту Ф2 программный счетчик PC в МП выдает на ША МП адрес ячейки памяти, в которую будет производиться запись данного, а на ШД МП присутствует код слова состояния (PSW).

На

такте T2

формируется импульс записи в РгСС и

слово состояния записывается в регистр.

По положительному фронту Ф2

оканчивается синхросигнал SYNC

(СИНХР), а на ШД МП двоичный код является

кодом

данных,

подлежащих записи в память.![]()

На

такте Т3

на выходе

![]() МП формируется сигнал с уровнем "0",

по которому будет проходить запись

данных в память. Из этого сигнала и

разряда Д4

ОUТ

(ВЫВОД) регистра РгСС формируется

сигнал

МП формируется сигнал с уровнем "0",

по которому будет проходить запись

данных в память. Из этого сигнала и

разряда Д4

ОUТ

(ВЫВОД) регистра РгСС формируется

сигнал![]() ,

разрешающий запись в память (рис.3.5).

Непосредственно запись кода данных в

память осуществляется по сигналу Ф2.

,

разрешающий запись в память (рис.3.5).

Непосредственно запись кода данных в

память осуществляется по сигналу Ф2.

На протяжении всего машинного цикла записи данных в память сигнал DBIN(П) МП находится в нулевом состоянии, что переключает двунаправленный формирователь ШД в направлении передачи МП в системную шину МПС.

Процесс

записи данных во внешнее устройство ВУ

аналогичен записи данных в память.

Отличие заключается в способе формирования

системного сигнала записи

![]() .

Как видно из уравнений 3.1

(3.1а),

в формировании этого сигнала участвует

инверсия сигнала разряда Д4

OUT

(ВЫВОД) регистра слова состояния РгСС.

.

Как видно из уравнений 3.1

(3.1а),

в формировании этого сигнала участвует

инверсия сигнала разряда Д4

OUT

(ВЫВОД) регистра слова состояния РгСС.

Рисунок 3.5 Схема записи данных в памяти.

Рисунок 3.6 - Временная диаграмма цикла М3 записи данных в память