- •Пояснительная записка к курсовой работе по дисциплине

- •Задание

- •Содержание

- •Введение

- •Выбор микропроцессора цос

- •2. Описание архитектуры процессора цос.

- •Многоканальный буферизованный последовательный порт (мкбпп).

- •3. Система команд

- •4. Разработка структурной схемы устройства

- •5. Периферия

- •Микроконтроллер мс68нс(7)11d3

- •Характеристики

- •6. Функциональная схема

- •3). Подключение внешней памяти к процессору цос

- •8. Операции ввода-вывода

- •Заключение

2. Описание архитектуры процессора цос.

Высокий уровень производительности процессоров семейства С5000 стал возможен благодаря их высокопроизводительной архитектуре, специально разработанной с учетом требований широкого круга приложений. Так. например. в состав ядра процессоров включен Витерби-ускоритель, который сокращает выполнение операции "butterfly update", применяемой в декодировании GSM канала, до 4-х команд процессора.

200-MIPS Двойное ядро DSP Состоящий из Два

Независимые Подсистемы

Каждое Ядро Имеет Расширенный Мультиавтобус

Архитектура С Тремя Отдельными 16 битами

Автобусы Памяти Данных и Один Автобус Программы

Арифметический Логический Модуль на 40 битов (ALU)

Включение Барреля-Shifter на 40 битов и

Два Сумматоры на 40 битов В Ядро

Каждое Ядро Имеет 17-ни Параллельных 17 битов

Множитель, соединенный к Змее на 40 битам для

Non-Pipelined Единственный цикл Умножают/

Накопите (MAC) Операции

Каждое Ядро Имеет Сравнивающийся. Выбирать, и

Модуль Склада(магазина) (CSSU) для Добавляющегося/Сравнивающегося

Выбор Viterbi Оператора

Каждое Ядро Имеет Кодирующее устройство Образца к

Вычислите Значение Образца 40 битов

Значение Сумматора в Единственном(отдельном) Цикле

Каждое Ядро Имеет Два Генератора Адреса

С Восьмью Вспомогательными Регистраторами и Два

Вспомогательные Модули Арифметики Регистра

(ARAUs)

Автобус Данных на 16 битов С Держателем Автобуса Данных

Особенность

256КБ ни 16 Расширенных(продленнь1х) Адресов Программы Место(космос)

Общее количество 200КБ ни 16 Двойной - и Единственного доступа ОПЕРАТИВНАЯ ПАМЯТЬ На-чипе

Повторение Единственной команды и

Операции Блока-повторения

Команды Со Словом 32 бита длиной

Операнды

Команды С 2 или 3 Чтениями Операнда

Быстро Возвращаются От Прерываний

Арифметические Команды С Параллельным Складом(магазином)

И Параллельная Загрузка

Условные Команды Склада(магазина)

Управление Вывода CLKOUT

Управление Вывода РЕКЛАМИРУЮТ

Управление Потребления Власти(мощи) С IDLE1,

IDLE2. и IDLE3 Команды

Двойное 1.8-V (Ядро) и 3.3-V (ввод - вывод) Власть(мощь)

Запасы(поставки) для Малой мощности. Быстрой Операции

10-ns Команда Устанавливаемого-пункта(-точки) Единственного цикла

Выполнение

Межпроцессорная Связь через Два

Внутренний FIFOs с 8 элементами 1

2 Каналов Прямого доступа к памяти

(DMA) для Передач данных Без ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Загрузка (6 Каналов В Подсистему)

Шесть Многоканальных Буферизированных Последовательных портов

(McBSPs) (Три McBSPs В Подсистему)

Интерфейс Ведущего порта на 16 битов (НРП6)

Мультиплексированный Со Внешним Интерфейсом Памяти

Штырьки

Программируемый по программному обеспечению Блокированный стадией

Петля (PLL) Обеспечивает Несколько Синхронизаций

Опции (Требуют Внешнего TTL Генератора)

Логика Эмуляции На основе просмотра На-чипе

Два Программируемых по программному обеспечению Таймера

( Один В Подсистему)

Программируемое по программному обеспечению Состояние ожидания

Генератор (14 Максимумов Состояний ожидания)

Обеспеченный в BGA Массиве Сетки Шара с 144 штырьками

( GGU Суффикс) и Тонкая Четверка с 144 штырьками

Плоский корпус (TQFP) (PGE Суффикс) пакеты

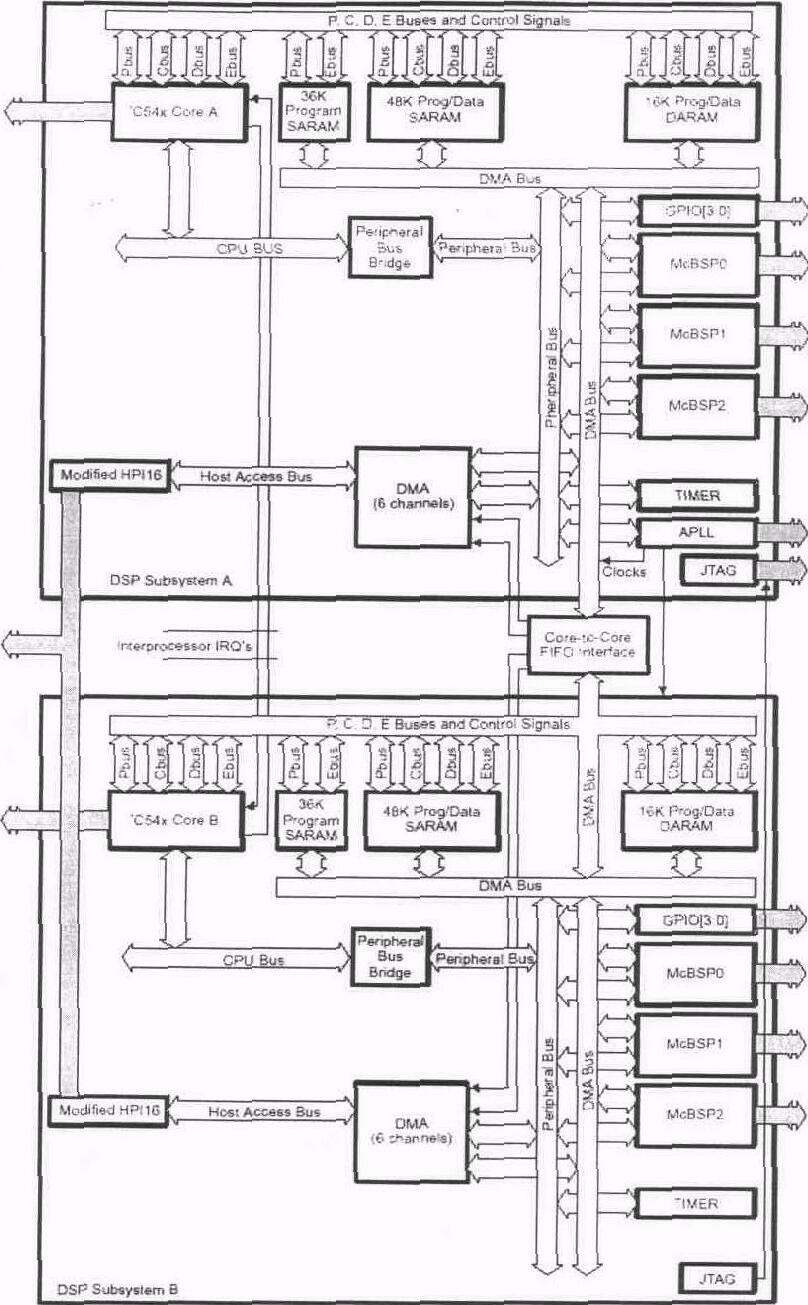

Рисунок

Подробнее о каждом из ядер процессора:

Другие важные особ енности архитектуры ядра С54ХХ таковы:

• Четыре внутренние шины и два генератора адреса позволяют параллельно выполнять операции с несколькими операндами и снижают критические параметры доступа к памяти.

• 40-разрядный сумматор и два 40-разрядных аккумулятора позволяют производить параллельную обработку инструкций в одном цикле команды.

• Второй дополнительный 40-разрядный аккумулятор на выходе умножителя позволяет выполнять неконвейерные MAC операции типа двух суммировании и умножения в параллель.

• Одноцикловая нормализация и экспоненциальное декодирование дает поддержку операций с плавающей точкой, которые часто используются при кодировании речи.

• Умножитель 17х17 разрядов позволяет выполнять 16-разрядное знаковое или беззнаковое умножение с округлением и контролем насыщения - и все это в одном командном цикле.

• Новые однотактовые команды эффективно выполняют общие ЦОС операции, такие как обработка звена симметричного КИХ фильтра.

• 40-разрядное АЛУ может работать в режиме двойного 16-разрядного, что позволяет выполнять двойные однотактовые операции.

Восемь дополнительных регистров и программный стек позволяют применить наиболее развитый и эффективный среди процессоров с плавающей точкой С-компилятор.

Семейство С5000 построено по модифицированной Гарвардской архитектуре. В нем используется 3 отдельных системы шин для данных и одна для команд. Разделение памяти команд и памяти данных позволяет выполнять одновременный доступ к командам и данным, что повышает параллелизм выполнения. Например, в одном цикле могут быть выполнены две операции чтения и одна операция записи. Команды с параллельной записью и специальные команды полностью используют все преимущества данной архитектуры. Кроме того, данные могут пересылаться между областями команд и данных. Такая степень параллелизма дает возможность поддерживать мощный набор арифметических, логических операций и операций с битами, которые выполняются за один машинный цикл. В дополнении к этому, ядро С54ХХ включает в себя эффективные механизмы управления прерываниями, повторения операций и вызовов подпрограмм.

Рисунок 2.1. Архитектура процессора.

Структура шин. Архитектура С54ХХ состоит из 8 основных шин:

• Одна шина чтения команд (РВ). которая предназначена для выборки команд и непосредственных операндов.

• Две шины чтения данных (СВ и DB) и одна шина записи данных (ЕВ). которые соединяют большинство элементов системы. Через шины СВ и DB операнды читаются из памяти данных, а через шину ЕВ - пишутся.

• Четыре адресных шины (РАВ, CAB, DAB и ЕАВ), на которые выставляются адреса, необходимые для выполнения команды.

Устройства С54ХХ имеют возможность генерации одновременно ло двух адресов данных, которые сохраняются в двух дополнительных регистрах (ARAUO и ARAU1).

Шина РВ может переносить операнд, хранимый в памяти программ (для примера, таблицу коэффициентов), на вход умножителя для выполнения операций умножения/суммирования или в область данных для операций передачи данных. Это дает возможность использовать однотактовые команды с тремя операндами.

Устройства С54ХХ также имеют внутреннюю двунаправленную шину для доступа к размещенной на кристалле периферии. Эта шина соединяется с шинами DB и ЕВ через мост.

Через этот же мост к внутренней структуре шин подключается и внешняя шина процессора, для интерфейса с внешней памятью и устройствами.

Доступ к устройствам через эту шину может требовать более чем двух тактов для чтения и записи - это зависит от внешнего устройства.

Устройства семейства С54ХХ имеют систему поддержки шины данных и шины адреса, исключающую на ней плавающие уровни в то время, когда шина находится в третьем состоянии.

Память. Полное адресуемое пространство для процессоров семейства С54хх составляет 192К 16-разрядных слов. Память делится на три сегмента по 64 К Слов:

сегмент команд, сегмент данных и сегмент ввода-вывода. Сегмент команд служит для хранения программы, также в нем могут содержаться некоторые данные, например, таблицы коэффициентов. Сегмент данных содержит данные, используемые при выполнении программы. Сегмент ввода-вывода используется для доступа к внешним периферийным устройствам и может также использоваться как расширение сегмента данных.

Параллельная архитектура ядра процессора позволяет выполнять 4 конкурирующих операции с памятью в одном такте: выборка команды, чтение двух операндов и запись результата. Для этого используются четыре параллельных системы шин: шина чтения команд (РВ). шина записи данных (ЕВ) и две шины чтения данных (СВ и DB). Каждая шина имеет доступ к разным областям памяти для разных видов операций. Такая архитектура позволяет выполнять параллельное чтение двух операндов, 32-разрядный доступ и одновременное чтение и запись операндов.

На кристалле С5000 располагаются два вида внутреннего ОЗУ - с двойным доступом и с одинарным доступом. ОЗУ с двойным доступом делится на блоки по 2Кслов. Данные в каждом из этих блоков могут быть считаны или записаны дважды за один машинный такт. Основное назначение данной памяти - хранение данных. однако она может быть сконфигурирована и как память команд.

Старшие модели семейства могут поддерживать до 8М 16 -разрядных слов (см. таблицу характеристик) и имеют эффективные механизмы работы со страничной адресацией, позволяющие производить автоматическое переключение старших разрядов адреса. Эта память организована как 128 страниц длинной по 64Кслов. При этом в процессоре добавляются дополнительные 7 линий адреса и расширенный регистр счетчика команд, а также ряд дополнительных команд.

Начальный загрузчик. Начальный загрузчик - это программа, размещенная во внутреннем ПЗУ процессора. Он используется для переписывания программы из внешнего источника в ОЗУ процессора или внешнее ОЗУ, где она будет исполняться. Начальный загрузчик вызывается автоматически при включении питания или при

сбросе процесс ора, если установлен соответствующий режим. Режим устанавливается переводом вывода МР/МС в нулевое состояние. Если при сбросе процессора этот вывод находится в состоянии 0. то процессор начинает выполнять команды из внутреннего ПЗУ процессора. Начальный загрузчик может выполнять загрузку программы из большого набора источников:

• Параллельное 8- или 16-разрядное ПЗУ

• Параллельная загрузка из регистра ввода-вывода

• Загрузка из последовательного порта с 8- или 16-разрядными данными

• Загрузка через Хост-порт интерфейс

• Мягкий старт

Режимы загрузки программы из последовательного или из хост-порта дают возможность отказаться от отдельного ПЗУ для ЦСП и загружать программу их хост процессора без каких либо дополнительных затрат. При этом не требуется подведения громоздкой параллельной шины и для загрузки программы используется тот же интерфейс, что и для связи между ЦСП и хост-процессором.

Внутренняя периферия.

Все процессоры семейства С54ХХ имеют множество размещаемых на кристалле периферийных устройств. Конкретный набор зависит от модели процессора. В этот набор входят

• программируемый генератор задержек

• программируемый переключатель банков памяти

• параллельный порт ввода-вывода

• широкий выбор последовательных портов

• таймер

• тактовый генератор АЦП

Программируемый генератор задержек служит для увеличения длительности цикла обмена по шине до 7 машинных тактов при обмене с медленными внешними устройствами или с медленной внешней памятью. Он работает без использования какого-либо внешнего аппаратного обеспечения. Количество тактов задержки задается для набора областей памяти через специальные регистры.

Программируемый переключатель банков памяти служит для автоматической вставки одного дополнительного такта при пересечении границ банка памяти или при переходе от памяти команд к памяти данных. Этот дополнительный цикл позволяет одному устройству памяти освободить шину перед тем, как ее займет другое устройство памяти, что исключает аппаратные конфликты на шине. Размер банка памяти задается специальным регистром.

Параллельные порты ввода-вывода. Каждый процессор семейства С5000 может адресовать 64К портов ввода-вывода. Доступ к портам осуществляется специальными командами ввода-вывода. Через пространство портов ввода-вывода организуется наиболее простой интерфейс к внешним устройствам, требующий минимального количества внешней логики декодирования адреса.

Хост порт интерфейс. ХПИ это параллельный 8-разрядный (или 16-разрядный) интерфейс для связи ЦСП с хост-процессором (управляющим контроллером). Обмен информацией между ЦСП и хост-процессором идет через блок во внутреннем двухпортовом ОЗУ ЦСП размером в 2Кслов, к которому имеют доступ как ЦСП, так и хост-процессор. Возможна организация 16 разрядного доступа через обмен

двойными байтами. ХПИ может работать в двух режимах - в первом из них хост-процессор и ЦСП имеют конкурентный доступ к этому блоку памяти с приоритетом хост-процессора. Во втором режиме хост-процессор имеет доступ к с внутренней памяти ЦС11. когда ЦСП находится в спящем режиме или в состоянии сброса. Обмен с ХПИ возможен и тогда, когда процессор находится в состоянии IDLE2 . то есть остановлены все тактовые сигналы как ядра процессора, так и периферии. При этом не происходит выхода процессора из этого режима и. соответственно, увеличения потребления питания. Скорость обмена через ХПИ в 16-разрядном режиме может достигать 20 МБайт в секунду.

Тактовый генератор. Процессоры семейства С5000 имеют гибкую систему формирования тактовых импульсов с переменными параметрами. Эта система позволяет как делить входную частоту, так и умножать ее, что дает возможность гибкого выбора частоты внешнего генератора и рабочей частоты процессора. Возможность умножения частоты позволяет использовать для генерации быстрого внутреннего тактового сигнала низкую частоту. Это уменьшает количество проблем с наводками внешней тактовой частоты, с разводкой ее по плате, позволяет использовать более медленные генераторы и резонаторы и снизить энергопотребление системы. Кроме того. старшие модели семейства имеют возможность программной подстройки частоты работы процессора. Коэффициент умножения частоты при программной подстройке может меняться от 0,25 до 16. Это позволяет менять тактовую частоту программно, в процессе работы, в зависимости от требуемого режима работы. Вместе с тактовой частотой меняется и ток потребления процессора. Таким образом, можно, меняя ток потребления, добиться компромисса между временем активной работы процессора и потребляемой им в активном режиме мощностью, что особенно важно для мобильных систем с лимитированной емкостью источников питания. При этом для каждого режима работы устройства можно устанавливать оптимальное соотношение между временем выполнения задачи и током потребления процессора.

Контроллер прямого доступа к памяти (ПДП). Позволяет осуществлять передачу данных из одной области памяти в другую без участия ЦПУ. Контроллер ПДП позволяет пересылать данные в и из памяти команд, памяти данных, внутренней периферии, такой как МКБПП, или внешней памяти, параллельно с работой ЦПУ. Всего контроллер ПДП имеет 6 независимых каналов с программируемым приоритетом.

Последовательные порты. Процессоры семейства С5000 имеют несколько видов последовательных портов.

Стандартный последовательный порт - синхронный последовательный порт с независимыми каналами приема и передачи, двойной буферизацией, программируемыми тактовыми частотами и длиной данных.

TDM порт. Позволяет обмениваться данными в режиме временного разделения. Всего через этот порт могут быть соединены до 7 устройств. При этом каждому устройству выделяется свой временной интервал для обмена.

Буферизованный последовательный порт - имеет возможность прямого чтения и записи данных во внутреннюю память процессора. Размеры и положение буфера в памяти программируются пользователем. При работе буферизованного порта прерывание вызывается не на каждый прием или передачу данных, а при заполнении или исчерпании буфера данных. Максимальная скорость обмена по буферизованному последовательному порту может достигать 50 мегабит/сек.