- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

11. Построение центрального процессора на базе микропроцессора Intel 8086.

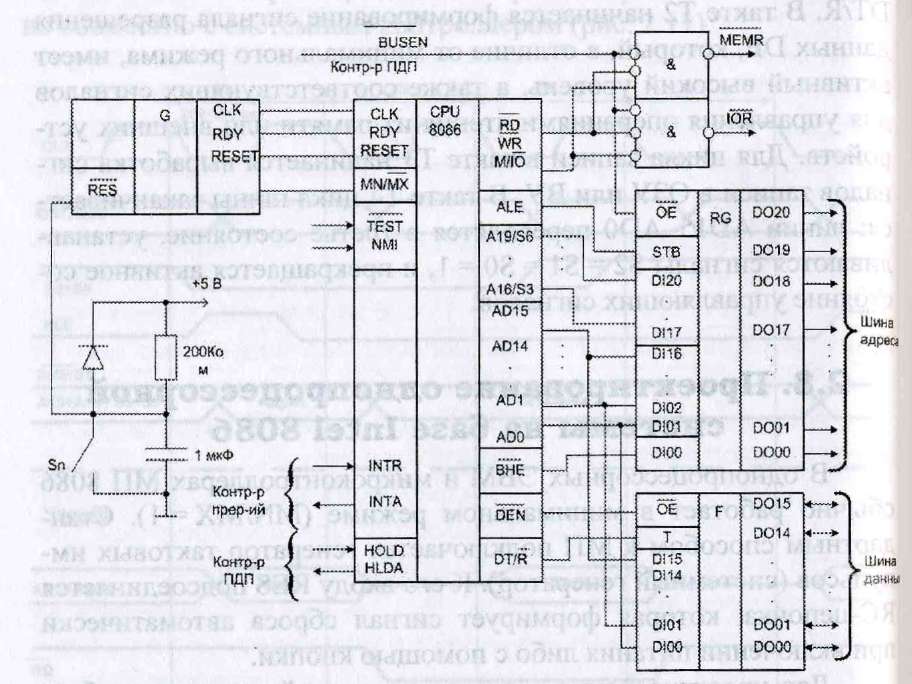

Построение блока центрального процессора. При разработке структуры блока ЦП (рис. 2.12) возникают три задачи:

разделения (демультиплексирования) шины адреса/ Данных (ШАД);

буферирования шины адреса (ША) и шины данных (ШД);

формирования системных управляющих сигналов для блоков памяти и внешних устройств.

Первая задача решается с помощью тристабильных регистровых схем, выполняющих функции адресной защелки. Так как сигнал ВНЕ формируется в том же интервале времени, что и адресные сигналы, то его также необходимо зафиксировать в защелке. Поэтому на рис. 2.12 показана схема 21-разрядного регистра адреса.

Рис. 2.12. Пример построения центрального процессора на базе МП Intel 8086

Вторая задача решается с помощью двунаправленных шинных формирователей с тремя устойчивыми состояниями, которые усиливают сигналы системной шины данных.

Третья задача может быть решена с помощью комбинационных логических схем, которые формируют требуемые управляющие сигналы на основе сигналов RD, WR и М/IO, вырабатываемых МП. Если в системе используется адресное пространство ввода-вывода, изолированное от пространства памяти, то целесообразно сформировать сигналы, аналогичные сигналам на выходах системного контроллера. Если же в микропроцессорной системе ввод-вывод организован с отображением на память, то сигнал М/IO не используется, и на ЗУ и ВУ подаются сигналы RD и WR после усиления.

Используемые усилители и формирователи должны обеспечивать три выходных состояния, чтобы можно было организовать прямой доступ к памяти (ПДП). В этом случае после перевода МП в состояние захвата усилители переходят в третье состояние по сигналу РМ (BUSEN), поступающему от контроллера ПДП. Если захват шин и обмен данными по каналу ПДП не предусмотрен, то необходимость в таком переключении отпадает.

12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

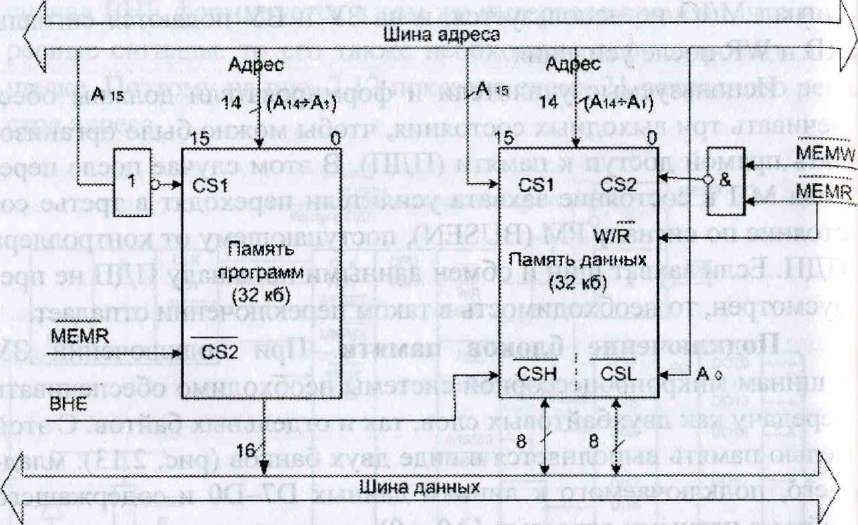

Подключение блоков памяти. При подключении ЗУ к шинам микропроцессорной системы необходимо обеспечивать передачу как двухбайтовых слов, так и отдельных байтов. С этой целью память выполняется в виде двух банков (рис. 2.13): младшего, подключаемого к линиям данных D7-D0 и содержащего байты с четными адресами (АО = 0), и старшего, соединенного с D15-D8 и содержащего байты с нечетными адресами (АО = 1). Чтобы каждое слово передавалось за один цикл шины, слова располагают только с четных адресов.

Напомним, что адресная линия АО совместно с линией разрешения старшего банка ВНЕ обеспечивает следующие варианты пересылок по шине данных:

АО = 0, ВНЕ = 0 - пересылается слово;

АО = 0, ВНЕ = 1 - пересылается только младший байт;

АО = 1, ВНЕ = 0 - пересылается только старший байт;

АО = 1, ВНЕ = 1 - устройство не выбрано.

Выработка сигнала ВНЕ и указанный порядок пересылок реализуются микропроцессором автоматически.

При чтении из ЗУ в любом случае на шину данных будет подаваться слово, из которого МП при необходимости выберет требуемый байт и поместит его в регистр, указанный в выполняемой команде. Поэтому сигналы ВНЕ и АО на постоянное ЗУ (ПЗУ, на рис. 2.13 - память программ) не подаются. При записи в ЗУ (на рис. 2.13 - память данных) необходимо различать старший и младший байты, иначе может происходить разрушение информации, хранящейся в соседнем байте. Для этого сигналы ВНЕ и АО подаются на входы CSH и CSL выбора старшего и младшего банков ОЗУ.

Процесс обращения к ПЗУ стробируется сигналом MEMR, а к ОЗУ - сигналами MEMR и MEMW, объединенными с помощью логического элемента И-НЕ.