- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

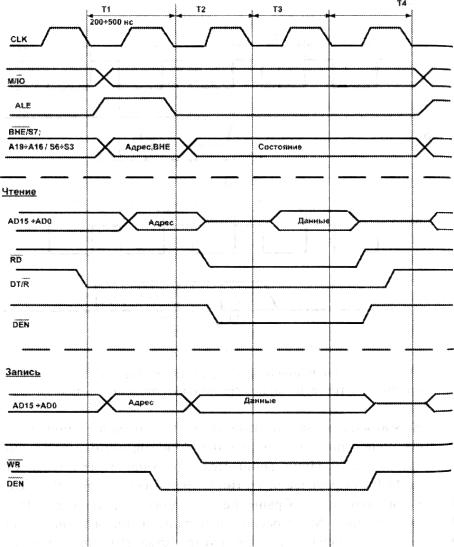

9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

В минимальном режиме функционирование микропроцессора иллюстрируется временными диаграммами, приведенными на рис. 2.10. Цикл начинается с формирования в такте Т1 сигнала M/IO, определяющего тип устройства (ЗУ или ВУ), к которому производится обращение для пересылки данных. Длительность сигнала М/IO равна длительности цикла шины, и он используется для селекции адреса устройства. В такте Т1 и в начале такта Т2 микропроцессор выставляет адрес ЗУ на линии А19-А16 и AD15-AD0 либо адрес ВУ на линии AD15-AD0, а также вырабатывает сигнал ВНЕ, который вместе с АО определяет передачу слова или одного из байтов. Одновременно с этим МП выдает строб адреса ALE, по спаду которого адрес фиксируется во внешних регистрах-защелках. На выходах этих регистров адрес сохраняется в течение всего цикла шины (до записи нового значения).

В такте Т2 происходит переключение шин:

на линии A19/S6-A16/S3

поступают сигналы состояния S6-S3,

которые сохраняются

до

конца такта Т4. В дальнейшем значения

этих сигналов

зависят от вида выполняемого действия

(чтение или запись).

такте Т2 происходит переключение шин:

на линии A19/S6-A16/S3

поступают сигналы состояния S6-S3,

которые сохраняются

до

конца такта Т4. В дальнейшем значения

этих сигналов

зависят от вида выполняемого действия

(чтение или запись).

В цикле чтения в такте Т2 линии AD15-AD0 переводятся в третье состояние до появления данных от адресованного устройства. В тактах Т2-Т4 вырабатывается сигнал чтения RD = О, который указывает этому устройству на необходимость выдачи данных. Для управления буферами данных, которые обычно подключаются к линиям AD 15-AD0, в тактах Т2-Т4 формируется сигнал DE, разрешающий передачу данных. Направление передачи данных при чтении определяет сигнал DT/R = 0, действующий в течение всего цикла. После выполнения чтения и установления сигнала RD = 1 микропроцессор заканчивает такт Т4 следующим образом: линии AD15-AD0 находятся в высокоом- ном состоянии, сигналы М/Ю, DE, DT/R, S7-S3 неактивны, буферы данных отключены от канала.

В цикле записи в такте Т2 адрес на линиях AD15-AD0 заменяется данными, предназначенными для записи в адресуемое устройство. Данные остаются действительными до середины такта Т4 и сопровождаются сигналом WR = 0, который используется в качестве строба для записи данных в устройство. Сигнал DE = О появляется уже в такте Т1 и используется для подготовки буферов к передаче данных. Сигнал DT/R= 1, переключающий буферы на передачу данных в направлении к МП, удерживается на протяжении всего цикла записи. После установления WR = 1 такт Т4 заканчивается так же, как и при выполнении цикла чтения.

Таким образом, циклы чтения и записи различаются не только активными значениями сигналов RD или WR и состоянием сигнала DT/R, но и тем, что в цикле записи сигналы DE и WR становятся активными раньше и имеют большую длительность, чем в цикле чтения. Соответственно данные при записи присутствуют на шине в течение большего промежутка времени, чем при чтении.

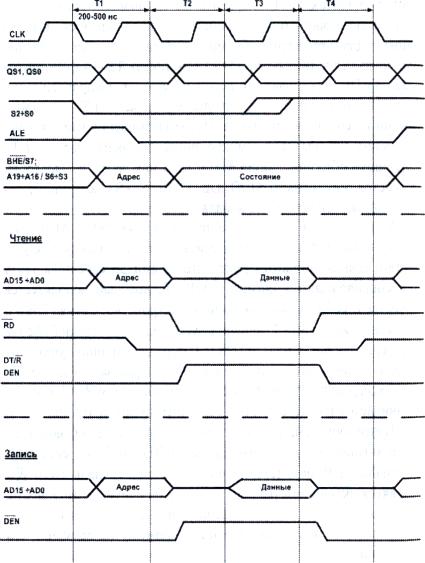

10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

В максимальном режиме работа шины адреса/данных микропроцессора эквивалентна работе в минимальном режиме.

Как уже отмечалось, в максимальном режиме изменяется значение восьми управляющих сигналов, в частности МП вырабатывает сигналы состояния S2-S0, на основе которых системный контроллер формирует необходимые системные управляющие сигналы. Таким образом, МП в этом режиме работает обязательно совместно с системным контроллером (рис. 2.11).

К од

состояния S2-S0

выдается по срезу синхроимпульса в

последнем

такте предшествующего цикла, которым

может быть такт Т4 или Т1. В такте Т1

контроллер формирует строб ALE

и

устанавливает необходимый уровень

сигнала на выходе DT/R.

В такте Т2 начинается формирование

сигнала разрешения данных

DE,

который, в отличие от минимального

режима, имеет активный

высокий уровень, а также соответствующих

сигналов для управления операциями

чтения из памяти или внешних устройств.

Для цикла записи в такте ТЗ начинается

выработка сигналов записи

в

ОЗУ или ВУ. В такте Т4 цикл шины

заканчивается: линии AD15-AD0

переводятся в третье состояние,

устанавливаются сигналы S2

= SI

= SO

= 1, и прекращается активное состояние

управляющих сигналов.

од

состояния S2-S0

выдается по срезу синхроимпульса в

последнем

такте предшествующего цикла, которым

может быть такт Т4 или Т1. В такте Т1

контроллер формирует строб ALE

и

устанавливает необходимый уровень

сигнала на выходе DT/R.

В такте Т2 начинается формирование

сигнала разрешения данных

DE,

который, в отличие от минимального

режима, имеет активный

высокий уровень, а также соответствующих

сигналов для управления операциями

чтения из памяти или внешних устройств.

Для цикла записи в такте ТЗ начинается

выработка сигналов записи

в

ОЗУ или ВУ. В такте Т4 цикл шины

заканчивается: линии AD15-AD0

переводятся в третье состояние,

устанавливаются сигналы S2

= SI

= SO

= 1, и прекращается активное состояние

управляющих сигналов.