- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

В максимальном режиме действуют следующие управляющие сигналы (помимо общих сигналов с минимальным режимом, см. воп. 4).

S2-S0 (State) - сигналы состояния, содержащие информацию о типе выполняемого цикла шины. Сигналы состояния подаются в контроллер шины, который дешифрует их и формирует расширенный набор управляющих сигналов. Если МП не инициирует цикл шины, то сигналы S2-S0 устанавливаются в пассивное состояние 111.

QS1-QS0 (Queue State) - состояние очереди. Идентифицирует состояние внутренней 6-байтовой очереди команд МП и действует в течение такта синхронизации после выполнения операции над очередью. Сигналы QS1-QS0 предназначены для сопроцессора, который воспринимает команды и операнды с помощью команды ESC. Сопроцессор контролирует шину AD и фиксирует момент, когда из программной памяти выбирается предназначенная для него команда ESC, а затем следит за очередью команд и определяет момент, когда эта команда должна выполняться.

RQ/GT1-RQ/GT0 (Request/Get) - запрос/представление (подтверждение, разрешение). Две одинаковые двунаправленные линии, каждая из которых может использоваться для передачи импульсных сигналов запроса/разрешения доступа к локальной шине (каналу). Процесс доступа к шине осуществляется в следующем порядке:

1. устройство, подключенное к локальной шине и требующее доступа к общим ресурсам, формирует запросный (первый) импульс длительностью один такт;

2. в конце текущего цикла МП выдает ответный (второй) импульс, подтверждающий возможность доступа к локальной шине. В следующем такте МП переводит шины адреса/данных и управления в высокоомное состояние и отключается от канала;

3. по окончании работы с каналом устройство выдает на ту же линию импульс (третий), указывающий на окончание захвата канала. В следующем такте МП возобновляет управление шиной и продолжает вычисления.

Все три импульса имеют одинаковую длительность и низкий активный уровень. Сигналы на линиях независимы, однако линия RQ/GT0 имеет более высокий приоритет, чем линия RQ/GT1, когда запросы поступают одновременно. Но если на линии RQ/GT0 появляется запрос в то время, когда МП находится в состоянии захвата по сигналу RQ/GT1, то этот запрос захвата не получает подтверждения до освобождения шины по линии RQ/GT1. Таким образом, каждая из двух рассмотренных линий служит для установления режима захвата шин .

LOCK - блокировка шины, информирует устройства системы, что они не должны пытаться запрашивать шину. Формируется однобайтовым префиксом LOCK, располагаемым перед командой, и действует до конца выполнения этой команды, запрещая доступ к системной магистрали другим устройствам, в частности другим процессорам. При подтверждении запроса шины выходной буфер сигнала LOCK переводится в третье состояние. Префикс LOCK не влияет на прерывания.

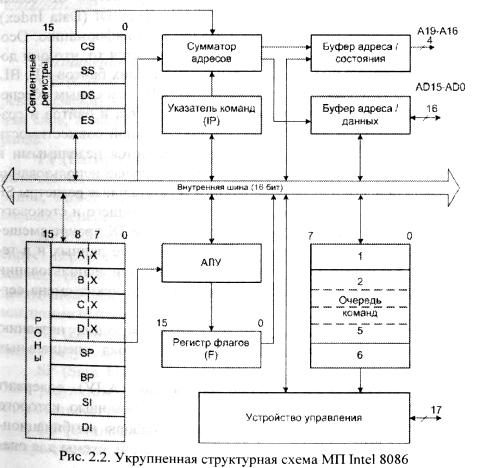

6. Структура микропроцессора Intel 8086.

Структура МП содержит три относительно независимые части:

операционное устройство, реализующее заданные командой операции;

устройство шинного интерфейса, осуществляющее выборку команд из памяти, а также обращение к памяти и внешним устройствам для считывания операндов и записи результатов;

устройство управления.

Устройства могут работать параллельно, что обеспечивает совмещение во времени процессов выборки и исполнения команд. Это повышает быстродействие МП, так как операционное устройство, как правило, выполняет команды, коды которых уже находятся в МП, и поэтому такты выборки команды не включаются в ее цикл.

Операционное устройство МП содержит группу общих регистров, арифметико-логическое устройство (АЛУ) и регистр флагов F.

Восемь 16-битовых регистров общего назначения участвуют во многих командах.

В соответствии с основным назначением рассматриваемых регистров выделяют регистры АХ, ВХ, СХ, DX, используемые прежде всего для хранения данных, и регистры SP (Stack Pointer), BP (Branch Pointer), SI (Stack Index), DI (Data Index), которые хранят главным образом адресную информацию. Особенностью регистров АХ, ВХ, СХ, DX является то, что они допускают раздельное использование их младших байтов AL, BL, CL, DL и старших байтов АН, ВН, СН, DH. Тем самым обеспечивается возможность обработки как слов, так и байтов и создаются необходимые условия для программной совместимости с МП 8080. Все остальные регистры являются неделимыми и оперируют 16-битовыми словами, даже в случае использования только старшего или младшего байта. Указательные регистры SP и BP хранят смещение адреса в пределах текущего и стекового сегмента памяти, а индексные регистры SI и DI хранят смещение адреса соответственно в текущем сегменте данных и в текущем дополнительном сегменте. Однако при использовании этих регистров для адресации операндов возможна смена сегментов памяти.

Кроме основных функций, соответствующих названию регистров, общие регистры выполняют и ряд специальных функций.

АЛУ содержит 16-битовый комбинационный сумматор, с помощью которого выполняются арифметические операции, наборы комбинационных схем для выполнения логических операций, схемы для операций сдвигов и десятичной коррекции, а также регистры для временного хранения операндов и результатов.

К АЛУ примыкает регистр флагов F (рис. 2.3). Его младший байт FL полностью соответствует регистру флагов МП Intel 8080, а старший байт FH содержит четыре дополнительных флага. Шесть арифметических флагов фиксируют определенные признаки результата выполнения операции (арифметической, логической, сдвига или загрузки регистра флагов). Значения этих флагов (кроме флага AF) используются для реализации условных переходов, изменяющих ход выполнения программы. Различные команды влияют на флаги по-разному.

![]()

Рис. 2.3. Формат регистра флагов F

Назначение арифметических флагов:

CF (Carry Flag) - флаг переноса.

PF (Parity Flag) - флаг четности (или паритета).

AF (Additive Flag) - флаг вспомогательного переноса, фиксирует перенос (заем) из младшей тетрады в старшую при сложении (вычитании.

ZF (Zero Flag) - флаг нуля.

SF (Sign Flag) - флаг знака.

OF (Overflow Flag) - флаг переполнения.

Для управления некоторыми действиями МП предназначены три дополнительных флага.

DF (Direct Flag) - флаг направления, управляемый командами CLD и STD; определяет порядок обработки цепочек в соответствующих командах: от меньших адресов (DF = 0) или от больших (DF = 1).

IF (Interrupt Flag) - флаг разрешения прерываний, управляемый с помощью команд CLI и STI; при IF = 1 микропроцессор воспринимает и соответственно реагирует на запрос прерывания по входу INTR; при IF = 0 прерывания по этому входу запрещаются (маскируются) и МП игнорирует поступающие запросы прерываний.

TF (Trace Flag) - флаг трассировки (прослеживания). При TF = 1 МП переходит в покомандный (пошаговый) режим работы, применяемый при отладке программ, когда автоматически генерируется сигнал внутреннего прерывания типа 1 после выполнения каждой команды с целью перехода к соответствующей подпрограмме, которая обычно обеспечивает индикацию содержимого внутренних регистров МП.

Управляющее устройство (УУ) дешифрует команды, а также воспринимает и вырабатывает необходимые управляющие сигналы. В его состав входит блок микропрограммного управления, в котором реализовано программирование МП на микрокомандном уровне.

Устройство шинного интерфейса содержит блок сегментных регистров, указатель команд, сумматор адресов, очередь команд и буферы, обеспечивающие связь с шиной. Шинный интерфейс выполняет операции обмена между МП и памятью или портами ввода-вывода по запросам операционного устройства. Когда операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует опережающую выборку кодов очередных команд из памяти.

Очередь команд представляет собой набор байтовых регистров и выполняет роль регистра команд, в котором хранятся коды, выбранные из программной памяти. Длина очереди составляет 6 байт, что соответствует максимально длинному формату команд. Наличие очереди команд, а также способность операционного устройства и шинного интерфейса работать параллельно позволяют совместить во времени фазы выборки команды и выполнения заданной операции: пока одна команда исполняется в операционном устройстве, шинный интерфейс осуществляет выборку следующей команды. Таким образом, достигаются высокая плотность загрузки шины и повышение скорости выполнения программы.

Буфер шины адреса/данных (БАД) содержит 16 двунаправленных управляемых усилителей с тремя выходными состояниями и обеспечивает номинальную нагрузочную способность линий AD15-AD0.

Буфер шины адреса/состояния (БАС) содержит четыре однонаправленных усилителя с тремя выходными состояниями и обеспечивает номинальную нагрузочную способность линий A19/S6-A16/S3.

Сегментные регистры хранят базовые (начальные) адреса сегментов памяти: кодового сегмента CS (Code Segment), в котором содержится программа; стекового сегмента SS (Stack Segment); сегмента данных DS (Data Segment); дополнительного сегмента ES (Extended Segment), в котором обычно содержатся данные. Наличие сегментных регистров обусловлено разделением памяти на сегменты и используемым способом формирования адресов памяти.

Сумматор адресов осуществляет вычисление 20-битовых физических адресов путем суммирования смещения и содержимого соответствующего сегментного регистра, которое дополняется четырьмя нулевыми младшими разрядами.

Указатель команд IP (Instruction Pointer) хранит смещение следующей команды в текущем кодовом сегменте, т.е. указывает на следующую по порядку команду.