- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

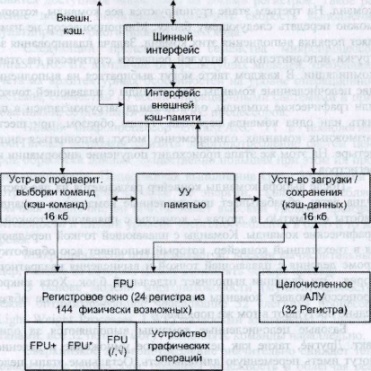

Семейство процессоров с архитектурой SPARC включает 32-разрядные микропроцессоры MicroSPARC, Super SPARC, HiperSPARC и целый подкласс 64-разрядных микропроцессоров UltraSPARCxx. Традиционно системы на основе SPARC микропроцессоров - это высокопроизводительные рабочие станции для научных расчетов и Unix-серверы. Архитектура SPARC была создана компанией Sun Microsystems в 1985 г. В ее основу положены результаты работ RISC I и RISC II, проводившиеся в Калифорнийском университете в Беркли с 1980 по 1982 г. В частности, в архитектуру SPARC вошла предложенная в Беркли концепция «регистровых окон», упрощающая создание однопроходных компиляторов и существенно снижающая количество команд обращения к памяти по сравнению с другими реализациями RISC-архитектуры. Основными чертами архитектуры SPARC являются:

- поддержка линейного 32-разрядного адресного пространства;

- использование 32-разрядных команд фиксированной структуры с тремя базовыми форматами;

- реализация доступа к памяти и пространству ввода/вывода посредством команд загрузки/сохранения;

- небольшое количество способов адресации (либо «регистр - регистр», либо «регистр - непосредственный операнд»);

- использование трехадресных регистровых команд, когда команда выполняется над двумя операндами, а результат помещается в регистр-приемник;

- большой регистровый файл с регистровыми окнами, что позволяет значительно сократить накладные расходы, связанные с переключением контекста при выполнении параллельных процессов; в каждый момент времени программе доступно восемь глобальных целочисленных регистров и регистровое окно (24 регистра), отображаемое на регистровый файл;

- отдельный регистровый файл вещественных регистров, который может интерпретироваться в программах как набор из 32 регистров обычной точности (32 бита) или 16 регистров двойной точности (64 бита), или восьми регистров учетверенной точности (128 бит), или как смесь регистров различной разрядности;

-отложенная передача управления, когда процессор всегда выбирает команду, следующую за командой передачи управления; она может быть выполнена или не выполнена в зависимости от состояния «аннулирующего» разряда в команде передачи управления;

- быстрые обработчики прерываний;

- команды межпроцессорной синхронизации - одна команда выполняет непрерываемую операцию «чтения с последующей записью», другая команда - «непрерываемый обмен содержимого регистра и памяти»;

- поддержка сопроцессора, который может использоваться наряду с АЛУ;

- двоичная совместимость программ пользователей на всех реализациях SPARC, т.е. готовые программы должны вести себя совершенно одинаково на всех SPARC-системах.

Любой процессор с архитектурой SPARC может работать попеременно в одном из двух режимов: пользовательском и привилегированном. В привилегированном режиме процессор выполняет все команды, включая привилегированные. В пользовательском режиме попытка выполнения привилегированных команд вызывает прерывание с передачей управления специальной системной программе.

Конкретная аппаратная реализация целочисленного устройства может содержать от 40 до 520 32-разрядных регистров общего назначения. Регистровый файл целочисленного устройства разбит на группы из восьми глобальных регистров и циклического стека, содержащего от двух до 32 наборов (регистровых окон) по 16 регистров в каждом. В каждый момент времени исполняемой программе доступны восемь глобальных регистров и регистровое окно размером в 24 регистра.

Регистры окна разбиты на три группы: восемь входных регистров, восемь локальных и восемь выходных регистров, которые в то же время являются входными регистрами смежного окна, т.е. соседние окна перекрываются на восемь регистров. Текущее окно задается полем указателя текущего окна в слове состояния процессора.

Архитектура SPARC поддерживает три основных типа данных:

-знаковое целое - 8, 16, 32 и 64 разряда;

-беззнаковое целое - 8, 16, 32 и 64 разряда;

-вещественное - 32, 64 и 128 разрядов.

Микропроцессоры UltraSPARCxx являются «старшими» представителями семейства, которые позволили существенно увеличить возможности SPARC-систем по обработке графики и видеоизображений. UltraSPARC стал одним из первых универсальных процессоров, в котором эти функции реализованы аппаратно. Он имеет специальный модуль для обработки видеоданных и графики. Функции обработки видеоизображений могут работать сразу с восемью элементами изображения. Обработка изображений выполняется в блоке FPU, который обычно выполняет операции над 64-битовыми данными с плавающей точкой. В этом блоке выполняются логическое сложение и умножение элементов изображения. В систему команд микропроцессора включен набор команд (VIS - Visual Instruction Set), позволяющий загружать и обрабатывать данные в виде 64-битовых блоков. VIS насчитывает 30 команд для эффективной обработки мультимедиа, графики, изображений и других алгоритмов, ориентированных на целочисленную обработку. Команды VIS включают в себя сложение, умножение и вычитание, что позволяет параллельно выполнять за один такт до восьми целочисленных операций над байтами или полусловами.

U ltraSPARC

имеет также несколько специальных

средств, улучшающих его работу с памятью.

Это повышает производительность

программ мультимедиа и других системных

задач. Самым крупным изменением является

новая команда перемещения блока

данных по шине «процессор - память» со

скоростью 600 Мб/с. Это позволяет основному

процессору работать как видеопроцессор,

передавая данные с экрана на экран.

Перемещение блока можно с выгодой

использовать и в других приложениях,

например в сетевом программном обеспечении

для перемещения пакетов данных.

ltraSPARC

имеет также несколько специальных

средств, улучшающих его работу с памятью.

Это повышает производительность

программ мультимедиа и других системных

задач. Самым крупным изменением является

новая команда перемещения блока

данных по шине «процессор - память» со

скоростью 600 Мб/с. Это позволяет основному

процессору работать как видеопроцессор,

передавая данные с экрана на экран.

Перемещение блока можно с выгодой

использовать и в других приложениях,

например в сетевом программном обеспечении

для перемещения пакетов данных.

Команды сохраняются в кэше и для ускорения обработки предварительно декодируются. Каждые две инструкции в кэше ассоциируются с двумя битами, которые используются для предсказания переходов. Два бита позволяют отслеживать четыре различных состояния, кодирующих последние два перехода, выполняемых по этим командам. Механизм предвыборки использует эти биты для динамического упреждения переходов. UltraSPARC способен предсказывать переход с вероятностью около 0,9.

Обрабатывающий конвейер UltraSPARC имеет девять этапов и позволяет выполнять до четырех команд за один такт. Первые два этапа стандартные - это выборка и декодирование команд. На третьем этапе группируются все команды, которые можно передать следующему блоку. Микропроцессор не изменяет порядка выполнения этих команд. Задача планирования загрузки исполнительных модулей решается статически на этапе компиляции. В каждом такте могут выбираться на выполнение две целочисленные команды, две команды с плавающей точкой или графические команды, одна команда загрузки/записи в память или одна команда перехода. Таким образом, при шести возможных командах одновременно могут выполняться лишь четыре. На этом же этапе происходит получение информации из регистров.

После выбора команды конвейер разделяется на две части. Одна ветвь обрабатывает целочисленные команды и команды работы с памятью, а другая - команды с плавающей точкой и графические команды. Команды с плавающей точкой передаются в трехэтапный конвейер, который выполняет всю обработку, кроме деления с плавающей точкой и вычисления квадратного корня. Эти функции выполняет отдельный блок. Хотя микропроцессор подает команды поочередно, результаты не обязательно поступают в том же порядке.

Базовые целочисленные команды выполняются за один такт. Другие, такие как целочисленное умножение и деление, могут иметь переменную длительность. Остальные этапы целочисленного конвейера выполняют загрузку/запись в память.

Для получения высокой пропускной способности UltraSPARC использует иерархию шин. 128-разрядная шина памяти работает с тактовой частотой самого процессора. Для выполнения ввода-вывода на периферийные устройства используется шина SBus. Sun Microsystems реализует интерфейс с этой шиной на аппаратном уровне с помощью микросхемы коммутации магистрали, входящей в набор микросхем процессора. Она позволяет изолировать шину памяти от шины ввода-вывода и выполнять операции чтения из памяти одновременно с вводом- выводом на периферийные устройства. В результате достигается высокий коэффициент использования шины и пропускная способность 1,3 Гбит/с.

Следующий представитель семейства микропроцессор UltraSPARC III, в отличие от предыдущих моделей, требующих учета их архитектурных особенностей на уровне операционной системы, совместим со всеми операционными системами и приложениями, созданными для SPARC процессоров.

Новый микропроцессор UltraSPARC Т1 с технологией CoolThreads позволяет снизить энергопотребление систем центров обработки данных, существенно повышая при этом их производительность. Поддерживая выполнение сразу 32 потоков и потребляя примерно столько же энергии, сколько потребляет обычная лампочка, он обеспечивает высокий уровень производительности и низкий уровень энергопотребления в одно и то же время.

Микропроцессор поддерживает до восьми вычислительных ядер, каждое из которых может выполнять четыре потока.

Сверхнизкое энергопотребление значительно снижает тепловыделение процессора, повышая надежность и облегчая реализацию охлаждения систем центров обработки данных.

Микропроцессор UltraSPARC Т1 имеет следующие параметры:

- множественно ассоциативный кэш команд первого уровня по 16 Кб на каждое ядро;

- множественно ассоциативный кэш данных с четырьмя каналами по 8 Кб на одно ядро;

- интегрированная множественно ассоциативная кэш-память второго уровня с четырьмя каналами емкостью до 3 Мб;

- поддержка шифрования с открытым ключом (RSA);

- 48-разрядное виртуальное и 40-разрядное физическое адресное пространство;

- поддержка четырех размеров страниц: 8 Кб, 64 Кб, 4 Мб и 256 Мб;

- поддержка версий с 4, 6 и 8 ядрами;

- четыре 144-разрядных интерфейса памяти;

- исправление 4-битных ошибок, обнаружение 8-битных ошибок;

- 128-разрядная шина адреса/данных;

- технология 90-нанометровая.

Дальнейшее развитие данной линии в виде микропроцессора UltraSPARC Т2 представляет собой фактически уже целую вычислительную систему, выполненную на одном кристалле и реализующую серверные функции вычислений, сетевого администрирования, обеспечения безопасности и ввода/вывода.

Микропроцессоры с архитектурой MAJC, разработанной компанией Sun, предназначены для использования в системах обработки мультимедийных данных и выполнения Internet- приложений.

Первый микропроцессор с данной архитектурой MAJC 5200 был выпущен в середине 2000 г. Он представляет собой два 128-разрядных VLIM (Very Long Instruction Word) микропроцессорных ядра, интегрированных на одном кристалле.

В микропроцессоре реализовано четыре уровня параллелизма:

- мультипроцессорная структура кристалла;

- мультитредовое выполнение программы;

- VLIM-параллелизм на уровне команд;

- SIMD-обработка данных.

Система команд RISC-процессоров ориентирована на поточную обработку мультимедийной информации и аппаратную поддержку высокоуровневых конструкций языка Java. Аббревиатура MAJC образована от «Microprocessor Architecture for Java Computing» (микропроцессорная архитектура для вычислений на языке Java).Архитектура MAJC является масштабируемой. На одном кристалле MAJC может располагаться несколько идентичных процессоров (в зависимости от конкретной реализации), каждый из которых содержит от одного до четырех функциональных блоков - RISC-процессоров и кэш-команд. Каждый из расположенных на кристалле процессоров может выполнять до четырех команд за один такт.

Командное слово MAJC объединяет от одной до четырех 32-разрядных команд, каждая из которых предназначена для одного из четырех RISC-процессоров. В том случае, когда не представляется возможным одновременно задействовать все четыре RISC-процессора, отдельные команды могут отсутствовать, поэтому командное слово MAJC может иметь переменную длину. Для указания количества команд в слове используются его первые два разряда: 00 - одна команда; 01 - две команды; 10 - три команды; 11 - четыре команды. Назначения команд осуществляются в порядке номеров функциональных блоков.