- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

Микропроцессор К5. С 1990 г. AMD и Intel ведут судебную тяжбу по поводу собственности на микрокод процессоров архитектуры х86. В течение ряда лет AMD, отставая от Intel по крайней мере на одно поколение микропроцессоров, полагалась в основном на лицензированную технологию и вносила незначительные изменения в выпускаемые микропроцессоры. Появление Pentium создало для AMD прямую угрозу вытеснения с рынка, что стимулировало компанию к интенсификации работ над созданием нового семейства микропроцессоров, совместимых с семейством х86. Была поставлена цель - создать такое семейство микропроцессоров, которое опередило бы Pentium. Работы над К5 были начаты, когда еще не были известны подробности о микропроцессоре Pentium. К5 - это первый микропроцессор AMD, при создании которого не использовалась никакая интеллектуальная собственность Intel. В то же время он обладает лучшей по сравнению с процессорами Intel производительностью. По данным AMD, реальные приложения (Microsoft Excel, Word, CorelDraw) работают на процессорах серии К5 на 30 % быстрее, чем на Pentium с той же тактовой частотой. Такая производительность достигается в основном за счет увеличенного объема кэш-памяти и более прогрессивной суперскалярной архитектуры. Вместо парных конвейеров целочисленных вычислений Pentium в К5 используется суперскалярная архитектура со счетверенной подачей команд пяти обрабатывающим блокам и RISC-ядром с уникальным декодером инструкций х86.

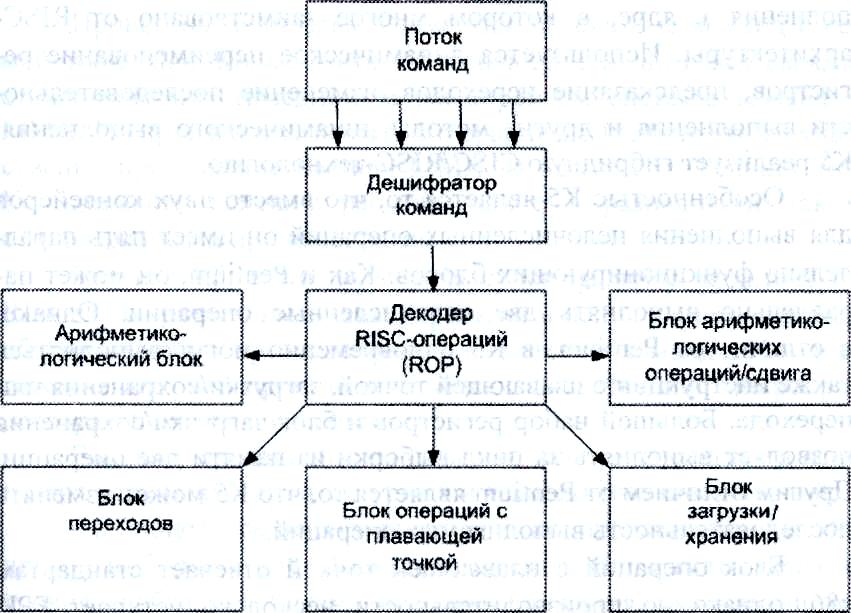

Используемая в микропроцессорах AMD архитектура RISC 86 (впервые предложенная фирмой NexGen) показана на рис. 6.1.

Рис. 6.1. Архитектура RISC 86 компании AMD

Как известно, команды х86 отличает сложность и переменная длина, затрудняющие их динамическое выполнение. Декодер, представляющий собой наиболее сложную часть микропроцессора, разбивает длинные CISC-инструкции на небольшие RISC-подобные компоненты - так называемые ROP (RISC- операции). R-операции напоминают команды микрокода микропроцессоров х86. Первые микропроцессоры с архитектурой х86 выполняли свой сложный набор микрокоманд, выбирая из внутренней постоянной памяти микрокод. В последних микропроцессорах х86 использование микрокода сведено к минимуму за счет применения простых команд. В К5 применяется другой подход: здесь большинство R-операций генерируется динамически не микрокодом, а декодером. Однако микрокод все еще используется для обработки сложных и редко применяемых команд, таких как строковые операции и операции над комплексными числами. Тем не менее даже в этих случаях в результате генерируется поток R-операций. К5 может конвертировать команду х86 в 1-4 R-операции. Эти операции планируются для выполнения в ядре, в котором многое заимствовано от RISC- архитектуры. Используется динамическое переименование регистров, предсказание переходов, изменение последовательности выполнения и другие методы динамического выполнения. К5 реализует гибридную CISC/RISC-технологию.

Особенностью К5 является то, что вместо двух конвейеров для выполнения целочисленных операций он имеет пять параллельно функционирующих блоков. Как и Pentium, он может параллельно выполнять две целочисленные операции. Однако, в отличие от Pentium, в К5 одновременно могут выполняться также инструкции с плавающей точкой, загрузки/сохранения или перехода. Большой набор регистров и блок загрузки/сохранения позволяет выполнять за цикл выборки из памяти две операции. Другим отличием от Pentium является то, что К5 может изменять последовательность выполняемых операций.

Блок операций с плавающей точкой отвечает стандартам х86, однако по производительности несколько уступает FPU микропроцессора Pentium.

Основные характеристики К5:

- совместим с семейством микропроцессоров х86; суперскалярная архитектура с четырехвходовой подачей команд; конвейер с пятью стадиями обработки; пять параллельно функционирующих исполнительных блоков; кэш-команд 16 Кб, кэш данных 8 Кб с двумя портами, линейная адресация; изменение порядка выполнения команд, предсказание переходов, эффективное выполнение, отличный от Intel микрокод; совместим по выводам с Pentium.

Микропроцессор К6. Данный микропроцессор компании AMD явился продуктом совместных усилий AMD и специалистов из бывшей NexGen. По сути дела, Кб представляет собой воплощение проекта Nx686, ранее начатого компанией NexGen, но не завершенного по финансовым причинам. Процессор полностью совместим по системе команд с семейством х86. Кроме того, Кб оснащен ставшим отраслевым стандартом мультимедийным расширением системы команд - ММХ. По производительности Кб сравним с Pentium Pro и существенно превосходит Pentium ММХ. В отличие от Pentium Pro, Кб одинаково успешно работает как с 32-разрядными, так и с 16-разрядными приложениями.Как и в К5, в Кб применена суперскалярная архитектура RISC86 с раздельным декодированием/исполнением команд, обеспечивающая преемственность с системой команд х86 и достижение высокой производительности, свойственной микропроцессорам шестого поколения.

Высокая производительность процессора достигается благодаря ряду новых архитектурных и технологических решений:

- в процессоре реализуется преддекодирование команд х86 при их выборке в кэш. Каждая команда в кэш-памяти первого уровня снабжается битами преддекодирования, указывающими смещение начала следующей команды в кэше (от 1 до 15 байт); Кб содержит внутрикристальный кэш первого уровня по 32 Кб для данных и команд; в процессоре реализован высокопроизводительный блок вычислений с плавающей точкой; имеется высокопроизводительный блок мультимедийных операций стандарта ММХ; используется множественное декодирование х86 инструкций в однотактные RISC-операции;

- процессор поддерживает логику предсказания ветвлений, используя таблицу истории ветвлений из 8192 элементов, кэш адресов перехода и стек возврата, которые обеспечивают вероятность правильного предсказания перехода выше 0,95. В процессоре используется двухуровневая схема предсказания ветвлений. Таблица истории ветвлений не хранит при предсказании целевых адресов, специальные адресные АЛУ вычисляют целевые адреса во время декодирования инструкции. Кэш адресов ветвлений обеспечивает уточнение предсказанного ветвления, уменьшая потери при обращении к памяти. Кэш адресов поставляет на дешифраторы первые 16 байт инструкций, выбранных согласно прогнозу ветвления;

- процессор содержит параллельные дешифраторы, централизованный планировщик операций и семь исполнительных блоков, которые обеспечивают суперскалярное выполнение х86 инструкций в шестиступенчатом конвейере;

- в процессоре используется спекулятивное исполнение с изменением последовательности команд, предварительная посылка данных, переименование регистров.

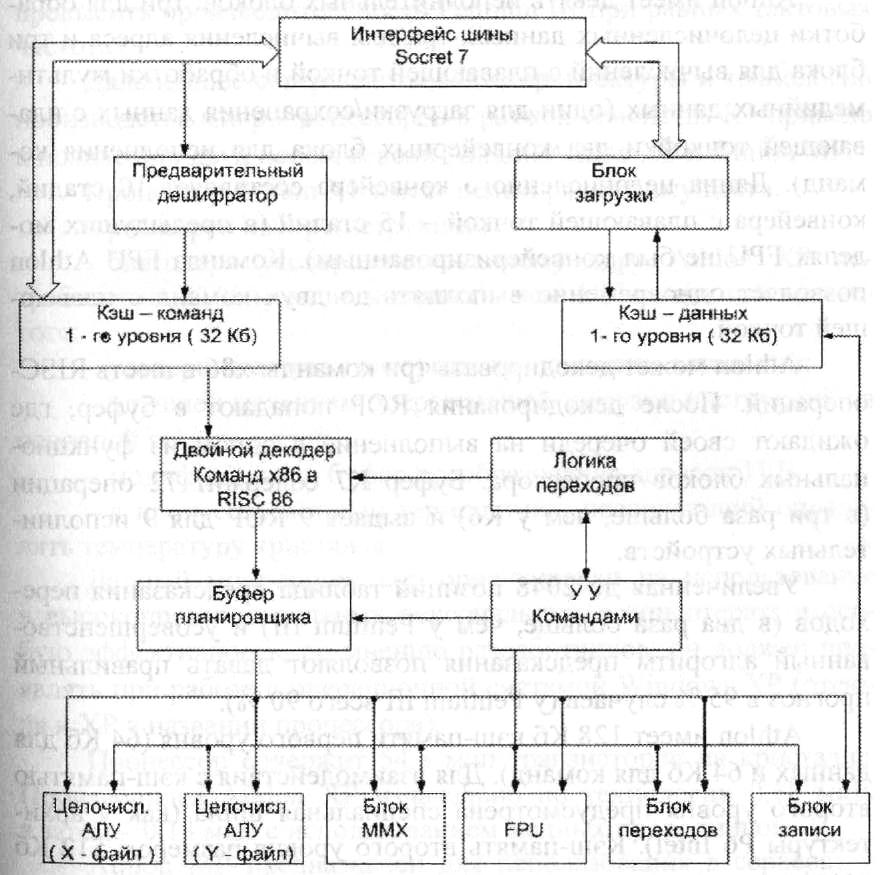

Структура микропроцессора К6 приведена на рис. 6.2.

Рис. 6.2. Структура микропроцессора Кб

RISC-ядро микропроцессора может выполнять за один такт до шести команд RISC86. В процессе исполнения ROP ядро использует 48 физических регистров - 24 регистра общего назначения и 24 регистра для переименования. 24 регистра подразделяются на 16 рабочих регистров и восемь регистров, соответствующих универсальным регистрам архитектуры х86: ЕАХ, ЕВХ, ЕСХ, EDX, EBP, ESP, ESI и ED1.

Планировщик Кб содержит в буфере 24 команды RISC 86 и назначает инструкции на выполнение семи исполнительным устройствам:

- модулю сохранения; модулю загрузки; модулю перехода; двум целочисленным АЛУ; целочисленному блоку мультимедийных команд;блоку операций с плавающей точкой.

Наличие буфера позволяет планировщику в динамике анализировать и изменять выбранную для исполнения последовательность команд, обеспечивая максимальную загрузку исполнительных устройств.Блок мультимедийных команд выполняет все инструкции расширения ММХ. Целочисленный Х-блок выполняет арифме- тико-логические операции, включая умножение, деление, сдвиг, циклический сдвиг. Y-блок - основные одно- и двухсловные арифметико-логические операции: ADD, AND, CMP, OR, SUB, XOR, расширение нуля и расширение знакового разряда числа. Блок вычислений с плавающей точкой выполняет все команды с плавающей точкой. Блок переходов осуществляет обновление состояния процессора (регистров, флагов) после подтверждения предсказанного условного ветвления, обеспечивая тем самым возможность спекулятивного выполнения команд (на глубину до семи переходов).

Микропроцессор К7 (кодовое имя Athlon) начал выпускаться в 1999 г. сначала по технологии 0,25 мкм (22 млн транзисторов на кристалле), затем - 0,18 мкм (37 млн транзисторов на кристалле).Архитектура, реализованная в Athlon, получила название QuantiSpeed. Она включает в себя суперскалярное конвейерное выполнение команд, конвейерный блок вычислений с плавающей точкой, аппаратную предвыборку данных в кэш-память и усовершенствованную технологию предсказания ветвлений.

Athlon имеет девять исполнительных блоков: три для обработки целочисленных данных, три для вычисления адреса и три блока для вычислений с плавающей точкой и обработки мультимедийных данных (один для загрузки/сохранения данных с плавающей точкой и два конвейерных блока для исполнения команд). Длина целочисленного конвейера составляет 10 стадий, конвейера с плавающей точкой - 15 стадий (в предыдущих моделях FPU не был конвейеризированным). Команда FPU Athlon позволяет одновременно выполнять до двух команд с плавающей точкой.Athlon может декодировать три команды х86 в шесть RISC- операций. После декодирования ROP попадают в буфер, где ожидают своей очереди на выполнение в одном из функциональных блоков процессора. Буфер К7 содержит 72 операции (в три раза больше, чем у Кб) и выдает 9 ROP для 9 исполнительных устройств.

Увеличенная до 2048 позиций таблица предсказания переходов (в два раза больше, чем у Pentium III) и усовершенствованный алгоритм предсказания позволяют давать правильный прогноз в 95 % случаев (у Pentium III всего 90 %).Athlon имеет 128 Кб кэш-памяти первого уровня (64 Кб для данных и 64 Кб для команд). Для взаимодействия с кэш-памятью второго уровня предусмотрена специальная шина (как у архитектуры Р6 Intel). Кэш-память второго уровня размером 512 Кб расположена вне процессорного ядра - в процессорном картридже, и работает на половинной частоте ядра.Использование при производстве процессора Athlon технологии 0,18 мкм с медными соединениями позволило разработчикам разместить на кристалле кэш-память второго уровня размером 256 Кб, работающую на тактовой частоте ядра.Разновидностью микропроцессора с архитектурой К7 стал Duron - бюджетный вариант микропроцессора, ориентированный на дешевые ПК. Основным его отличием является уменьшенная до 64 Кб кэш-память второго уровня. Микропроцессор Duron содержит 25 млн транзисторов на кристалле.

Благодаря примененным в К7 новым архитектурно-техническим решениям микропроцессорам AMD удалось на 7-10% превысить производительность Pentium III при равных тактовых частотах.

Дальнейшее совершенствование архитектуры и технологии производства микропроцессоров в рамках семейства К7 привело к появлению двух новых версий Athlon: Athlon ХР и Athlon MP.

Процессор Athlon ХР имеет целый ряд преимуществ:

-расширен набор инструкций; -благодаря усовершенствованному ядру Athlon ХР потребляет на 20 % меньше мощности, чем Athlon при той же частоте;

-усовершенствован алгоритм предсказания ветвлений; улучшен механизм опережающей загрузки инструкций из основной памяти в кэш; модифицирован буфер преобразования адресов TLB; в процессор встроен термодатчик, позволяющий определять температуру кристалла.

Данный микропроцессор ориентирован на использование в высокопроизводительных персональных компьютерах; и особую эффективность, по мнению разработчиков, он должен проявлять при работе с операционной системой Windows ХР (отсюда и ХР в названии процессора).

Процессор содержит 54,3 млн транзисторов на кристалле. Производился Athlon ХР изначально по технологии 0,18 мкм, а затем -0,13 мкм с использованием медных проводников.

Athlon MP предназначен для использования в серверах и мощных рабочих станциях и предусматривает возможность работы в двухпроцессорной конфигурации.