- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

29. Микропроцессоры с архитектурой iа-64

Микропроцессор Itanium является первым представителем 64-разрядных микропроцессоров фирмы Intel. Фактически же данный микропроцессор является детищем совместных усилий двух фирм: Intel и Hewlett-Packard (фирма Hewlett-Packard в свое время «поглотила» фирмы DEC и Compaq), которые в этом проекте объединили свои интеллектуальные и финансовые ресурсы. Первоначально микропроцессор имел мнемоническое обозначение Р7, затем - Merced (сокращение от слова Mercedes) и только потом - Itanium. Выпуск процессора был начат в 2001 г.

Наряду с микропроцессорами фирмы Intel, предшественниками Itanium можно считать и микропроцессоры с архитектурой Precision Architecture, разработанной фирмой Hewlett-Packard для своих RISC-процессоров. Ее 32-разрядный микропроцессор

Таблица

5.1

Х86

IA-64

Использование

сложных инструкций переменной длины,

обрабатываемых по одной

Использование

простых инструкций, сгруппированных

по три, одинаковой длины

Переупорядочивание

и оптимизация инструкций во время

выполнения

Переупорядочивание

и оптимизация инструкций во время

компиляции

Реализация

механизма предсказания переходов

Исполнение

нескольких последовательностей

команд одновременно без предсказания

переходов

Загрузка

данных из памяти по мере необходимости

Загрузка

данных до того, как они потребуются

РА-8000 имел 64-разрядную четырехконвейерную архитектуру с оригинальной схемой изменения последовательности выполняемых команд. Процессор содержал 10 функциональных устройств: два целочисленных АЛУ, два целочисленных устройства сдвига/объединения, два устройства умножения/накопления с плавающей точкой, два устройства деления/извлечения корня и два устройства загрузки/сохранения.

В РА-8000 использовался буфер переупорядочивания команд, просматривающий следующие 56 команд в потоке инструкций и определяющий, какие из них можно выполнять параллельно. Фактически буфер состоял из двух блоков на 28 команд каждый.

Команда, помещенная в буфер, ожидала готовности данных, являющихся результатом предыдущих команд, и выбиралась на выполнение (в порядке очередности), как только все требуемые данные получены и необходимое исполнительное устройство освободилось. Каждый из блоков буфера позволял планировать две команды за такт (итого до четырех команд за такт). Для устранения связей между параллельно выполняемыми командами в процессоре использовалось переименование регистров.

Hewlett-Packard спроектировала РА-8000 специально для научных и инженерных расчетов, при которых объем интенсивно используемых данных может быть велик. В этой связи возникла необходимость использования больших кэш-памятей команд и данных. РА-8000 использовал внешние основные кэшпамяти данных и команд объемом до 4 Мб, а также буфер переупорядочивания адресов, отслеживающий все команды загрузки/сохранения, что позволило сократить задержку, связанную с адресацией внешней кэш-памяти.

Архитектура микропроцессора Itanium (IA-64) реализует концепцию EPIC (Explicitly Parallel Instruction Computing - явное параллельное выполнение команд).

Основными особенностями EPIC являются:

- большое количество регистров; масштабируемость по количеству функциональных устройств (возможность увеличения числа функциональных устройств в последующих моделях микропроцессора); явное задание параллелизма в машинном коде; предикатное исполнение инструкций; упреждающая загрузка данных по предположению.

В табл. 5.1 приведены основные отличия архитектуры процессора IA-64 от архитектуры процессора х86.

В микропроцессоре Itanium последовательность команд и план загрузки исполнительных устройств формируются на этапе компиляции. В ходе выполнения программы последовательность команд не изменяется. В микропроцессоре используются: динамическое предсказание переходов, спекулятивное (по предположению) исполнение команд, аппаратная поддержка конвейерного выполнения циклов, отложенные операции обращения к памяти, предварительная загрузка данных в кэш.

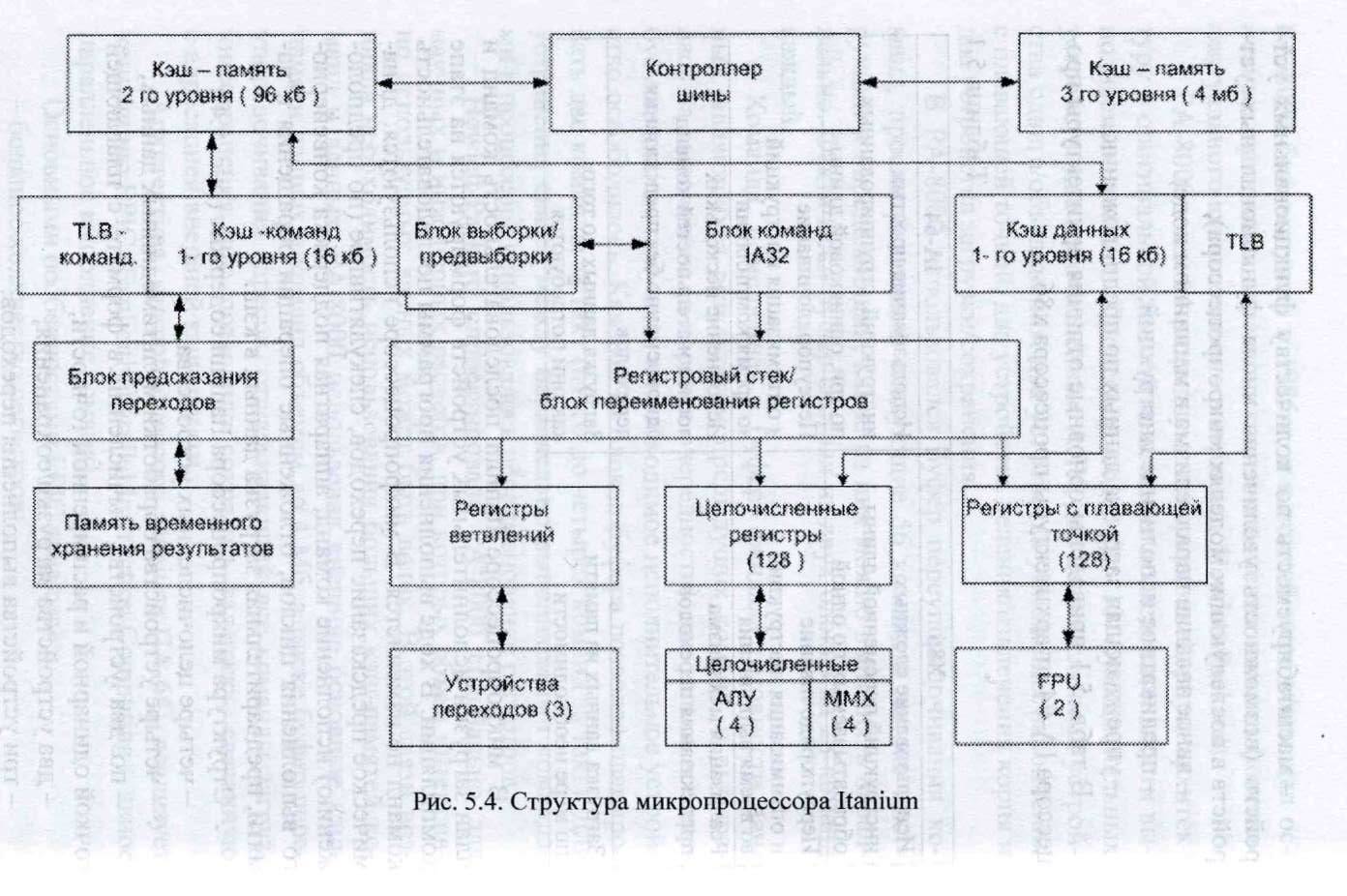

Структура микропроцессора Itanium содержит (рис. 5.4):

- четыре целочисленных устройства; четыре устройства обработки мультимедийных данных; по два устройства вычислений в формате с плавающей точкой одинарной и расширенной точности; два устройства загрузки/сохранения; три устройства выполнения переходов.

Все функциональные устройства микропроцессора конвейеризированы. Команда выполняется за 10 тактов, причем одновременно в микропроцессоре может выполняться до шести команд. Для повышения эффективности функционирования исполнительных блоков микропроцессора результаты выполнения команды передаются непосредственно на вход другой команды, минуя запись в регистры. Для этой цели используется память временного хранения результатов.

Процессор может напрямую адресовать до 18 Гб оперативной памяти. Itanium использует трехуровневую кэш-память:

-первый уровень — внутренняя раздельная кэш-память команд и данных, по 16 Кб каждая;

- второй уровень — внутренняя общая кэш-память команд и данных - 96 Кб;

-третий уровень — внешняя (в картридже) общая кэшпамять команд и данных - до 4 Мб.

Команды микропроцессора группируются компилятором в «связку» длиной 128 бит. Связка содержит три команды и шаблон, указывающий, какие команды в текущей и следующей связке могут выполняться одновременно Команды в связках могут размещаться в порядке, отличном от исходного, заданного в тексте программы, и могут быть как зависимыми (по управлению и данным), так и независимыми.

Команды микропроцессора имеют фиксированную длину 40 бит.

Формат команды приведен на рис. 5.5.

![]()

Рис. 5.5. Формат команды микропроцессора Itanium

Компилятор для микропроцессора Itanium использует технологию отмеченных ветвлений, сущность которой заключается в том, что команды, принадлежащие к различным ветвям алгоритма, помечаются различными значениями в поле предиката. Формирование связок команд осуществляется вне зависимости от значения предиката. Тем самым обеспечивается возможность одновременного выполнения команд, принадлежащих различным ветвям алгоритма.

В процессе выполнения программы после определения истинного направления ветвления вычислительного процесса сохраняются только результаты команд со значением предиката, соответствующим данной ветви.

Технология «отмеченных команд» существенно снижает негативное влияние ветвлений на машинном уровне.

Другой особенностью IA-64 является предварительная загрузка данных в кэш-память с разнесением во времени команд загрузки данных из памяти и команд, их использующих. Компилятор, анализируя исходный текст программы, заранее добавляет в формируемый исполняемый код команды загрузки необходимых данных и непосредственно перед командой, их использующей, - команду проверки их доступности. Таким образом удается в значительной степени сократить задержки, связанные с необходимостью ожидания загрузки требуемых данных.

В Itanium предусмотрена аппаратная поддержка выполнения циклов.

В микропроцессоре не используется динамическое переименование регистров. С целью обеспечения возможности конвейерного выполнения различных витков цикла в микропроцессоре применяется схема циклической замены используемых регистров («вращение регистров»): набор используемых в цикле регистров рассматривается как фрейм, отображаемый на регистровый файл, начиная с некоторой позиции - базы фрейма. При переходе на следующую итерацию цикла изменяется база фрейма на величину, равную количеству регистров во фрейме.

Микропроцессор Itanium II является вторым микропроцессором в семействе 64-разрядных микропроцессоров компании Intel. Itanium II рассчитан на применение в высокопроизводительных серверах и рабочих станциях.

Itanium II содержит кэш-память большой емкости: кэш третьего уровня емкостью 1,5 или 3 Мб, кэш второго уровня емкостью 256 Кб и кэш первого уровня емкостью 32 Кб. При размере кристалла 464 мм2 Itanium II содержит 221 млн транзисторов.Развитие технологии позволило на кристалле микропроцессора Itanium серии 9300 разместить уже миллиард транзисторов. За счет этого на кристалле располагаются четыре процессорных ядра, совокупная емкость трехуровневого кэша составила 30 Мб, а емкость оперативной памяти потенциально может быть равна 1 Тб. Разрядность виртуального адреса при этом составляет 64 бита, а физического - 50 бит. Межпроцессорный интерфейс обеспечивает скорость передачи до 48 Гб/с.