- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

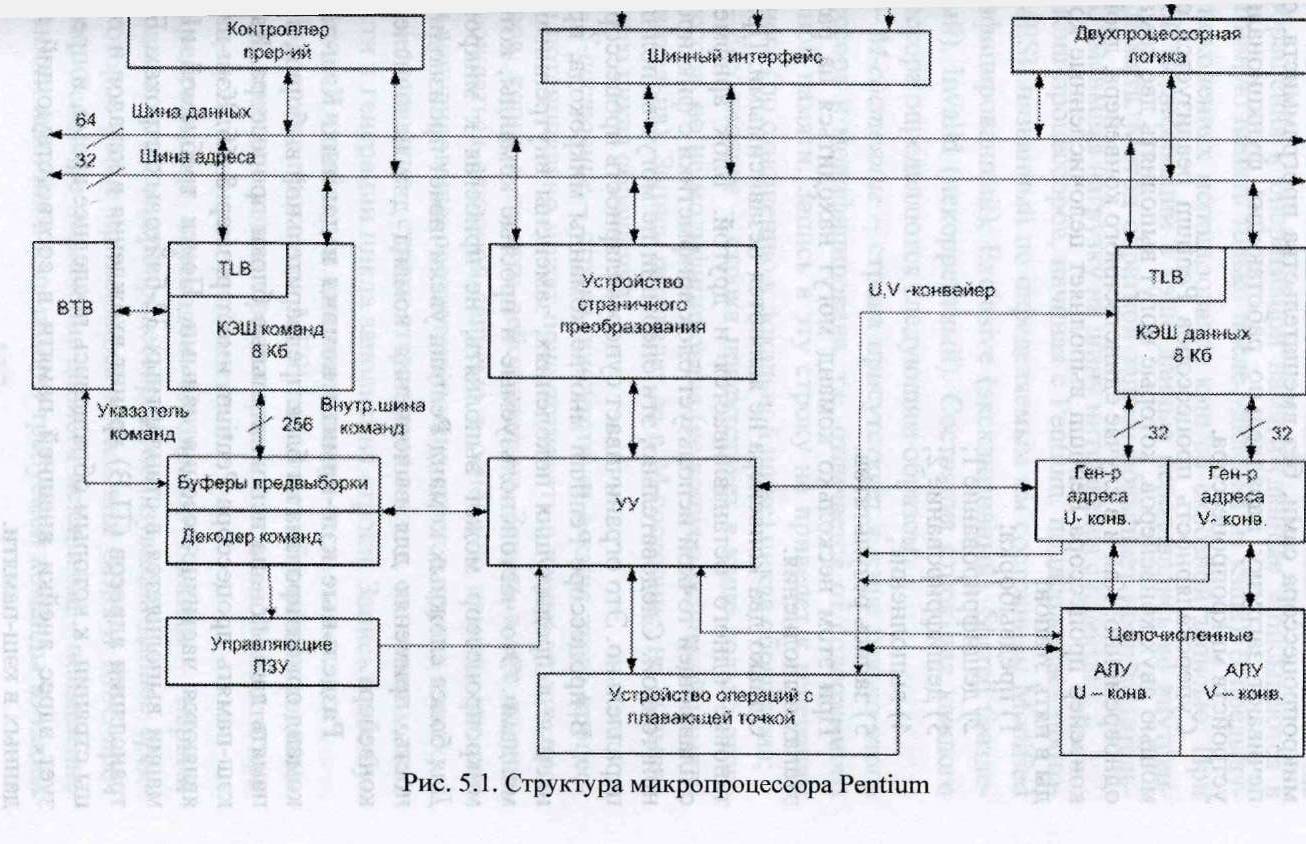

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

Проц.Pentium полностью программно совместим с пред. МП Intel и позволяет применять ранее разраб. ПО для ПК. Однако проц. семейства Pentium облад. целым рядом технич. новшеств, а именно:

- близкая к суперскалярной архитектура;

- раздельные кэш-памяти для команд и данных;

- предсказание переходов;

- высокопроизводительные операции с плавающей точкой:

- усовершенствованная 64-разрядная шина данных;

- средства обеспечения целостности данных;

- SL-технология со средствами управления энергопотреблением;

- поддержка многопроцессорности;

- мониторинг производительности;

- поддержка различных страниц памяти.

Суперскалярная архитектура. Процессор относится к классу суперскалярных, когда система команд не содержит никаких указаний на параллельную обработку внутри процессора. Основная идея, опред. развитие суперскалярных МП, состоит в построении возможно большего количества параллел. структур при сохр. традиционных последов. программ.

Т.е. предполаг., что компиляторы и аппаратура МП сами, без вмешательства программиста, обеспечивают загрузку параллельно работающих функц. устройств МП.

Суперскалярность процессоров Pentium реализуется с помощью двух конвейеров, которые могут вып. 2 команды одновременно. Как и в случае единственного конвейера, двойной конвейер процессора Pentium выполняет целочисленные команды в пять этапов:

1. предвыборка;

2. дешифрирование 1;

3. дешифрирование 2;

4. выполнение;

5. запись результатов.

При этом несколько команд могут находиться на разных этапах выполнения.

Однако два конвейера не являются независимыми. При остановке одного останавливается и другой. Блок арифметики с плавающей точкой использует блок арифметики с фиксированной точкой. Следовательно, эти операции не могут выполняться параллельно. Это ограничивает суперскалярность процессора. В процессоре Pentium многие команды микрокода, применяемые в предыдущих поколениях, заменены внутренними командами. Это частоиспользуемые и простые команды, которые микропроцессор может выполнять, не прибегая к микрокоду. Для более сложных команд Pentium увеличивает производительность, применяя для выполнения команд два целочисленных конвейера.

Раздельные кэш-памяти команд и данных. Кэш-память команд ориентирована на блок предвар. выборки, а кэш-память данных - на исполнительные блоки процессора. Каждая кэш-память процессора Pentium имеет размер 8 Кб. Кэш-памяти явл. частично-ассоциативными. Поиск требуемой информации вып. в стандартных 32-байтовых строках. Буфер трансляции адресов (TLB) хранит вхождения в каталог и таблицы страниц, к которым обращались последнее время, и преобразует адрес ячейки внешней памяти в соответ. адрес данных в кэш-памяти. Кэш-память данных процессора Pentium исп. метод «обратной записи». Он позволяет модифицировать данные в кэше без обращения к оперативной памяти (данные записываются в оперативную память только после удаления из кэша). В предыдущих поколениях исп. кэш со сквозной записью. При каждой модификации в кэше данные передавались во внутреннюю память. Метод обратной записи повышает производительность, уменьшая нагрузку на шину интерфейса с памятью. Кэш процессоров, начиная с Pentium, поддерживает протокол MESI, названный по определяемым им состояниям Modified (модифицированный), Exclusive (эксклюзивный), Shared (разделенный), Invalid (некорректный). Состояния строк для каждого процессора определяются следующим образом:

- М-состояние - строка присутствует в кэше только этого процессора и модифицирована, т.е. отличается от содержимого основной памяти. Запись в эту строку не приведет к генерации внешнего (по отношению к локальной шине) цикла обращения;

- Е-состояние - строка присутствует в кэше только этого процессора, но не модифицирована (ее копия в основной памяти действительна). Запись переведет ее в М-состояние, не вызывая внешнего цикла обращения;

- S-состояние - строка присутствует в кэше этого процессора и потенциально может присутствовать в кэшах других процессоров, копия в памяти действительна. Запись в нее должна сопровождаться сквозной записью в основную память, что повлечет аннулирование соответствующих строк в других кэшах;

- 1-состояние - строка отсутствует в кэше, ее чтение может привести к генерации цикла заполнения строки. Запись в нее будет сквозной и выйдет на внешнюю шину.

Поддержка протокола MESI позволяет обеспечить согласованность данных в кэшах процессоров и в основной памяти при работе в мультипроцессорной системе.