- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

20. Функциональные устройства микропроцессора Intel 80486

Устройство предвыборки команд. Циклы предвыборки команд считывают 16-байтные блоки команд, начиная с адресов, численно больших адреса последней выбранной команды. Начальный адрес формирует устройство предвыборки, которое напрямую соединено с устройством страничного преобразования. 16-байтные блоки предварительной выборки одновременно подаются в устройство предвыборки и кэш-память. В устройстве предвыборки имеется очередь предвыборки, которая хранит 32 байта команд. Когда каждая команда считывается из очереди, ее код операции подается в устройство дешифрирования команд, а смешение подается в устройство сегментации, где участвует в вычислении адреса. Если в выполняемой программе встречаются циклы, устройство предвыборки получает копии ранее выполненных команд из кэш-памяти. Запрос шины от устройства предвыборки имеет низший приоритет. Устройство предвыборки очищается, когда нарушается естественный порядок выполнения команд, например: при переходах, переключениях задач, особых случаях и прерываниях.Устройство предвыборки никогда не обращается за конец сегмента кода и к странице, которая не присутствует в памяти. Чтобы предотвратить опережающее считывание за конкретный адрес, команды не должны быть ближе к этому адресу на один байт плюс один выровненный 16-байтный блок.

Устройство дешифрирования команд. Устройство дешифрирования команд получает команды от устройства предвыборки и в двухступенчатом процессе преобразует их в управляющие сигналы низкого уровня и точки входа микрокода, т.е. микропрограмм.Устройство дешифрирования команд одновременно обрабатывает байты префиксов команд, коды операций, байты адресации и смещения.Устройство очищается при каждой очистке устройства предвыборки команд.

Устройство управления интерпретирует слово команды и точки входа микрокода, полученные от устройства дешифрирования команд. Оно имеет выходы для управления целочисленным устройством и устройством с плавающей точкой, а также управляет сегментацией, так как команды могут определять выбор конкретного сегмента.

Устройство управления содержит микрокод (управляющие микропрограммы) процессора.

Целочисленное операционное устройство (тракт данных) идентифицирует, где хранятся данные, и выполняет все арифметические и логические команды из системы команд. Оно имеет восемь программно-доступных 32-битных регистров общего назначения, несколько специализированных регистров, арифметико-логическое устройство и параллельный сдвигатель, обеспечивающий сдвиг в любом направлении и на любое число разрядов. Команды загрузки, сохранения, сложения, вычитания, логических операций и сдвигов выполняются за один такт.

Целочисленное устройство и устройство с плавающей точкой соединены двумя 32-битными двунаправленными шинами, которые применяются совместно для передач 64-битных операндов. Содержимое регистров общего назначения подается по отдельной 32-битной шине в устройство сегментации для формирования эффективных адресов.

Устройство с плавающей точкой имеет такую же систему команд и набор регистров, как арифметический сопроцессор. Оно содержит регистровый стек из восьми 80-битных регистров и специализированные схемы для интерпретации 32/64/80- битных форматов чисел, определенных в стандарте IEEE 754. Выходной сигнал на шине процессора сообщает внешней подсистеме об ошибках с плавающей точкой, а она может подать в процессор входной сигнал, показывающий, что процессор должен игнорировать ошибки и продолжать обычные операции.

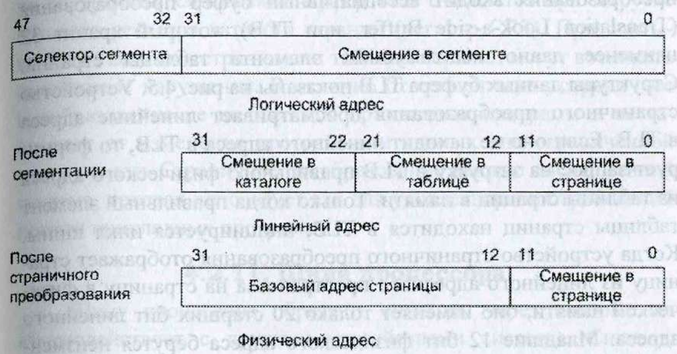

Устройство сегментации. Под сегментом понимается защищенное независимое адресное пространство. Сегментация применяется для изолирования прикладных программ, вызова процедур восстановления и локализации влияния ошибок программирования.Устройство сегментации преобразует сформированный программой сегментированный адрес, называемый логическим или виртуальным адресом, в несегментированный линейный адрес. Местонахождения и атрибуты сегментов в линейном адресном пространстве хранятся в структурах данных, называемых дескрипторами сегментов. Устройство сегментации производит вычисление адреса, привлекая дескрипторы сегментов и смещения, выделенные из команд. После этого линейные адреса посылаются в устройство страничного преобразования и кэш-память. Параллельно с вычислением линейного адреса производится контроль атрибутов сегмента.При обращении к сегменту первый раз его дескриптор копируется во внутренний регистр процессора и в дальнейшем при необходимости берется из этого регистра. Программа может иметь до 16383 сегментов. В любой момент времени во внутренних регистрах процессора могут находиться до шести дескрипторов сегментов. На рис. 4.4 показаны взаимосвязи между логическим, линейным и физическим адресами памяти.

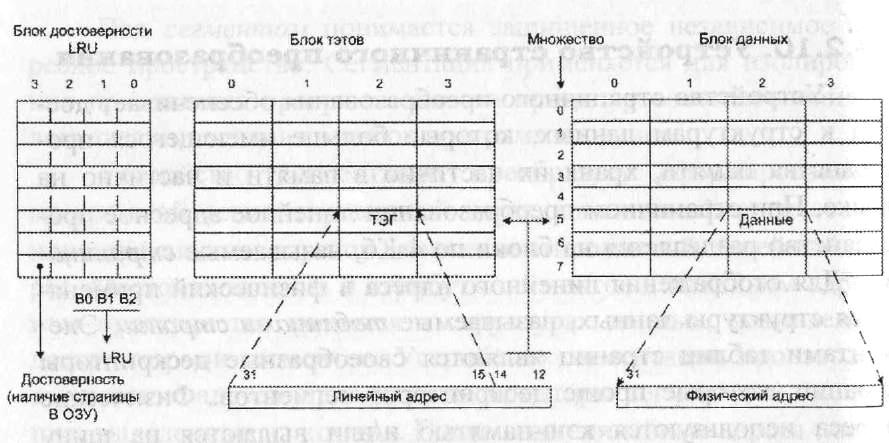

Устройство страничного преобразования обеспечивает доступ к структурам данных, которые больше имеющегося пространства памяти, храня их частично в памяти и частично на диске. При страничном преобразовании линейное адресное пространство разделяется на блоки по 4 Кб, называемые страницами. Для отображения линейного адреса в физический применяются структуры данных, называемые таблицами страниц. Элементами таблиц страниц являются своеобразные дескрипторы страниц, которые проще дескрипторов сегментов. Физические адреса используются кэш-памятью и/или выдаются на шину процессора. Устройство страничного преобразования фиксирует такие ситуации, как обращение к странице, отсутствующей в памяти, и формирует особые случаи, называемые страничными нарушениями. При страничном нарушении операционная система должна передать нужную страницу с диска в память. При необходимости она может освободить пространство в памяти, отсылая некоторую другую страницу на диск. Если страничное преобразование программно запрещено, физический адрес совпадает с линейным адресом. В устройство страничного преобразования входит ассоциативный буфер преобразования (Translation Look-a-side Buffer, или TLB), который хранит 32 наименее давно используемых элемента таблицы страниц. Структуры данных буфера TLB показаны на рис. 4.5. Устройство страничного преобразования просматривает линейные адреса в TLB. Если оно не находит линейного адреса в TLB, то формирует запрос на загрузку в TLB правильного физического адреса из таблицы страниц в памяти. Только когда правильный элемент таблицы страниц находится в TLB, инициируется цикл шины. Когда устройство страничного преобразования отображает страницу из линейного адресного пространства на страницу в физической памяти, оно изменяет только 20 старших бит линейного адреса. Младшие 12 бит физического адреса берутся неизменными из линейного адреса.

Рис. 4.5. Организация буфера TLB

В качестве стратегии замещения в буфере TLB применяется такой же алгоритм псевдо-LRU, как и во внутренней кэш-памяти. Буфер TLB очищается при загрузке базового регистра каталога страниц. Страничное преобразование не видимо для прикладных программ и не защищает от изменения программами данных вне ограниченной части памяти. Страничное преобразование видимо операционной системе, которая использует его для удовлетворения требований памяти прикладных программ.