- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

18. Шинный интерфейс и шина микропроцессора Intel 80486.

Это устройство учитывает приоритеты обращений к шине и координирует передачи данных, осуществляет предвыборку команд и выполняет функции согласования действий между внутренними устройствами процессора и внешней системой. На внутренней стороне это устройство взаимодействует с кэш-памятью и устройством предвыборки по трем 32-битным шинам. На внешней стороне шинный интерфейс формирует сигналы шины процессора. За исключением сигналов определения цикла, все циклы внешней шины (считывание из памяти, предвыборки команд, заполнение строк кэш-памяти и др.) выглядят для внешних схем обычными циклами процессора, причем все циклы имеют одинаковую временную диаграмму. В составе шинного интерфейса имеются следующие компоненты:

- драйверы адреса для формирования сигналов адреса и сигналов разрешения байт. Старшие 28 сигналов адреса являются двунаправленными, позволяя внешней схеме передать в процессор адрес строки кэш-памяти, содержимое которой объявляется недостоверным;

- приемопередатчики шины данных, предназначенные для управления двунаправленными сигналами данных шины процессора;

- схемы для управления (по тактам синхронизации) размером шины данных. Можно задать три размера внешней шины данных: 32, 16 и 8 бит.

- буферы записи, обеспечивающие буферирование до четырех запросов записи, что позволяет продолжать многие внутренние операции, не ожидая окончания циклов записи на шине процессора;

- схемы формирования циклов шины и управления шиной, которые реализуют большой набор циклов шины и управляющих функций, включая пакетные передачи, непакетные передачи (одно- и многотактные), арбитраж шины (запрос шины, захват шины, подтверждение захвата шины, блокировка шины, псевдоблокировка шины и отступление шины). Два программно-управляемых выхода обеспечивают кэширование страниц по тактам. Предусмотрены один вход и один выход для управления пакетными считываниями;

- схемы формирования и контроля паритета (четности), с помощью которых бит паритета формируется при записи и контролируется при считывании. Сигнал ошибки фиксирует ошибку паритета при считывании;

- схемы управления кэш-памятью поддерживают операции управления и согласования кэш-памяти. Три входа позволяют внешней системе управлять согласованностью данных, хранимых во внутренней кэш-памяти. Два специальных цикла шины предоставляют процессору возможность управлять согласованностью внешней кэш-памяти.

В ходе предвыборки команд шинный интерфейс считывает команды с шины процессора и передает их в устройство предвыборки команд и кэш-память. Устройство предвыборки команд после этого может получать команды непосредственно из кэш-памяти.

Шинный интерфейс имеет временные регистры для буферирования до четырех 32-битных передач записи в память. Можно буферировать адреса, данные или управляющую информацию. После буферирования запроса записи внутреннее устройство, сформировавшее запрос, освобождается для продолжения обработки. Если не ожидается запрос с более высоким приоритетом и шина свободна, на шине процессора сразу же инициируется цикл записи. Когда заполнены все четыре буфера записи, все последующие передачи записи ожидают в процессоре освобождения буфера записи.

Шинный интерфейс может пропускать ожидающие запросы считывания вперед буферированных записей. Объясняется это тем, что ожидающие считывания могут задержать работу внутреннего устройства, а ожидающие записи не оказывают заметного воздействия на скорость обработки. Записи передаются на шину процессора в том же порядке, в котором они были получены от внутренних устройств («первый пришел - первый ушел»). Однако сформированный впоследствии запрос считывания (данных или команды) может быть пропущен раньше буферированных записей. Для защиты от считывания неверных данных пропускание считываний раньше буферированных записей разрешается, если только все буферированные записи привели к попаданию в кэш-памяти. Так как внешнее считывание формируется только при промахе в кэш-памяти, любое считывание на внешней шине с рассмотренным средством защиты никогда не приведет к считыванию из той ячейки, в которую будет производиться буферированная запись. Для конкретного набора буферированных записей такое «пропускание вне очереди» можно произвести только один раз, так как возвращаемые при считывании данные могут заменить данные, готовые к записи из буферов записи. Чтобы для конкретного набора буферированных записей «пропускание вне очереди» происходило не более одного раза, все буферированные записи при пропускании вперед запроса считывания отмечаются как промахи в кэш-памяти. Отмеченные таким образом буферированные записи передаются на шину процессора ранее следующего запроса считывания. При объявлении данных во внутренней кэш-памяти недостоверными все ожидающие запросы также отмечаются как промахи в кэш-памяти. Запрещение кэш-памяти запрещает и буферы записи, что устраняет возможность изменения порядка циклов шины.

Для поддержания целостности данных накладываются некоторые ограничения на передачи к ячейкам ввода-вывода:

- считывания ввода-вывода никогда не кэшируются (состояние устройств может меняться асинхронно по отношению к процессору);

- считывания ввода-вывода никогда не производятся раньше буферированных записей в память. Благодаря этому процессор закончит модификацию всех ячеек памяти до считывания состояния из устройства (если при операции ввода-вывода потребуется обработка прерывания, то данные могут потеряться);

- одиночные записи ввода-вывода никогда не буферируются.

Следовательно, при выполнении команды OUT внутренние операции прекращаются до завершения на шине процессора всех буферированных записей и записи ввода-вывода. При этом внешней схеме отводится время сформировать цикл недостоверности кэш-памяти или замаскировать прерывания до выполнения процессором следующей команды. Процессор закончит модификацию всех ячеек памяти перед записью в ячейку ввода-вывода. Повторяющиеся команды OUT можно буферировать, так как в этом случае состояние внешних устройств не изменяется.

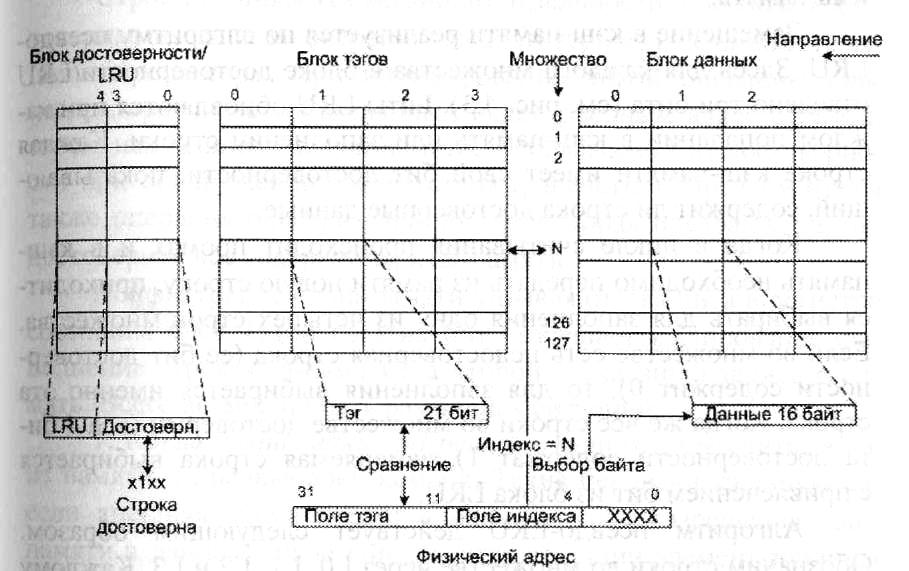

19. Внутренняя кэш-память хранит копии последних считанных команд, операндов и других данных. Когда процессор запрашивает информацию, уже находящуюся в кэш-памяти (попадание), цикл шины не нужен. Когда же процессор запрашивает информацию, отсутствующую в кэш-памяти (промах), информация считывает-ся в кэш-память за одну или несколько 16-байтных кэшируемых передач данных(заполнение строки кэш-памяти). Если формируется запрос записи в область в кэшпамяти, выполняются действия(сквозная запись): обновляется кэш-память;записываемые данные передаются в основную память. Кэш-память имеет четырехканальную ассоциативную по множеству организацию. Четырехнаправленная ассоциативность является компромиссом между быстродействием кэш-памяти с прямым отображением при попаданиях и большим коэффициентом попаданий полностью ассоциативной кэш-памяти. Блок данных в 8 Кб разделен по четырем направлениям, каждое из которых имеет 128 16-байтных строк кэшпамяти. Строка кэш-памяти содержит данные из 16 соседних байтных адресов в памяти, начиная с адреса, кратного 16. Адресация кэш-памяти осуществляется путем разделения старших 28 бит физического адреса на три части. Семь бит поля индекса определяют номер множества из 128 множеств в кэш-памяти. Старшие 21 бит являются полем признака, эти биты сравниваются с тэгами каждой строки в индексированном множестве и показывают, хранится ли 16-байтная строка кэш-памяти по данному адресу. Младшие четыре бита физического адреса выбирают байт внутри строки кэш-памяти. Находящееся в блоке достоверности/LRU (Least Recently Used) 4-битное поле достоверности показывает, являются ли в данный момент кэшированные данные по имеющемуся адресу достоверными. Когда при считывании возникает промах, в кэш-память записывается 16-байтный блок, содержащий запрошенную информацию.

Организация внутренней кэш-памяти

В кэш-памяти реализован принцип сквозной записи. Заполнение строки выполняется только при промахе в операции считывания. Когда в процессоре разрешены обычное кэширование и сквозная запись, каждая внутренняя запись в кэш-память обновляет содержимое кэш-памяти и передается в устройство шинного интерфейса и по шине процессора записывается в память.

Замещение в кэш-памяти реализуется по алгоритму псевдо-LRU. Здесь для каждого множества в блоке достоверности/LRU отведено три бита (см. рис. 4.3). Биты LRU обновляются при каждом попадании в кэш-память или заполнении строки. Каждая строка кэш-памяти имеет свой бит достоверности. Когда в цикле считывания происходит промах, приходится выбирать для заполнения одну из четырех строк множества. Если во множестве есть недостоверная, то для заполнения выбирается именно эта строка. Когда же все строки во множестве достоверны, заменяемая строка выбирается с привлечением бит из блока LRU. Алгоритм псевдо-LRU действует следующим образом: Обозначим строки во множестве через L0, LI, L2 и L3. Каждому множеству в блоке LRU соответствуют три бита ВО, В1 и В2, которые модифицируются при каждом попадании и заполнении следующим образом:

-если последнее обращение в множестве было к строке L0 или L1, то бит ВО устанавливается в состояние 1, а при обращении к строке L2 или L3 бит ВО сбрасывается в 0;

-если последнее обращение в паре L0-L1 было к строке L0, то бит В1 устанавливается в состояние 1, а при обращении к строке L1 бит В1 сбрасывается в 0;

-если последнее обращение в паре L2-L3 было к строке L2, то бит В2 устанавливается в состояние 1, а при обращении к строке L3 бит В2 сбрасывается в 0. Выбор заменяемой строки (когда все строки в множестве достоверны) определяет содержимое бит ВО, В1 и В2 (табл. 4.1)

Таблица 4.1

![]()

Строки кэш-памяти можно по отдельности объявить недостоверными, задавая операцию недостоверности кэш-памяти на шине процессора. При инициировании такой операции кэшпамять сравнивает объявляемый недостоверным адрес с тэгами строк, находящихся в кэш-памяти, и сбрасывает бит достоверности при обнаружении соответствия. Конфигурацией кэш-памяти управляют два бита в регистре состояния CR0. Один из этих бит разрешает кэширование (заполнение строк кэш-памяти), а второй - сквозную запись в память. Всего возможно пять различных ситуаций:

1)Когда кэширование разрешено, кэшируются считывания из памяти и предвыборки команд. Такие передачи кэшируются, если внешняя схема подаст входной сигнал разрешения кэшпамяти в данном цикле шины и если текущий элемент таблицы страниц разрешает кэширование.

2)В тех циклах, где кэширование запрещено при промахе, заполнение строки кэш-памяти не производится. Кэшпамять продолжает действовать, несмотря на то, что она запрещена для заполнения. Уже находящиеся в кэш-памяти данные используются, если они являются достоверными. Только когда все данные в кэш-памяти отмечены как недостоверные, что происходит при очистке кэш-памяти, все внутренние запросы считывания приводят к формированию внешних циклов шины.

3)Когда разрешена сквозная запись, все записи, включая и вызвавшие попадания, инициируют запись в память. Операции недостоверности удаляют строку из кэш-памяти, если адрес недостоверных данных отображается на строку кэш-памяти.

4)Когда сквозная запись запрещена, внутренний запрос записи, вызвавший попадание в кэш-памяти, не приводит к производству записи в память, а операции недостоверности запрещены.

5)Когда запрещены кэширование и сквозная запись, кэшпамять можно использовать как быстродействующее статическое ОЗУ. В такой конфигурации на шину процессора передаются только записи, вызвавшие промах, а операции недостоверности игнорируются.