- •1. Классификация, назначение и основные характеристики микропроцессоров.

- •2. Стандартизация архитектур микропроцессоров.

- •1. Архитектурно независимая спецификация программ

- •2. Java-технология, предложенная компанией sun

- •3. История развития и основные параметры микропроцессоров семейства Intel х86.

- •4. Минимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •5. Максимальный режим работы микропроцессора Intel 8086. Функциональное назначение выводов.

- •6. Структура микропроцессора Intel 8086.

- •7. Организация памяти микропроцессора Intel 8086.

- •8. Организация ввода-вывода и система прерываний микропроцессора Intel 8086.

- •9. Работа мп Intel 8086 в минимальном режиме. Временные диаграммы.

- •10. Работа микропроцессора Intel 8086 в максимальном режиме. Временные диаграммы.

- •11. Построение центрального процессора на базе микропроцессора Intel 8086.

- •12. Подключение блоков памяти и внешних устройств при построении однопроцессорной системы на базе микропроцессора Intel 8086.

- •13. Характеристики и назначение выводов арифметического сопроцессора Intel 8087.

- •14. Форматы данных арифметического сопроцессора Intel 8087.

- •15. Структура арифметического сопроцессора Intel 8087.

- •16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

- •17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

- •18. Шинный интерфейс и шина микропроцессора Intel 80486.

- •20. Функциональные устройства микропроцессора Intel 80486

- •21. Основные понятия защищенного режима.

- •22. Система привилегий и организация защиты микропроцессора Intel 80486.

- •23. Режим виртуального микропроцессора 8086 (v86)

- •24. Режим системного управления sмм.

- •25. Структура микропроцессора Pentium. Особенности архитектуры (суперскалярность, раздельные кэши команд и данных).

- •26. Структура микропроцессора Pentium. Особенности архитектуры.

- •27. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium Рrо, Pentium II)

- •28. Особенности архитектуры микропроцессоров 6-го поколения семейства х86 фирмы Intel (Pentium III, Pentium IV)

- •29. Микропроцессоры с архитектурой iа-64

- •30. Микропроцессоры архитектуры х86 фирмы амd 5-го и 6-го поколений

- •31. Микропроцессоры амd с 64-разрядной архитектурой Opteron.

- •32. Микропроцессоры с архитектурой Alpha фирмы dес.

- •33. Микропроцессоры с архитектурой sparc фирмы Sun Microsystems.

- •34. Перспективы развития универсальных микропроцессоров.

16. Функционирование арифметического сопроцессора Intel 8087 в пассивном и активном режимах.

Арифметический сопроцессор 8087 может работать только в паре с центральным процессором 8086/8088, который должен быть установлен в максимальный режим. Система с сопроцессором не требует никакой дополнительной логики, отличающейся от той, которая используется в системе с максимальным режимом ЦП. Схема расширенного процессора получается простым объединением одноименных выводов АСП и ЦП с дополнительным использованием контроллера прерываний для организации взаимодействия выхода INT сопроцессора и входа INTR ЦП.

Пассивный режим. Взаимодействие процессоров начинается по сигналу RESET, длительность которого должна быть не менее четырех тактов CLK. Через несколько тактов ЦП производит выборку команд из памяти, начиная с адреса FFFFOh, а сопроцессор следит за его работой, находясь в пассивном режиме. Выбирать команды из памяти может только ЦП, но сопроцессор также получает все команды, записывая их в очередь из байтов команд, идентичную очереди ЦП, и контролирует выполнение команд центральным процессором. В этом режиме выводы S2-S0, A19/S6-A16/S3 и AD15-AD0 используются как входы. Как только в потоке команд появляется команда ESC, АСП начинает переходить из пассивного режима в активный.

Активный режим. Для перехода в активный режим сопроцессор должен установить момент начала выполнения действий, определенных командой ESC. Для этого он начинает анализировать код состояния очереди команд ЦП по линиям QS1, QS0. Как только появляется код QS1QS0 = 01, соответствующий первому байту команды, и этот байт содержит код ESC = 11011, сопроцессор переходит в активный режим.

Если команда ESC содержит указание о том, что операнд- источник размещен в памяти, то ЦП формирует адрес операнда и считывает слово данных. При этом АСП перехватывает 20-битовый адрес операнда, записывая его в регистр ЕР, и слово данных, записывая его в очередь из байтов операндов. При длине операнда более одного слова сопроцессор получает остальные слова самостоятельно, дополнительно запрашивая шину.

Если определенный в команде ESC адрес является адресом приемника, сопроцессор, перехватив этот адрес в регистр ЕР, игнорирует считанное ЦП слово данных, а позднее, выполнив команду, записывает результат по перехваченному адресу.

В любом случае, перейдя в активный режим, сопроцессор выдает сигнал занятости BUSY=1 на вход TEST ЦП. С этого момента оба процессора осуществляют параллельную работу, Сопроцессор выполняет действия, определенные командой ESC, а ЦП продолжает выполнение программы. При этом шиной управляет ЦП, и каждый раз, когда сопроцессору требуется обратиться к памяти, он должен запрашивать шину по одной из линий RQ/GT.

17. Общая характеристика семейства 32-разрядных микропроцессоров Intel x86. Структура и функционирование микропроцессора Intel 80486.

Первым МП с 32-разрядной сеткой в семействе Intel был процессор 80386, затем появился МП 80486. Эти процессоры вобрали все свойства 16-разрядных МП семейства для обеспечения программной совместимости с разработанным ранее программным обеспечением. Помимо увеличения длины разрядной сетки, эти МП имеют ряд свойств, отсутствующих в более ранних моделях. Сюда можно отнести следующие:

1. Преодолено жесткое ограничение на длину непрерывного сегмента памяти в 64 Кб. В защищенном режиме эта величина равна 4 Гб - пределу физически адресуемой памяти.

2. Реализована поддержка виртуальной памяти размером до 64 Тб.

3. Реализован встроенный блок управления памятью, поддерживающего механизмы сегментации и страничной трансляции адресов.

4. Обеспечена четырехуровневая система защиты памяти и ввода-вывода, встроенный механизм переключения задач.

5. Реализована поддержка расширенной системы команд.

6. Обеспечена возможность работы в двух режимах:

- в режиме реальной адресации (реальный режим), полностью совместимом с 8086, в котором возможна адресация к физической памяти размером до 1 МБ;

- в защищенном режиме виртуальной адресации (защищенный режим), в котором процессор позволяет адресовать до 4 Гб физической памяти, при этом каждая задача виртуально может адресоваться к памяти до 16 Тб. В защищенном режиме возможно выполнение задач в режиме виртуального процессора 8086 (виртуальный режим).

1. Процессоры могут оперировать с 8-, 16- и 32-битными операндами, строками байт, слов и двойных слов, а также с битами, битовыми полями и строками бит, что в предыдущих моделях сделать было невозможно.

2. В архитектуру процессоров введены средства отладки и тестирования.

Рассмотрим особенности 32-разрядных микропроцессоров на примере Intel 80486.

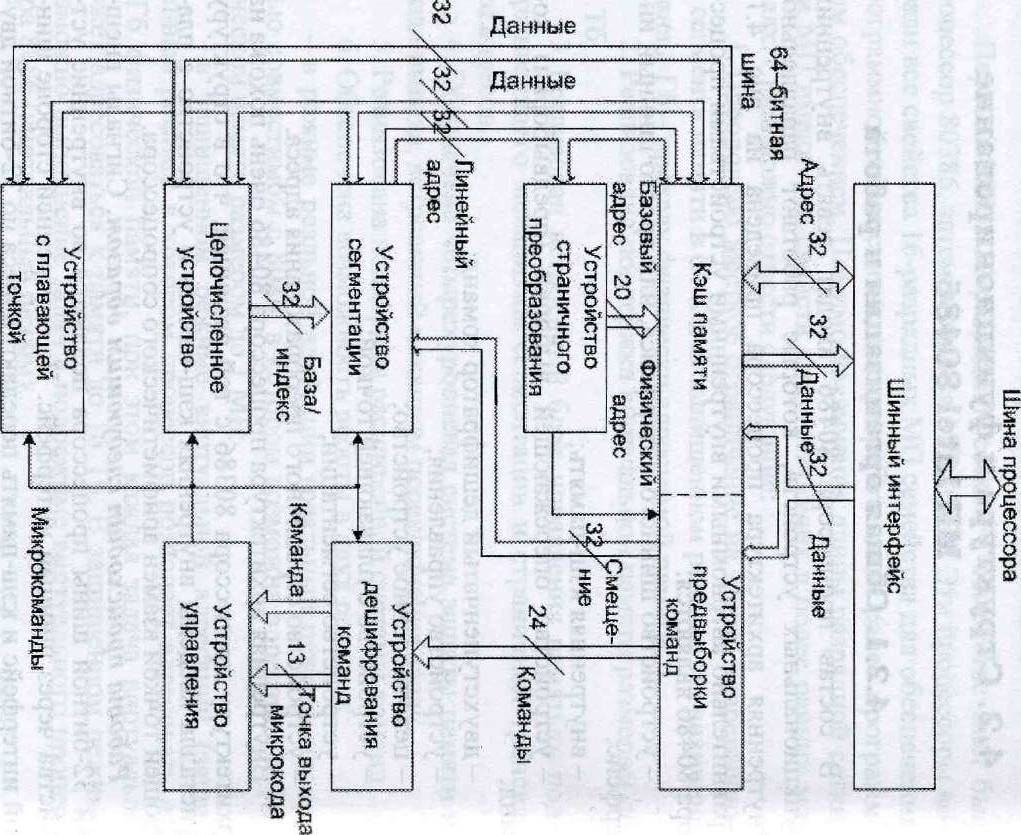

В состав процессора 80486 входят девять внутренних функциональных устройств, которые работают параллельно. Внутренняя архитектура процессора приведена на рис.4.1. Сравнительно автономными внутренними устройствами процессора 80486 являются:

устройство шинного интерфейса, или просто шинный интерфейс;

внутренняя кэш-память;

устройство опережающей выборки (предвыборки) команд;

двухступенчатый дешифратор команд;

устройство управления;

целочисленное устройство;

устройство с плавающей точкой;

устройство сегментации;

устройство страничного преобразования адреса.

Внутренняя архитектура процессора 80486 очень похожа на архитектуру процессора 80386 с той разницей, что в структуру кристалла введены внутренняя кэш-память и устройство с плавающей точкой взамен арифметического сопроцессора.

Работа происходит следующим образом. Сигналы внешней 32-битной шины процессора подаются во внутренние устройства через шинный интерфейс. На внутренней стороне шинный интерфейс и кэш-память передают адреса по 32-битной двунаправленной шине. Данные передаются из кэш-памяти в шинный интерфейс по 32-битной шине данных. Тесно связанные кэш-память и устройство предвыборки одновременно воспринимают выбранные с опережением команды из шинного интерфейса по разделенной 32-битной шине данных, которую кэш-память использует также для получения операндов. Находящиеся в кэш-памяти команды доступны устройству предвыборки, которое имеет 32-байтную очередь команд, ожидающих выполнения.

Рис. 4.1. Укрупненная структурная схема 32-разрядного микропроцессора Intel 80486.

Когда внутренние запросы данных или команд можно удовлетворить из кэш-памяти, сравнительно медленные циклы внешней шины процессора не выполняются. Шинный интерфейс привлекается, если операция требует обращения к шине процессора.

Дешифратор команд преобразует команды в управляющие сигналы низкого уровня и точки входа в микрокод (микропрограммы). Устройство управления выполняет микрокод и управляет целочисленным устройством, устройством с плавающей точкой и устройством сегментации. Результаты вычислений помещаются во внутренние регистры целочисленного устройства и устройства с плавающей точкой или в кэш-память. Кэш-память разделяет две 32-битные шины данных с устройством сегментации, целочисленным устройством и устройством с плавающей точкой. Эти две шины можно использовать совместно как 64-битную шину для передач между устройствами. Когда 64-битные дескрипторы сегментов передаются из кэш-памяти в устройство сегментации, 32 бита прямо передаются по одной шине данных, а другие 32 бита передаются через целочисленное устройство, поэтому все 64 бита достигают устройства сегментации одновременно.

Формирование адреса производят устройства сегментации и страничного преобразования. Логические адреса преобразуются устройством сегментации в линейные адреса, которые передаются в устройство страничного преобразования и кэш-память по 32-битной шине линейного адреса. Устройство страничного преобразования превращает линейные адреса в физические, которые направляются в кэш-память по 20-битной шине.

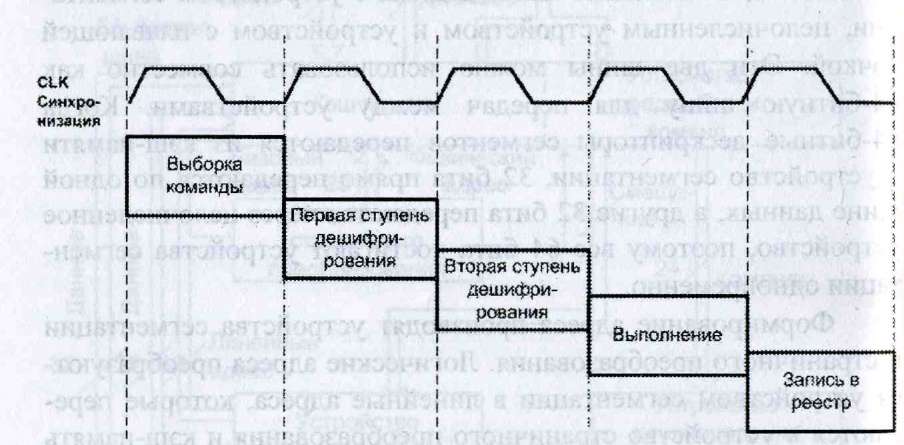

Не все команды требуют при своем выполнении участия всех внутренних устройств. Когда же команда требует участия нескольких устройств, каждое из них может обрабатывать параллельно другие команды на различных этапах выполнения. Несмотря на то, что каждая команда обрабатывается последовательно, в процессоре в различной стадии выполнения всегда находятся несколько команд. Одновременно выполняются операции, связанные с предвыборкой команд, дешифрированием команд, выполнением микрокода, а также целочисленные операции, операции с плавающей точкой, сегментации, страничного преобразования, управления кэш-памятью и шинного интерфейса. На рис.4.2 показан эффект параллелизма для одной команды. Каждый элемент в этом конвейере реализует свою функцию за один такт синхронизации. Внутренняя конвейеризация позволяет загрузить данные из кэш-памяти одной командой и использовать следующей командой уже в очередном такте синхронизации. Это объясняется наличием первой ступени дешифрирования, которая инициирует обращение к памяти до собственно выполнения. Так как в большинстве компиляторов и прикладных программ после команды загрузки находятся команды, оперирующие загруженными данными, подобный прием оптимизирует выполнение имеющихся программ.

Рис. 4.2. Конвейеризация команд

Однако в этом методе пришлось пойти на компромисс: последовательность команд, которая изменяет содержимое регистра, а затем использует этот регистр для обращения к памяти, длится три такта вместо двух. Но этот компромисс оказывается незначительным недостатком, так как большинство команд с обращением к памяти используют «устойчивое» содержимое указателя стека или указателя кадра, поэтому дополнительный такт требуется редко. Компиляторы часто вводят «буферную» команду между командой, которая изменяет регистр адреса, и командой, которая использует этот регистр.