- •3. Логические элементы цифровых устройств.

- •3.1. Построение логических элементов на транзисторных ключах

- •3.2. Построение логических элементов с использованием диодов

- •3.3. Монтажная логика

- •3.4. Цифровые элементы транзисторно-транзисторной логики (ттл)

- •3.4.1. Основы схемотехники элементов ттл

- •3.4.2. Ттл со сложным выходным каскадом.

- •3.5. Стандартные серии ттл

3. Логические элементы цифровых устройств.

Логические элементы (ЛЭ) реализуют элементарные булевы функции. Объединив ЛЭ определенным образом, можно построить устройство, выполняющее определенную функцию обработки или запоминания информации. Один или несколько логических элементов выполненных на одном кристалле представляют собой интегральную схему (ИС).

Логические ИС выпускаются сериями. Это совокупности логических схем (микросхем), выполняющих различные логические функции, имеющих единые электрические и конструктивные параметры и предназначенных для совместного использования.

По технологии базового элемента, серии ИС можно разделить следующим образом:

МОП, ЭСЛ – ФЛС I типа,

ДТЛ, ТТЛ, И2Л – ФЛС II типа.

Каждая серия характеризуется такими электрическими и временными параметрами как: U0, U1, I0вх, I1вх, I0вых, Рпот, tз. ср.

В различных сериях существуют микросхемы одинакового функционального назначения, имеющие одинаковую схему, условное обозначение, конструкцию, схему подключения (цоколевку) и электрические характеристики. Совокупность таких микросхем называют функциональным рядом.

Функциональный ряд можно разбить на несколько групп по функциональному назначению: формирователи, генераторы, логические элементы, триггеры, счетчики, мультиплексоры, регистры, дешифраторы, микросхемы памяти и схемы вычислительных средств.

3.1. Построение логических элементов на транзисторных ключах

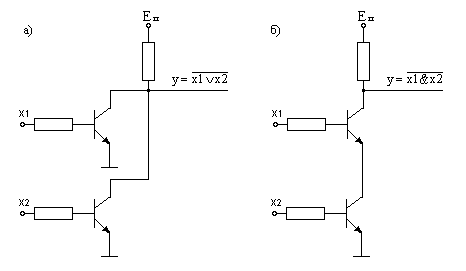

На рис. 3.1,а показана реализация логической функции 2ИЛИ-НЕ.

Если на один из входов Х1, Х2 подан уровень “1”, то один из транзисторов будет в насыщении (открыт), и на выходе будет уровень “0”.

Если на обоих входах будет уровень “0”, то, следовательно, транзисторы будут находиться в отсечке (закрыты), и на выходе будет обеспечен уровень “1”.

Рис 3.1. Реализация логических функций на транзисторных ключах

На рис. 3.1,б показана реализация логической функции 2 И-НЕ.

Если на один из входов Х1 или Х2 подан уровень “0”, или на оба входа Х1 и Х2 подан уровень “0”, то один или оба транзистора будут закрыты, и на выходе будет обеспечен уровень “1”.

Если на обоих входах Х1 и Х2 будет уровень “1”, то транзисторы будут открыты, и на выходе сформируется уровень “0”.

На таком принципе построения логических элементов основаны серии элементов МОП и ЭСЛ. Более детальное описание работы элементов этих серий приведено в справочниках и методических указаниях к лабораторным работам по изучению элементов соответствующих серий.

3.2. Построение логических элементов с использованием диодов

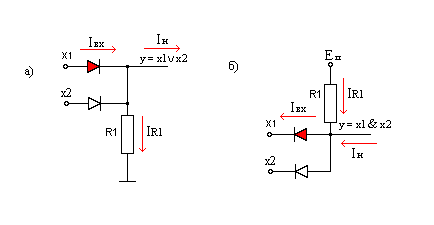

На рис. 3.2,а показана реализация логической функции 2ИЛИ на диодах.

Если хотя бы на одном из входов Х1, Х2 будет установлена “1”, то на выходе тоже будет“1”, так как один из диодов будет открыт и Uвых=U1вх-Uv. Если на обоих входах “0”, то и на выходе будет “0” Uвых=0 (диоды закрыты).

На рис. 3.2,б показана реализация логической функции 2И на диодах.

Если хотя бы на одном из входов Х1, Х2 будет “0” при Ux<ЕП, то на выходе тоже будет“0”, так как Uвых=U0вх+Uv. Если на обоих входах “1”, то и на выходе будет “1”, так как UХ1,Х2 ≈ ЕП.

Рис. 3.2 Реализация на диодах логических функций а) 2ИЛИ, б) 2И

На рис. 3.3,а показана реализация функции 2ИЛИ-НЕ.

Если хотя бы на одном из входов Х1, Х2 установлена “1” при Ux > ЕП, то на выходе будет “0”, так как ток через R1 или R2 будет течь в базу транзистора выходного каскада и введет его в насыщение.

Если на обоих входах “0”, то на выходе будет “1”, так как Ux < ЕП и ток через R1 и R2 потечет на вход, а не в базу транзистора.

На рис. 3.3,б показана реализация функции 2И-НЕ.

Если хотя бы на одном из входов Х1, Х2 уровень “0”, то на выходе будет “1”, так как Ux < ЕП и ток через R1 потечет на вход, а не в базу транзистора, и, следовательно, транзистор будет закрыт, а на его коллекторе будет уровень “1”. Если на обоих входах “1”, то на выходе будет “0”, так как UХ1,Х2≈ ЕП (I(Х1, Х2).≈ 0), ток через R1 будет течь в базу транзистора выходного каскада и введет его в насыщение.

Схемы, показанные на рисунке 3.3, являются примерами реализации логических функций на диодно-транзисторной логике (ДТЛ).

Рис. 3.3. Реализация на ДТЛ логической функции: а) 2ИЛИ-НЕ, б) 2И-НЕ.