- •Архитектура аппаратных средств.

- •1.2. Классификация элементов эвм.

- •1.3. Базовые логические элементы "и", "или", "не"

- •1.3.1. Элемент и

- •1.3.2. Элемент или

- •1.3.3. Элемент не

- •Исключительное или

- •Элемент и-не

- •Элемент или-не

- •Стрелка Пирса и штрих Шеффера. Стрелка Пирса

- •Штрих Шеффера

- •Архитектура фон Неймана.

- •Гарвардская архитектура.

- •Классическая гарвардская архитектура

- •Классифиация архитектур аппаратных средств.

- •Архитектура процессоров - cisc.

- •Архитектура процессоров - risc.

- •Сферы применения многоядерных процессоров

- •Основные классы многоядерных процессоров (many-core, multi-core, mimd, simd, smp, mmp)

- •Ячеистые" процессоры компании Tilera Процессоры Tile-64/64Pro

- •Семейство процессоров Tile-Gx

- •Процессор csx700

- •Краткие итоги

- •Архитектура процессоров seAforth

- •Структура графического процессора g80

- •Модель программирования cuda

- •Основные идеи архитектуры atac

- •Ключевые элементы технологии атас

- •Структура межъядерных связей

- •Передача данных и согласование кэш-памяти

- •Общая характеристика мультиядерных arm-процессоров

- •Серия Cortex-a mpCore

- •Состав, устройство и принцип действия основной памяти

- •Основная память

- •Статические элементы памяти

- •Программируемые зу

- •Сверхоперативная память

- •Ассоциативная память

- •Общие принципы функционирования кэш-памяти

- •Механизм сохранения информации в кэш-памяти

- •Типы кэш-памяти

- •Кэширование с обратной записью.

- •Организация внутренней кэш-памяти микропроцессора

- •Управление работой кэш-памяти на уровне страниц

- •Обеспечение согласованности кэш-памяти микропроцессоров в мультипроцессорных системах

- •Базовая система ввода-вывода (bios). Понятие cmos ram

- •Как bios управляет работой оборудования

- •Звуковые сигналы bios

- •Производитель ami

- •Производитель award

- •Системная, материнская плата

- •Цпу (Центральное процессорное устройство).

- •Архитектура графической подсистемы пк

- •Дисплеи

- •Дисплеи на элт

- •Жидкокристаллические дисплеи

- •Другие типы дисплеев

- •Принцип действия

- •Проекторы

- •Звуковая карта

- •Звуковые карты на шине pci.

- •Встроенный в системную плату ас’97_кодек.

- •Звуковые адаптеры и игры

- •Основные параметры и функции звуковых карт.

- •Блок питания.

- •Принтеры

- •Матричные принтеры

- •Струйные принтеры

- •Лазерные принтеры

Передача данных и согласование кэш-памяти

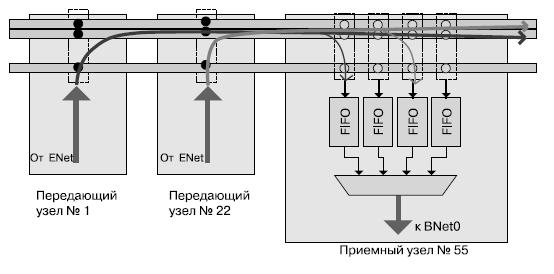

Более детально процесс передачи данных с применением сети ANet показан на рис. 7.6. Сообщения ядер достигают хаба, который, в свою очередь, пересылает их в сеть ONet на своей уникальной длине волны. Это позволяет двум хабам передавать данные одновременно без интерференции. ONet состоит из нескольких световодов: 64 для данных, 1 для управления и несколько для метаданных. Световоды метаданных служат для указания типа передаваемого сообщения (чтение памяти, данные и пр.) или как тэг сообщения (для устранения двусмысленности при нескольких сообщениях от одного источника). Хаб приемника принимает оба значения последовательно в FIFO-буфер, связанный с конкретным отправителем. Затем данные пересылаются вычислительным ядрам через BNet. Оптическая часть позволяет эффективно реализовывать широковещательную передачу с большей скоростью и меньшими затратами на регенерацию сигнала.

Рис. 7.6. Процесс передачи данных с использованием сети ANet

Ядра в АТАС — простые процессоры с кэшем данных и команд первого уровня. Когерентность кэшей поддерживается при помощи протокола, известного как ACKwise. Кэши поддерживают когерентность при помощи протокола распределенных директорий MOESI.

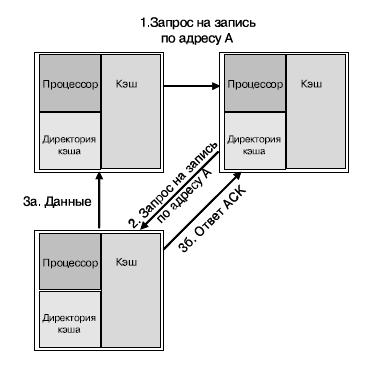

Директории распределены равномерно между ядрами, более того, каждое ядро является "домом" для определенного пула адресов (распределяется статически). Рис 7.7 представляет три ядра, находящиеся в различных кластерах. Каждое ядро содержит процессор, кэш данных и директории кэша. Для примера (рис. 7.7) предположим, что обращение к директории кэша всегда приводит к промаху (необходимости синхронизации кэша). Стрелками на рисунке обозначены типовые операции по согласованию кэшей: промах по записи по адресу А ядром а. В данном примере ядро б является "домом" адреса А, и начальное состояние адреса А в кэше — "занято" (O-state) ядром с. Трафик по согласованию кэшей передается по сети ANet. Последовательность действий для согласования кэшей для данного случая будет следующей:

Рис. 7.7. Пример согласования кэшей различных ядер

процессор в ядре а пытается осуществить запись по адресу А и получает ошибку записи;

ядро а посылает запрос на запись ядру б, к которому относится адрес А;

ядро б не имеет данных в кэше, но указывается, что этот адрес занят ядром с. Ядро б посылает запрос на запись по этому адресу от имени ядра а;

ядро с пересылает данные адреса А ядру а и обновляет состояние кэша для этого адреса до "недействительный";

ядро с посылает ACK-сигнал в директорию ядра б;

линия кэша, содержащая адрес А, обновляется на ядре а, и линия получает статус "модифицирована";

процессор ядра а производит запись по адресу А.

Когда ядрам необходимо обратиться к внешней памяти, они делают это при помощи нескольких встроенных в кристалл контроллеров памяти. Каждый контроллер памяти замещает кластер ядер и, таким образом, имеет свой выделенный оптический хаб. После получения запроса по оптической сети он обращается к внешним DRAM-модулям посредством стандартных линий ввода-вывода. Результаты передаются в оптическую сеть. Изменяя количество контроллеров памяти и количество кластеров, можно на различных АТАС-процессорах достигать различных значений показателей пропускной способности подсистемы памяти и вычислительной мощности. Основная задача контроллера памяти — преобразовать запросы от процессорных ядер в транзакции на шине памяти. Выбор технологии шины, таким образом, не зависит от архитектуры накристальной сети.

Вполне допустим вариант использования оптических интерфейсов как на ввод-вывод, так и для шины памяти. Это даст преимущество в пропускной способности и потребляемой мощности.

Каждый оптический вывод может поддерживать до 64 длин волн со скоростями до 20 ГГц. Скорость передачи данных будет ограничена скоростью работы электронных компонент, управляющих оптическим потоком. Предполагается, что скорость в 5 ГГц вполне может быть достигнута. При этом полоса пропускания оптического вывода может достигать 320 Гб/с (40 Гб/с). Для сравнения, 64-битная DDR3 имеет пиковую пропускную способность 12,8 Гб/с. Поскольку оптическая шина памяти состоит только из одного световода, уменьшается количество выводов, и это при увеличении пропускной способности практически в три раза. Все это де- лает применение оптического ввода-вывода востребованным для АТАС- процессоров с несколькими контроллерами памяти.