- •Вступление

- •1. Разработка проекта

- •1.1. Создание проекта

- •1.2. Создание логической схемы

- •1.3. Создание сложных схем

- •2. Компиляция проекта

- •2.1. Установка настроек компилятора

- •2.2. Создание назначений I/o логической схемы выводам плис

- •2.3. Компиляция проекта

- •3. Модуль симуляции

- •3.1. Создание Waveform файла для симуляции

- •3.2. Симуляция проекта

- •4. Модуль программирования

- •4.1. Программирование устройств Altera

- •5. Дополнительные сведения

- •5.1. Cправочная система Quartus II

- •5.2. Получение лицензии

- •6. Лабораторные работы

- •6.1. Изучение возможностей стенда и сапр Quartus II

- •6.2. Конфигурирование и программирование плис

- •6.3. Построение блоков управления на логических элементах

- •6.4. Использование блоков интеллектуальной собственности ip предоставляемых сапр Quartus II

- •Литература

- •Оглавление

2.2. Создание назначений I/o логической схемы выводам плис

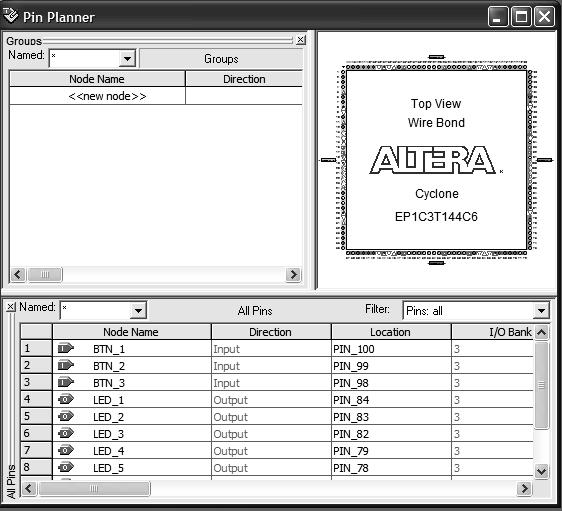

Используя Pin Planner можно просматривать и создавать назначения для всех ножек в проекте. После созданий назначений можно проверить их правильность командой I/O Assignment Analysis.

Сначала нужно создать БД проекта, выбрав в меню Processing пункт Start/Start Analysis & Synthesis. Компилятор проверит файл проекта на синтаксические и семантические ошибки и сгенерирует БД проекта.

В меню Assignments выбрать пункт Pins. Появится окно Pin Planner. В колонке Node Name можно увидеть уже установленные I/O логической схемы. В колонке Location указываются ножки ПЛИС.

Рис. 2.5. Окно распределителя контактов

После назначения выводов необходимо снова проверить проект, используя пункт Start Analysis & Synthesis меню Processing.

2.3. Компиляция проекта

Компилятор автоматически обнаруживает и использует файлы, такие как:

заголовочные файлы (*.inc), содержащие прототипы функций AHDL;

файлы инициализации памяти (*.mif) или файлы Hexadecimal Intel-format (.hex), включающие начальное содержание памяти;

файлы проекта Quartus II (*.qpf);

файлы с настройками Quartus II, содержащие информацию о проекте и настройках (*.qsf).

Компилятор генерирует информацию о предупреждениях и ошибках, которые появляются автоматически в окне сообщений.

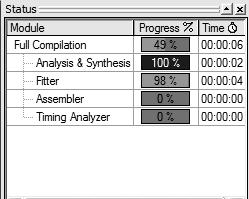

Для запуска процесса полной компиляции необходимо в меню Processing выбрать пункт Start Compilation. Компилятор немедленно начнет обработку проекта. В окне Status будет отображаться время, затрачиваемое на работу каждого модуля компиляции и его выполнение в процентах.

Рис. 2.6. Окно состояния

В течение компиляции все сообщения компилятора появляются во вкладке Processing окна Messages. Щелкнув два раза левой кнопкой мыши на сообщении можно увидеть источник ошибки или предупреждения.

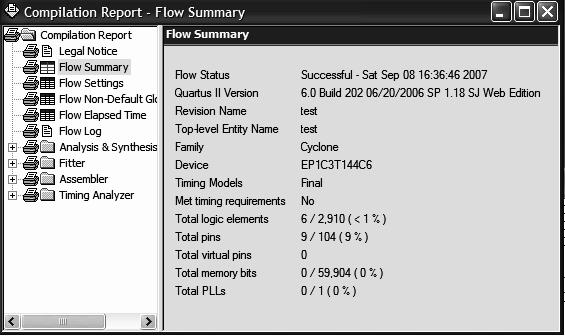

Отчет о компиляции появляется автоматически в окне Compilation Report. Он предоставляет детальную информацию о процессе компиляции.

Рис. 2.7. Окно отчета

3. Модуль симуляции

Симуляция позволяет проверить проект на работоспособность до программирования ПЛИС. В зависимости от информации, в которой нуждается разработчик можно выполнить функциональную либо временную симуляцию. Функциональная симуляция тестирует только логику работы проекта путем симуляции поведения списка цепей (Flattened netlist), полученных из файла проекта. Во временной симуляции используется полностью скомпилированный список цепей, содержащий информацию о таймингах, тестирующий логику работы с учетом временных задержек в устройстве.

Симулятор использует входные векторы для симуляции входных сигналов, которое программируемое устройство будет генерировать в тех же состояниях. Симулятор поддерживает следующие вектора входных сигналов:

Vector Waveform File (*.vwf);

Compressed Vector Waveform (*.cvwf);

Vector Table Output File (*.tbl);

Power Input File (*.pwf);

генерируемый Max+PLUS II векторный файл (*.vec);

Simulation Channel File (*.scf).

Альтернативным способом является ввод векторных сигналов в окне Tcl консоли. В типичном процессе симуляции создаются наборы входных векторов и проверяются результаты на выходах.