- •Вступление

- •1. Разработка проекта

- •1.1. Создание проекта

- •1.2. Создание логической схемы

- •1.3. Создание сложных схем

- •2. Компиляция проекта

- •2.1. Установка настроек компилятора

- •2.2. Создание назначений I/o логической схемы выводам плис

- •2.3. Компиляция проекта

- •3. Модуль симуляции

- •3.1. Создание Waveform файла для симуляции

- •3.2. Симуляция проекта

- •4. Модуль программирования

- •4.1. Программирование устройств Altera

- •5. Дополнительные сведения

- •5.1. Cправочная система Quartus II

- •5.2. Получение лицензии

- •6. Лабораторные работы

- •6.1. Изучение возможностей стенда и сапр Quartus II

- •6.2. Конфигурирование и программирование плис

- •6.3. Построение блоков управления на логических элементах

- •6.4. Использование блоков интеллектуальной собственности ip предоставляемых сапр Quartus II

- •Литература

- •Оглавление

2. Компиляция проекта

Компилятор Quartus II Compiler состоит из набора интегрированных модулей, которые проверяют схемы на наличие ошибок, синтезируют логику, приспосабливают проект под конкретные плис Altera, генерируют выходные файлы для симуляции, проводят анализ задержек и программирование устройства. Базовый компилятор состоит из модулей анализа и синтеза (Analysis & Synthesis), компоновщика (Fitter), ассемблера (Assembler) и анализатора задержек (Timing Analyzer). Эти модули можно запускать вместе или по отдельности через интерфейс пользователя. Альтернативным способом является запуск этих модулей независимо друг от друга, выполнив соответствующие команды в командной строке.

В течение процесса полной компиляции модуль анализа и синтеза сначала извлекает информацию, которая определяет иерархические связи между файлами проекта, и проверяет проект на основные ошибки. Затем он создает организационную карту проекта и совмещает все файлы проекта в базе данных для дальнейшей обработки. Следующим шагом компоновщик выбирает оптимальные пути межсоединений, соответствие пинов, и соответствие логических ячеек, необходимых для помещения в выбранную ПЛИС Altera. Ассемблер завершает обработку проекта путем преобразования ассоциаций сборщика в образ для программирования (прошивку) ПЛИС. Наконец, анализатор временных задержек запускается автоматически и генерирует отчет, содержащий информацию о задержках для логической схемы проекта. Также можно запускать другие модули компилятора, такие как генератор списка цепей (EDA Netlist Writer) и помощник проекта (Design Assistant) как части цикла полной компиляции, чтобы сгенерировать дополнительные файлы для отладки проекта.

Можно настроить различные методы компиляции, такие как компиляция по временным параметрам, для увеличения скорости работы логической схемы и оптимизации использования ресурсов ПЛИС. В течении компиляции можно просматривать результаты в окне Compilation Report.

В данном разделе пособия будут представлены настройки компилятора, а также будет показано, как создавать назначения входов и выходов схемы пинам устройства.

2.1. Установка настроек компилятора

Настройки компилятора позволяют определить семейство целевой ПЛИС, опции анализа и синтеза, настройки сборщика и другие опции. В раздел настроек можно попасть через меню Assignments, выбрав пункт Settings.

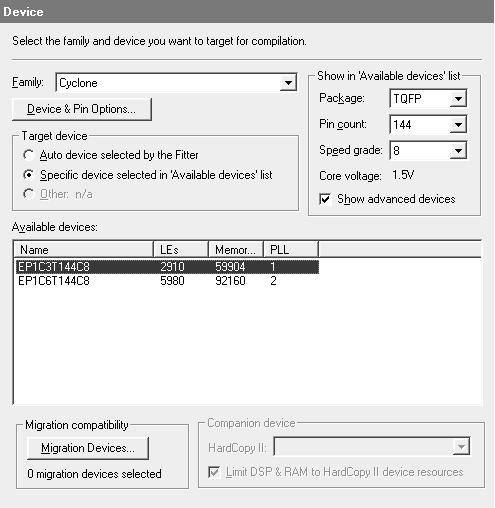

Для выбора целевой ПЛИС нужно сделать следующее:

В меню Assignments выбрать пункт Device.

В списке Family выберете семейство Cyclone.

В поле Target Device выберете пункт Specific device selected in ‘Available device’ list.

В поле Show in ‘Available devices’ list в списке типов корпусов Package выберете TFQP, в списке выбора количества пинов Pin count выберете 144, в списке класса быстродействия Speed Grade выберете 8;

В списке доступных устройств Available devices укажите EP1C3T144C8.

Рис. 2.1. Вкладка выбора ПЛИС

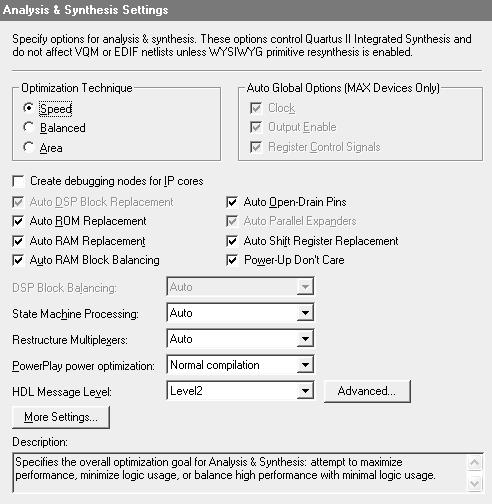

Настройки Анализа и Синтеза расположены на странице Analysis & Synthesis Settings диалога настроек, они позволяют оптимизировать работу модуля анализа и синтеза для обработки проекта. Для этого в списке Category диалога настроек выбрать пункт Analysis & Synthesis Settings. Появится страница настроек модуля анализа и синтеза;

В поле Optimization Technique выберете опцию Speed. Она указывает компилятору во время стадии анализа и синтеза распределять ресурсы ПЛИС для достижения максимальной производительности логической схемы внутри устройства;

Рис. 2.2. Вкладка настроек модуля анализа и синтеза

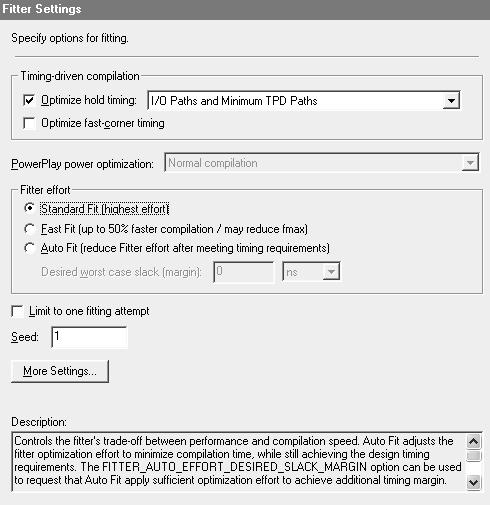

Вкладка настроек сборщика Fitter Settings позволяет определить опции, которые управляют сборкой проекта и скоростью компиляции. В закладке Physical Synthesis Optimization можно увеличить производительность проекта, используя физический синтез, который является интеграцией логического синтеза в процессах размещения и маршрутизации.

Для этого в диалоговом окне выберите категорию Fitter Setting. В поле Timing-driven compilation проверьте, чтобы опция Optimize hold timing была включена и выбран пункт I/O Paths and Minimum TPD Path. В поле Filter effort выберите пункт Standard Fit.

Рис. 2.3. Вкладка настроек компоновщика

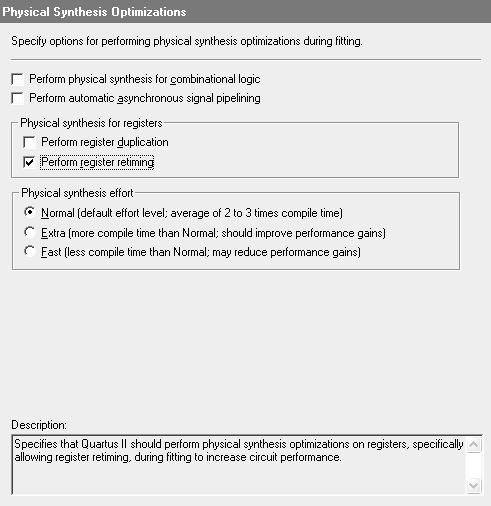

Далее в списке Category раскройте пункт Fitter Settings и выберете Physical Optimizations. В поле Physical synthesis for register включите опцию Perform register retiming. В поле Physical synthesis effort выберете опцию Extra.

После всех настроек нажмите OK, чтобы установки компилятора вступили в силу.

Рис. 2.4. Вкладка настроек модуля синтеза