- •1 Мета і задачі курсу "Цифрова схемотехніка"

- •1.1 Мета викладання курсу

- •1.2 Програма знань і умінь

- •2 Робоча програма дисципліни "Цифрова схемотехніка"

- •2.1 Лекційні заняття

- •2.2 Розділи програми, що пропонуються для самостійного вивчення

- •2.3 Лабораторні заняття

- •2.4 Практичні заняття

- •2.5 Курсове проектування

- •2.6 Рекомендована література

- •3 Характеристика підручників і навчальних посібників

- •4 Методичні вказівки з вивчення курсу "Цифрова схемотехніка"

- •5 Індивідуальні розрахункові завдання, контрольні завдання

- •6 Рекомендації з використання обчислювальної техніки

- •7 Рекомендації з організації самостійної роботи

- •8 Приклади розв’язання типових задач

Міністерство

освіти і науки України

Харківський

національний університет радіоелектроніки

Методичні вказівки

до самостійної

роботи

з дисципліни

"Цифрова схемотехніка"

для студентів

денної форми навчання

спеціальностей

ФБЕ, ЕПП, МНП

ЗАТВЕРДЖЕНО

Кафедрою БМЕ

Протокол № 6

від “ 11 ” 01 2004

р.

Харків 2004

Методичні

вказівки до самостійної роботи з

дисципліни "Цифрова схемотехніка"

для студентів денної форми навчання

спеціальностей ФБЕ, ЕПП, МНП / Упоряд.:

І.В. Прасол.

Харків: ХНУРЕ, 2004.

40 с.

Упорядники: І.В

Прасол.

Зміст

Вступ

1 Мета і задачі

курсу "Цифрова схемотехніка"

1.1 Мета викладання

курсу

1.2 Програма знань

і умінь

2 Робоча програма

дисципліни "Цифрова схемотехніка"

2.1 Лекційні

заняття

2.2

Розділи програми, що пропонуються

для самостійного вивчення

2.3 Лабораторні

заняття

2.4 Практичні

заняття

2.5 Курсове

проектування

2.6 Рекомендована

література

3

Характеристика підручників

і навчальних посібників

4 Методичні вказівки

з вивчення курсу "Цифрова схемотехніка"

5 Індивідуальні

розрахункові завдання, контрольні

завдання

6 Рекомендації з

використання обчислювальної техніки

7 Рекомендації з

організації самостійної роботи

8 Приклади

розв’язання

типових задач

ВСТУП

Дисципліна "Цифрова

схемотехника" відноситься до циклові

фундаментальних дисциплін, читається

на 4 курсі і є однієї з основних у

підготовці бакалаврів, фахівців і

магістрів по напрямку "Електроніка".

Вона базується на знанні електротехніки,

аналогової схемотехники, напівпровідникової

електроніки та електронних систем.

Навчальним планом передбачені лекції,

практичні заняття, лабораторні роботи

і курсове проектування. На лекціях

студенти одержують необхідні теоретичні

знання, необхідні для успішного

оволодівання дисципліною. У ході

практичних зайнять вивчаються прийоми

практичних розрахунків параметрів і

характеристик схем цифрової електроніки,

закріплюються отримані теоретичні

знання. На лабораторних роботах студенти

освоюють навички експериментальних

досліджень реальних цифрових схем з

використанням контрольно-вимірювальної

апаратури. Експериментально досліджуються

властивості логічних схем, визначаються

їхні основні параметри і характеристики.

У ході курсового проектування здобуваються

навички аналізу існуючих технічних

рішень, аналізу їх вад і недоліків,самостійного

проектування схем і пристроїв цифрової

електроніки, прийняття нових технічних

рішень.

Відвідування

практичних зайняти і лабораторних

робіт є обов'язковим для студентів.

Пропущені заняття підлягають

відпрацьовуванню. На практичні заняття

і лабораторні роботи студенти повинні

прийти підготовленими, вивчивши

відповідні теоретичекие розділи і

виконавши домашні завдання. Лабораторні

роботи починаються захистом звітів по

попередній роботі.

Особлива роль у

вивченні дисципліни приділяється

самостійній роботі. В умовах постійно

зростаючих обсягів інформації, високою

швидкістю її старіння, недостатністью

навчальної літератури саме інтенсивна

самостійна робота покликана підготувати

студентів до складних умов післяосвітньої

адаптації в умовах сучасного виробництва.

Тому метою даних методичних вказівок

є систематизація прийомів і методів

самостійній роботі студентів при

вивченні дисципліни "Цифрова

схемотехника".

Мета

дисципліни: вивчення принципів побудови

сучасних цифрових пристроїв та

напівполупроводникової пам’яті,

цифроаналогового та аналогоцифрового

перетворення, новітньої елементної

бази, основних типів комбінаційних та

послідовних пристроїв, методів

проектування та аналізу цифрових схем.

За результатом

вивчання дисципліни студенти повинні:

ЗНАТИ:

основи цифрової техніки; логічні

елементи різних технологій виготовлення;

комбінаційні пристрої; послідовні

пристрої; функціональні компоненти

цифрової схемотехніки; пристрої

пам”яті; нову елементну базу; перспективи

розвитку цифрової техніки;

- ВМІТИ:

аналізувати роботу пристроїв цифрової

схемотехніки; синтезувати логічні

схеми у базисах логічних елементів

різної технології; синтезувати

комбінаційні та послідовні пристрої;

проектувати генератори імпульсів, АЦП

і ЦАП; застосовувати новітню елементну

базу та програми аналізу електронних

схем.

№ теми

Назва розділу

або теми

Обсяг (год.)

1

2

3

1.

Вводна

лекція. Задачі та структура курсу.

Електронний ключ на біполярному

транзисторі. Статичні режими, перехідні

процеси

2

2.

Електронні

ключі на польових транзисторах.

Засоби підвищення бистродії ключів

2

3.

Логічні

змінні та функції. Числа та коди.

Бульова алгебра. Карти Карно. Базиси

логічних функцій

2

4.

Інтегральні

логічні елементи (ЛЕ)

4.1

Класифікація,

основні параметри та характеристики

ЛЕ. ТТЛ – елементи

2

4.2

Схемотехніка

ЛЕ на МДН - транзисторах. Основні МДН

серії інтегральних мікросхем

2

4.3

Емітерно

- зв’язана транзисторна логіка (ЕЗЛ).

Універсальний елемент, забезпечення

високої швидкості. ЕЗЛ мікросхеми

серії К1500. Інтегральна інжекційна

логіка (І2Л).

Схемотехніка інвертора та універсального

ЛЕ в базісі І2Л

2

5.

Комбінаційні

функціональні вузли.

5.1

Перетворювачі

кодів. Шифратори, дешифратори

2

5.2

Мультиплексори,

демультиплексори, алгебраїчні

суматори, цифрові компаратори

2

5.3.

Логічні матриці,

що програмуються.

Оптимальний

синтез комбінаційних

схем. Метод

Квайна

2

6.

Послідовні

функціональні вузли

6.1

Інтегральні

тригери. RS – тригери

2

6.2

D, T -

тригери. Універсальні JK – тригери

2

6.3

Лічильники.Класифікація.

Асинхронні та синхронні лічильники

(сумуючі та віднімаючі). Побудова

лічильників з заданим коефіцієнтом

лічби

2

1

2

3

7.

Елементи пам’яті

напівпроводникових

запам’ятаючих

пристроїв. Типи за- пам’ятовуючих

пристроїв та їх призначення

2

8.

Цифро – аналогові

перетворювачі

2

9.

Аналого –

цифрові перетворювачі

2

10.

Функціональні

компоненти цифрової схемотехніки.

Логічні розширювачі. Перетворювачі

рівнів. Генератори прямокутних

імпульсів

2

11.

Автоколивальні

мультивібратори. Очікуючі мультивібратори

2

12.

Регістри.Класифікація.Схемотехніка,

типові інтегральні мікросхеми

2

13.

Перспективи

розвитку цифрової схемо-техніки.

Сучасна елементна база

2

14.

Проектування

логічних схем за допомогою мови VHDL

2

№

Теми для

самостійного вивчення

Обсяг (год.)

1.

Елементи

пам’яті напівпроводникових

запам’ятаючих пристроїв. Типи

запам’ятовуючих пристроїв та їх

призначення

5

2.

Аналого-цифрові

пристрої

2

3.

Аналого-цифрові

перетворювачі

3

4.

Цифро-аналогові

перетворювачі

2

5.

Тригери та

мультивібратори на транзисторах

2

6.

Сучасні серії

цифрових мікросхем

2

7.

Функціональні

компоненти цифрової схемотехніки.

Логічні розширювачі. Перетворювачі

рівнів.

2

8.

Пристрої

програмованої логіки

6

№ теми

Теми занять

Обсяг, год.

1.

Дослідження

електронних ключів

4

2.

Дослідження

логічних елементів

4

3.

Дослідження

тригерів

4

4.

Дослідження

лічильників

4

5.

Дослідження

регістрів

4

6.

Дослідження

мультивібраторів

4

7.

Дослідження

Ц/А та А/Ц перетворювачів

4

8.

Дослідження

схем запам"ятовуючих пристроїв

4

№ теми

Теми занять

Обсяг, год

1.

Розрахунок

ключьових схем на транзисторах

2

2.

Логічні функції.

Базові логічні елементи

2

3.

Аналіз

та синтез комбінаційних логічних

схем

2

4.

Аналіз

та синтез логічних схем послідовного

типу

2

Метою

курсового проекту є практичне заглиблення

теоретичних знань з основних розділів

курсу, а також придбання навичок

самостійного розв’язання конкретних

завдань з розробки вузлів цифрових

систем за сучасним станом технології

їх виготовлення.

В результаті

виконання курсового проекту студент

повинен уміти:

-

здійснювати правильний вибір елементної

бази для побудови вузлів цифрових

систем;

- розробляти

принципові схеми цифрових систем;

- проектувати

генератори імпульсів, АЦП, ЦАП.

Курсовий

проект виконується в 7 семестрі денної

форми навчання. Плануємий обсяг - 20

годин.

Теми завдань на

курсове проектування:

Проектування

схеми базового логічного елемента

ТТЛ.

Проектування

схеми базового елемента ЕЗЛ.

Проектування

схем логічних елементів на основі

технології І 2Л.

Проектування

логічних схем на основі мультиплексорів

і демультиплексорів.

Проектування

схем перетворювачів кодів.

Побудова схем

клавіатурного введення.

Побудова схем

цифрової індикації.

Побудова схем на

основі логіки, що програмується.

Проектування

пристроїв керування на інтегральних

тригерах.

Проектування

схем лічильників імпульсів (двійкових,

двоїчно-десяткових, підсумовуючих, що

віднімають, реверсивних, зі змінним

коефіцієнтом ділення).

Проектування

схем дільників частоти.

Проектування

пристроїв на регістрах.

Проектування

схем запам'ятовуючих пристроїв.

Проектування

схем АЦП для введення аналогової

інформації в цифрову систему.

Проектування

схем ЦАП.

Проектування

схем генераторів прямокутних імпульсів.

Проектування

схем багатофазних генераторів.

Проектування

схем пультів дистанційного керування.

Розробка цифрових

схем пристроїв побутового призначення

(сигналізатор проникнення у квартиру,

несанкціонованого підключення до

телефонної лінії й ін.).

Проектування

цифрових пристроїв автомобільної

електроніки (автосторож, економайзер,

тахометр і ін.).

Проектування

схем медичних приладів індивідуального

користування (електронного термометра,

вимірника артеріального тиску й ін.).

Проектування

схем сільськогосподарського призначення

(цифрові вимірники температури й

вологості ґрунту й ін.).

2.6.1 Основна

література

1. Алексенко А.Г.

Микросхемотехника - М.: Сов. Радио, 1990.

- 496с.

2. Ерофеев Ю.Н.

Импульсные устройства. - М.: Высш. шк.,

1989. - 526с.

3.

Зубчук В.И. и др. Справочник по цифровой

схемотехнике.- Киев: Техніка, 1990. -446с.

4. Скаржепа В.А. и

др. Электроника и микросхемотехника.

- Киев: Техніка, 1989.

5. Новиков Ю.В.

Основы цифровой схемотехники. Базовые

элементы и схемы. Методы проектирования.

– М.: Мир, 2001.- 379 с.

6. Угрюмов Е.П.

Цифровая схемотехника. –СПб.:

БХВ-Петербург, 2001. – 528 с.

7. Партала О.Н.

Цифровая электроника. – СПб: Наука и

Техника, 2001. -224 с.

2.6.2. Додаткова

література

1. Зельдин Е.А.

Импульсные устройства на микросхемах.

- М.:Радио и связь,1991. - 160с.

2.

Гутников В.С. Интегральная электроника

в измерительных устройствах. - Л.:

Энергия, 1988. - 303с.

3. Бибило П.Н.

Синтез логических схем с использованием

языка VHDL. - М.: СОЛОН-Р, 2002.-384 с.

4.

Цифровые интегральные микросхемы:

Справочник / Богданович М.И., Грель И.Н.,

Дубина С.А. и др. – Мн.: Беларусь, Полымя,

1996. – 605 с.

2.6.3. Методичні

посібники та вказівки

1. Методические

указания к лабораторным работам по

импульсным устройствам. - Харьков,

ХТУРЭ, 1994. - 56с.

2.

Методические указания к лабораторным

работам по курсу "Цифровая схемотехника"

для студентов всех форм обучения

специальностей ФБЭ,ЭПУ/ Сост. Е.Г. Куник,

И.В. Прасол, Б.И. Борзенков. – Харьков:ХНУРЭ,

2001,-42с.

3. Методические

указания к практическим занятиям по

курсу “Основы схемотехники”. - Харьков,

ХТУРЭ, 1993. - 46с.

4. Методичні

вказівки до лабораторних робіт з курсу

"Цифрова схемотехніка" для студентів

денної та заочної форм навчання

спеціальностей ЕПП,ФБЕ/Упоряд. О.О.

Чистюхін, В.Н. Міськов:МОН України,

ХНУРЕ.-Х.:ХНУРЕ,2003.-49 с.

5. Методические

указания к практическим занятиям по

курсу "Цифровая схемотехника" для

студентов всех форм обучения специальностей

ФБЭ,ЭПУ,МПП/Сост. Прасол И.В. – Харьков,

ХНУРЭ, 2004, - 24 с.

6.

Методичні

вказівки до курсового

проектування та самостійної роботи з

дисципліни "Цифрова схемотехніка"

для студентів усіх форм навчання

спеціальностей ФБЕ, ЕПП, МНП / Упоряд.:

Прасол І.В.

Харків: ХНУРЕ, 2004.

50 с.

7.

Коспект лекцій з дисципліни “Цифрова

схемотехніка” для студентів спеціальностей

ФБЕ,ЕПП – електронний варіант, 2004 р.

Основні теоретичні

матеріали викладені в основній

літературі [1-7]. У ній наведені відомості

про принципи побудови цифрових схем,

їхніх основних властивостях, схеми

різних цифрових пристроїв, методах

проектування й аналізу. Слід зазначити

літературу [5,6]. Вона містить найбільш

систематизовані відомості про принципи

побудови сучасних цифрових пристроїв.

Джерело [7] може бути рекомендований

для стислого початкового ознайомлення

з дисципліною, для одержання повного

уявлення про вивчаємий предмет. Також

він може бути використаний як довідковий

посібник у ході завершальної підготовки

до іспиту.

Додаткова література

[1-4] дозволяє конкретизувати одержані

теоретичні знання, ознайомитися з

реальними конкретними схемами цифрових

пристроїв[1,2], проаналізувати основні

електричні параметри й характеристики

сучасної елементної бази [4]. В [3]

викладаються основи сучасної комп'ютерної

мови для проектування цифрових схем.

Цей матеріал призначений для найбільш

підготовлених студентів і дозволяє

формалізувати процес синтезу логічних

схем.

Методичні посібники

й вказівки [1-6] використаються на

практичних заняттях, лабораторних

роботах і в ході курсового проектування.

Їх студенти можуть одержати й в

електронному вигляді для індивідуального

використання.

Розділ "Електронні

ключі" найкраще вивчати по основній

літературі [2]. При цьому варто звернути

особливу увагу на умови, при яких

забезпечуються режими насичення й

відсічення ключа на біполярному

транзисторі. При аналізі перехідних

процесів необхідно розглянути

по-окремості стадії включення(затримка,

наростання переднього фронту й

нагромадження надлишкового заряду) і

вимикання(розсмоктування надлишкового

заряду, формування заднього фронту,

перезаряд бар'єрних ємностей). Варто

порівняти властивості й характеристики

ключів на польових і біполярних

транзисторах і вивчити способи підвищення

швидкодії(прискорювальний конденсатор,

нелінійний зворотний зв'язок, ненасичений

режим роботи транзисторів).

У розділі "Логічні

функції й змінні" необхідно вивчити

способи й форми представлення логічних

функцій, властивості елементарних

логічних функцій(склейка,поглинання,виявлення,

правило Моргана й ін.), перехід від

табличного представлення до аналітичного.

Особливу увагу варто приділити правилу

Моргана, використання якого дозволяє

переходити з одного логічного базису

в іншій(ТА-НІ, АБО-НІ,ТА-АБО-НІ). Варто

знати напам'ять таблиці переходів

елементарних функцій(ТА,ТА-НІ,АБО,АБО-НІ,НІ,

АБО що виключає ) і умовні графічні

позначення відповідних схемних

компонентів. При синтезі логічних схем

найчастіше використовуються методи

Квайна-Мак-Класки й карт Карно [3].

Комбінаційні

схеми(мультіплексори, шифратори,перетворювачі

кодів) доцільно вивчити по [3]. Перспективне

застосування логіки, що програмується

[5,6] - це дозволяє реалізовувати складні

пристрої на базових матрічних кристалах.

Послідовні

схеми(тригери, лічильники, регістри)

розглянуті в [3-6].

Розрахункові

завдання призначені для закріплення

теоретичного матеріалу, розвитку

навичок його практичного застосування,

контролю самостійної роботи студентів.

5.1 Індивідуальні

розрахункові завдання

Завдання

1. Реалізація перемикальної

функції (ПФ) від п'яти змінних. У таблиці

1 наведені варіанти, що описують

залежність вихідних значень функцій

від набору, що надійшов, до вхіду.

Таблиця

1 Варіанти значень функцій

№ вар.

Значення функції

на наборах

Базіс

Серія ІМС

1

0

1

0,2,4,8,10,16,23,25,30

1,3,5,7,9,11,24,29

АБО-НІ

К531

2

4,6,10,11,14,25,30

1,3,5,8,13,16,20,23,29

2MS"із8в1"

К561

3

1,5,8,12,20,25,27,30

0,3,6,7,14,16,19,22,24

ТА-НІ

К1533

4

0,3,6,10,15,21,24,28

1,4,7,9,11,17,20,26,31

Булев

К555

5

3,7,10,15,17,21,25,29

2,5,8,11,18,22,26,30

АБО-НІ

К561

6

2,6,10,16,19,25,30

3,9,12,13,17,20,21,23

2MS"із8в1"

К155

7

1,5,6,9,12,19,22,26,29

2,4,10,13,16,21,25

ТА-НІ

К531

8

0,4,10,13,18,21,26,30

1,5,9,11,15,20,24,28

Булев

К561

9

2,3,6,11,16,21,25,28

0,4,12,14,17,20,23,27

АБО-НІ

К1533

10

2,7,10,17,21,24,26,29

1,2,5,9,13,14,18,23,25

2MS"із8в1"

К555

11

2,4,6,12,15,19,23,27

4,8,10,11,14,25,30

ТА-НІ

К561

12

0,5,9,13,18,22,26,31

1,5,8,12,20,25,27,30

Булев

К155

13

2,4,6,8,10,18,24,28

0,3,7,11,15,21,25,27

АБО-НІ

К531

14

0,5,7,9,11,13,16,19,27

3,6,10,15,17,21,25,29

2MS"із8в1"

К561

15

2,5,7,10,12,15,19,28

4,6,11,16,21,25,30

ТА-НІ

К1533

16

3,4,8,15,20,24,27,30

1,5,6,9,12,19,22,26,29

Булев

К555

17

0,4,6,8,10,12,15,23,29

0,5,11,13,18,21,26,30

АБО-НІ

К561

18

0,1,5,9,12,15,17,22,26

2,3,6,11,16,21,25,28

2MS"із8в1"

К155

19

1,3,5,8,13,16,20,23,29

2,7,10,17,21,24,26,30

ТА-НІ

К531

20

0,3,6,7,14,16,19,22,24

2,4,8,10,11,20,23,27

Булев

К561

21

1,4,7,9,11,17,20,26,31

0,5,8,13,18,22,25,30

АБО-НІ

К1533

22

2,5,8,11,18,22,26,30

2,4,6,9,10,19,24,28

2MS"із8в1"

К555

23

3,9,12,13,17,20,21,23

5,7,10,11,14,16,19,27

ТА-НІ

К561

24

0,2,4,10,13,16,21,25

1,5,7,11,12,15,19,28

Булев

К155

25

1,5,9,11,15,20,24,28

3,4,6,18,22,25,27,30

АБО-НІ

К531

26

3,4,5,12,14,17,20,23,27

0,1,6,8,10,13,15,25,29

2MS"із8в1"

К561

27

1,4,5,11,15,21,25,29

3,7,8,13,17,20,23,27

ТА-НІ

К1533

28

0,2,7,10,20,25,29,31

3,6,14,15,22,24,26,30

Булев

К555

29

1,5,8,12,16,21,26,29

0,3,7,11,15,19,23,25,

АБО-НІ

К561

30

0,1,5,11,15,18,22,30

1,2,5,7,10,14,18,24,25

2MS"із8в1"

К155

31

1,3,5,11,15,21,25,29

2,4,6,8,10,14,20,27,28

ТА-НІ

К531

32

0,2,7,10,20,25,28,31

3,5,6,12,13,15,19,29

Булев

К561

33

0,1,4,10,15,19,21,28

2,4,7,9,12,16,20,25,30

ТА-НІ

К1533

34

0,1,3,9,13,15,21,23,28

2,5,6,8,11,14,19,25,31

2MS"із8в1"

К555

35

0,2,4,7,8,15,18,22,25

3,9,12,14,17,19,24,28

АБО-НІ

К561

На наборах, не

зазначених у таблиці, функція може

приймати будь-яке значення.

Визначити

максимальний час затримки розповсюдження

сигналу від моменту подачі набору

вхідних змінних до появи відповідного

логічного рівня на виході.

Завдання

2. Використовуючи ІМС

зазначеної у варіанті серії, розробити

схему 8-розрядного синхронного лічильника.

№ варианту

Тип ІМС

4

К555ИЕ10

6

К531ИЕ18

8

К555ИЕ6

10

К555ИЕ9

13

К555ИЕ7

15

К561ИЕ14

17

К531ИЕ17

29

К531ИЕ16

34

К561ИЕ11

Побудувати часову

діаграму роботи лічильника для випадку,

коли на його синхровхід надходить 40

синхроімпульсів

Варіант 19,22.

З'єднати послідовно 2 зазначені ІМС,

побудувати часову діаграму роботи

отриманої схеми для 25 вхідних

синхроімпульсів.

Варіант 19. К561ИЕ9.

Варіант 22. К561ИЕ8.

Побудувати схему

8-розрядного двунаправленого регістра

пам'яті, використовуючи ІМС заданої

серії:

№ варианту

Серія ІМС

5

К531

7

К555

9

К561

11

К1561

12

К1533

16

К1554

20

К155

Використовуючи

ІМС мультиплексорів і логічних елементів,

побудувати схему комбінаційного

пристроя зсуву. Величина зсуву

визначається вхідним кодом. Зсув

виконувати без втрат розрядів. Вхідне

слово - 4-х розрядне.

№ варианту

Серія ІМС

Макс. величина

зсуву

Напрям зсуву

2

К1533

4

ст

14

К561

3

ст,мл

18

К555

3

мл

21

К155

3

ст,мл

23

К155

4

мл

25

К555

4

ст

27

К1533

3

мл

30

К155

4

ст

33

К1533

4

мл

35

К561

3

ст

Примітка: мл - зсув

убік молодших розрядів, ст - убік старших.

Використовуючи

ІМС К155ИЕ8 побудувати схему дільника

частоти.

Варіант

28. КДЛ=69

Варіант

32. КДЛ=6.

Побудувати тимчасову діаграму роботи

для двох циклів.

Розробити схему

дешифратора шкального типу (16 виходів).

Кількість включених світлодіодів

(починаючи з молодшого) відповідає

двійковому коду, що надійшов на вхід

дешифратора. Виходи підключаються до

світлодіодам (Iном=5 мА). Використати

ІМС наступних серій:

Варіант 24. К555.

Варіант 26. К155.

Варіант 31. К561.

Варіант

1. Побудувати схему перетворювача

імпульсної послідовності.

Він повинен сформувати

на своїх виходах імпульсні послідовності,

зрушені на 90, 180 і 270 градусів стосовно

вхідної імпульсної послідовності.

Варіант 3.

Використовуючи ІМС К561ИР9, побудувати

реверсивний регістр зсуву.

5.2 Контрольні

завдання

5.2.1 Електронні

ключі:

1. Наведіть умови,

що забезпечують режими насичення і

відсічення транзистора в схемі ключа.

2. Які фактори

визначають швидкодію транзисторного

ключа?

3. Які відомі

способи підвищення швидкодії

транзисторного ключа?

4. Як впливає

підключення навантаження на характеристики

транзисторного ключа?

5. Як зміниться

швидкодія ключа, якщо напруга джерела

живлення зменшиться в два рази?

6. Чим відрізняються

транзисторні ключі на p–n–p, n–p–n і

польових транзисторах?

5.2.2 Логічні

функції:

1.

Наведіть основні властивості логічних

функцій.

2. Як перейти від

табличної форми представлення логічної

функції до аналітичного (СДНФ, СКНФ)?

3. Порівняйте

методи мінімізації логічних функцій.

4. Як реалізувати

логічну функцію ЧИ на елементах І-НІ?

Як реалізувати логічну функцію І на

елементах ЧИ-НІ?

5.2.3 Логічні

елементи:

1. Якими статичними

і динамічними параметрами характеризуються

інтегральні ЛЕ?

2.

Назвіть особливості схем сучасних

базових елементів ТТЛ, ЕЗЛ, І2Л

и на польових транзисторах?

3.

Порівняєте мікросхеми серій ТТЛ, ЕЗЛ,

І2Л

и на польових транзисторах між собою.

4. Які міри приймають

для підвищення навантажувальної

здатності, швидкодії і зменшення

споживаної потужності ЛЕ?

5. Елемент ТТЛ

може реалізувати логічну функцію

одновхідного інвертора двома способами:

об'єднанням логічних входів і підключенням

до усіх входів, крім одного, рівня "1".

Який з режимів кращий і чому?

5.2.4 Комбінаційні

логічні пристрої:

1. На скількох

прямих виходах чотирьохрозрядного

дешифратора може бути сигнал: а) рівня

"0"?; б) рівня "1"?

2. Скільки входів

повинне бути у дешифратора з 16 виходами,

щоб він був: а) повним? б) неповним?

3. Порівняєте між

собою три основні структури дешифраторів:

матричну (лінійну), каскадну і пірамідальну.

4. Який код

установиться на виході шифратора з

пріоритетом, якщо активні рівні надійшли

одночасно на три входи?

5. Скільки виходів

повинен мати восьмівхідний шифратор

для перетворення десяткових чисел у

двоічний код?

6. У яких випадках,

яким образом будують пірамідальну

(деревоподібну) схему мультіплексора

чи демультіплексора? Які недоліки

пірамідальних структур?

7. Які особливості

мультіплексорів на КМОН-схемах?

8. Як за допомогою

мультіплексора реалізувати логічну

функцію? Наведіть приклади.

9. Чим відрізняються

перетворювачі кодів з ваговим і неваговим

перетворенням? Де найчастіше

використовуються перетворювачі з

ваговим перетворенням?

10. Де використовується

перетворювач двоічного коду в код

семісегментного індикатора? Скільки

у нього входів? Наведіть приклад.

5.2.5 Послідовні

цифрові пристрої:

1. Приведіть умовні

графічні позначення основних різновидів

тригерів в інтегральному виконанні,

їх таблиці переключень і поясніть

призначення входів.

2. Приведіть схеми

основних різновидів тригерів на ЛЕ.

3. У чому розходження

між синхронними тригерами, керованими

рівнем тактуючого сигналу, і синхронними

тригерами з внутрішньою затримкою? У

яких випадках використовуються зазначені

типи тригерів?

4. Як побудувати

Т-триггер на основі RS-, D-, JK -тригера?

5. Які зміни

необхідно внести в схему тригера з

внутрішньою затримкою, щоб змінити

фронт тактуючого сигналу, по якому

здійснюється переключення тригера?

6. Як побудувати

підсумовуючий, віднімаючий і реверсивний

лічильники на JK-тригерах?

7. Як побудувати

лічильник c довільним коефіцієнтом

перерахування?

8. Які типи тригерів

можуть бути використані в регістрах і

чому?

9. Назвіть основні

параметри й характеристики регістрів.

10. Охарактеризуйте

основні види регістрів(зберігання, із

зсувом вправо й уліво, реверсивні).

11. Приведіть схеми

регістрів зберігання й зсуву. Які

принципи їхньої побудови?

12. Зобразіть умовні

графічні позначення мікросхем регістрів.

13. Приведіть

приклади сучасних інтегральних схем

регістрів, які виконани по різних

технологіях (ТТЛ, ЕЗЛ, на польових

транзисторах), їхні електричні параметри

й характеристики.

14. Наведіть приклади

пристроїв, які будуються на регістрах.

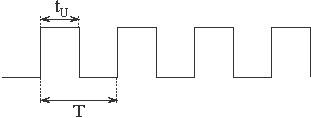

5.2.6 Генератори

прямокутних імпульсів:

З якою метою в

схемах мультивібраторів і одновібраторів

включають діоди?

Якими елементами

схеми мультивібратора визначається

максимальна й мінімальна частота

проходження вхідних імпульсів?

У чому складається

особливість побудови схем мультивібраторів

з RC - зворотними зв'язками на елементах

АБО-НІ?

Порівняйте між

собою характеристики мультивібратора

з автоматичним зсувом і без нього.

Назвіть переваги

мультивібраторів із двупетлевим

зворотнім зв"язком.

Чим відрізняється

стабільність роботи схем одновібраторів

на елементах ТТЛ?

Приведіть і

поясніть розрахункові співвідношення

для тривалості імпульсів у схемах

одновібраторів на інтегральних

мікросхемах ТТЛ.

Яким способом

можна домогтися підвищення стабільності

вихідного імпульсу одновібратора?

Намалюйте схему

мультивібратора на елементах АБО-НІ

і її часові діаграми. Яким способом

можна усунути замикання мультивібратора

на елементах ТТЛ?

Проектування

електричної схеми обов'язково повинне

завершуватися її моделюванням на ЕОМ.

У ході цього етапу проектування

перевіряється правильність функціонування

запропонованого варіанта схеми,

розраховуються її основні вторинні

параметри й характеристики, у ряді

випадків проводиться багатокритеріальна

параметрична оптимізація. У випадку

цифрових схем виявляються перегони й

змагання сигналів, розраховуються

відповідні часи затримок. Для цього

необхідно використати сучасні системи

автоматизованого проектування.

У цей час відома

велика кількість програм і систем

проектування електронних схем, серед

яких найбільш відомими є:

- Мicro-Cap - розробка

фірми Spectrum Software для розрахунку електричних

характеристик схем. Недавно вийшла

версія 6.0, яка має бібліотеку більше 10

тис. электрорадіоелементів ведучих

фірм Японії, Європи й США;

- Design Lab - інтегрований

пакет корпорації MicroSim, до складу якого

входить відома програма моделювання

Pspice. Він дозволяє проводити наскрізне

проектування радіоелектронних пристроїв:

від введення принципової схеми і її

моделювання до створення керуючих

файлів для програматорів, розробки

друкованих плат і керуючих програм для

свердлильних верстатів і виводу даних

на графобудівник;

- P-CAD - пакет

логічного аналізу й конструкторського

проектування на платформі DOS, що став

фактично стандартом на промислових

підприємствах;

- ACCEL EDA - пакет

P-CAD на платформі Windows. Версії 15.1 привласнене

найменування P-CAD 2000, що випливає версія

зветься P-CAD 2001;

- Electronics WorkBench -

розробка фірми Interactive Image Technologies для

моделювання електричних процесів у

схемах;

- OrCAD - розробка

однойменної фірми.

З вищенаведених

програм виділяються програма Electronics

WorkBench( завдяки наявності

контрольно-вимірювальних приборів-мультиметр,

осцилограф і ін.- по зовнішньому вигляді,

органам керування й характеристикам

максимально наближених до реальних,

легкості в освоєнні й зручності

використання) і система наскрізного

проектування OrCAD, що дозволяє практично

реалізовувати всі проектні процедури

від алгоритмічного опису схеми до

випуску конструкторської документації

й програм для автоматів, що випускають

електронні схеми.

6.1 Застосування

системи OrCAD

Комплекс

OrCAD вирішує повний цикл завдань

проектування електронного устаткування:

створення схеми пристрою; створення

опису схеми мовою VHDL; синтез блоків на

FPGA і CPLD;

аналогове, цифрове й змішане

моделювання; проектування друкованої

плати. До його составу

входять наступні програми:

OrCAD Capture - графічний

редактор схем;

OrCAD Exprres - синтез

і аналіз логічних ІС і ПЛІС;

OrCAD Pspice - моделювання

аналогових і змішаних аналого-цифрових

пристроїв;

OrCAD Pspice Optimizer-

програма параметричної оптимізації;

OrCAD Layout- розробка

друкованих плат і ряд інших.

Програма OrCAD

Capture призначена для створення проекту,

частина якого може бути задана у вигляді

принципової електричної схеми, а інша

частина може бути описана мовою високого

рівня VHDL . Крім того, з оболонки OrCAD

Capture запускається модуль OrCAD Express для

синтезу й моделювання ПЛІС, а також

програми моделювання аналогових,

цифрових і змішаних аналого-цифрових

пристроїв PSpice і параметричної оптимізації

PSpice Optimizer.

При

створенні проекту кожного типу

завантажуються відповідні бібліотеки

компонентів. При створенні принципових

схем проекту необхідна інформація

відшукується в убудованій базі даних,

що поставляється разом із системою й

поповнюється користувачами. Компоненти

зберігаються у відповідних бібліотеках

(які мають розширення .olb

):

- Analog - дискретні

аналогові компоненти (резистори,

ємності, індуктивності й ін.);

- Source - джерела

аналогових і цифрових сигналів, параметри

яких задаються в текстовому вигляді;

-Sourcestm.olb - такі ж

джерела, але їхні параметри задаються

за допомогою редактора сигналів Stimulus

Editor;

- Bipolar.olb - біполярні

транзистори;

- CD400.olb - КМОН

логічні елементи;

- Dig(ecl.olb - ЕСЛ

логічні елементи;

- 7400.olb - ТТЛ логічні

елементи;

- Siemens.olb -

напівпровідникові прилади фірми

Siemens;

- Angdev.olb - операційні

підсилювачі й інші ІС фірми Analog Devices.

Створення проекту

електричної схеми провадиться в програмі

OrCAD Capture. У неї завжди відображаються

два вікна - менеджер проекту й інформаційне

вікно "Session Log". У менеджері проекту

відображається структура проекту у

вигляді файлів. Файлова структура

проекту містить ряд розділів: Design

Resource - опис проекту (файл проекту *.dsn,

файли окремих сторінок схеми, перелік

компонентів Design Cache, VHDL-файли, перелік

використовуваних бібліотек компонентів

*.olb); Outputs - результати проектування;

PSpice Resource - інформація для моделювання

за допомогою PSpice (Include Files, Model Library,

Simulation Profiles, Stimulus Files) і ін.

У програмі OrCAD

Capture можливо створювати чотири типи

проектів:

Analog or Mixed-Signal

Cicrcuit- аналогові або змішані аналого-цифрові

пристрої, які моделюються за допомогою

програми PSpice(можлива подальша розробка

друкованої плати за допомогою OrCAD

Layout);

PC Board- друковані

плати з можливістю електричного

моделювання;

Prоgrammabel Logic-пристрої

програмувальної логіки CPLD або FPGA;

Schematic- тільки

створення й документування принципової

схеми.

Програма аналогового

моделювання PSpice підтримує наступні

типи аналізу:

Bias Point- розрахунок

по постійному струму;

DC Sweep-варіювання

параметрами компонентів у режимі

розрахунку по постійному струму;

Time

Domain(Transient)-часовий аналіз(розрахунок

перехідного процесів);

AC Sweep/Noise-частотний

аналіз;

Monte Carlo/Worst

Case-статичний аналіз по методу Монте

Карло або найгіршого випадку.

Моделювання

електронної схеми виконується по

команді з головного меню "Run PSPice".

Після цього запускається програма

моделювання PSPice. По закінченні її роботи

необхідно в програмі Capture виділити

досліджувані величини струму або

напруги. Це виконується по команді

"PSPice / Markers/ Voltage Level" або "PSPice /

Markers / Carrent into pin". Можливо також

відображати сигнали в програмі Pspice по

команді " Trace\ Add Trace". Для дослідження

отриманих графіків виберіть курсор по

команді "Trace\ Cursor\Display" і вказівником

миші виміряйте необхідні параметри.

Після моделювання

необхідно проаналізувати отримані

результати моделювання й, якщо необхідно,

зробити повторне моделювання схеми з

іншими параметрами або виконати інший

вид аналізу.

6.2 Застосування

програми Electronics Workbench

Програма Electronics

Workbench (залежно від версії) дозволяє

виконати розрахунок схеми по постійному

струму (DC Operating Point), розрахунок частотних

характеристик (AC Frequency), розрахунок

перехідних процесів (Transient), Фур'є-аналіз

(Fourier), аналіз спектра внутрішніх шумів

(Noise), аналіз нелінійних і інтермодуляційних

перекручувань (Distortion), багатоваріантний

аналіз (Parameter sweep), температурні

випробування схеми (Temperature sweep), розрахунок

відносної чутливості характеристик

схеми до змінам параметрів обраного

компонента (Sensitivity), розрахунок на

найгірший випадок (Worst Case) і статистичний

аналіз по методу Монте-Карло (Monte Carlo).

Вікно програми

EWB 5.0 містить головне меню, панелі

інструментів і бібліотек компонентів

і контрольно-вимірювальних приладів,

а також робоче поле (простір). Робочий

простір являє собою саму більшу

центральну область вікна EWB. Воно є

подобою макетної плати, на якій збирається

й налагоджує схема.

Складання

схеми здійснюється приміщенням елементів

з активної бібліотеки елементів у

робочу

область екрана, з'єднанням цих елементів

і, при необхідності, підключенням

вимірювальних приладів.

Для

розміщення елемента на робочому полі

необхідно активізувати відповідну

бібліотеку компонентів(Basic, Transistors,

Analog Ics, Digital Ics і т.д), вибрати необхідний

елемент і, затиснувши ліву клавішу

миші, "перетягнути" його на поле.

З'єднання елементів

схеми між собою провадиться аналогічно

перетаскуванню елементів у робочий

простір. Щоб скористатися вимірювальним

приладом, необхідно вибрати відповідний

прилад.

Для здійснення

аналізу схеми з головного меню варто

вибрати пункт Analysis, задати вид аналізу

і його параметри й натиснути кнопку

0-1, яка розташована в правому верхньому

куті екрана.

Отримані результати

необхідно проаналізувати, зробити

виводи і якщо буде потреба внести

корективи в схему. Потім моделювання

повторити з новим варіантом схеми.

Загалом

процес навчання

умовно поділяється на чотири основних

етапи: 1) ознайомлювальний; 2) первинне

засвоєння матеріалу; 3) накопичення

інформації; 4) аналітичне осмислення і

систематизація знань.

На

першому етапі, який реалізовується на

лекціях, здійснюється первинне

ознайомлення з предметом вивчення,

обсягом і змістом необхідних знань,

загальними фізичними процесами,

складаються перші уявлення про

систематизацію знань.

Другий

етап

це самостійне, індивідуальне опрацювання

основних підручників

і конспекту

лекцій, спрямоване на отримання

необхідних теоретичних знань. Самостійна

робота

найпродуктивніша, якщо

студент спілкується з викладачем під

час консультацій, щоб з'ясувати і

уточнити основні положення навчального

матеріалу.

Третій

етап

реалізовується на лабораторних і

практичних заняттях, в процесі підготовки,

виконання, захисту завдань та звітів,

розв’язання контрольних задач. На

цьому етапі загальні

теоретичні знання застосовують до

конкретних явищ і пристроїв,

поглиблюють

в процесі аналізу експериментальних

і розрахункових результатів. Тут корисне

спілкування студентів між собою,

проведення взаємних консультацій,

дискусій, взаємної перевірки знань.

Завершальний

етап

аналітичне осмислення, аналіз і

систематизація знань, набуття професійних

навичок,

ознайомлення зі

спеціальною літературою, рекомендованою

викладачем або вибраною відповідно до

індивідуальних інтересів, самоконтроль

знань в процесі підготовки відповідей

на контрольні запитання

і завдання, виконання індивідуальних

розрахункових завдань, курсових робіт

і проектів.

Така

багатоступенева структура засвоєння

сприяє отриманню глибоких і довготривалих

знань, виробляє творче, аналітичне

мислення.

Задача

1. У схемі електронного ключа на

біполярному транзисторі (рис. 8.1,а) ЕК

= 10В, ECM

= 3 В, Rl

=10 кОм, R2

= 15 кОм, RK

= 2 кОм. Визначите, у якому режимі буде

працювати транзистор, якщо UBX

= +5 В; 3 В; –1 В. Вважати h21Е

= 20, IKO

0, Uбен

0.

Рисунок 8.1

Рішення.

Припустимо, транзистор відкритий і

насичений. Тоді еквівалентна схема

вхідного ланцюга ключа має вид,

представлений на рис.8.1,б. Зважаючи на

те, що транзистор ідеальний, Uбен

= 0. На підставі першого закону Кирхгофа

IБ =

I1 -

I2,

Виразимо струми через параметри

елементів схеми:

Тоді

IБ =

UBX/R1–ECM/R2.

Величина

струму бази насичення Iбн

= Iкн/h21Е

Для

насичення транзистора необхідно, щоб

Iб

Iбн.

При заданих вхідних напругах:

1) Iб

= 5/10–3/15 = 0,3 мА, тpaнзистор відкритий і

насичений;

2) Iб

= 3/10-3/15 = 0,1 мА, транзистор відкритий, але

працює в активному режимі;

3) Iб=

–1/10-3/15 = –0,3 мА.

В

останньому випадку величина базового

струму виявилася негативною. Це значить,

що прийняте допущення невірне і

транзистор знаходиться в режимі

відсічення. Еквівалентна схема вхідного

ланцюга ключа в цьому випадку зображена

на рис.8.1,в, a Iб

= IК0.

Зневажаючи

величиною IК0

зі співвідношення

знайдемо

значення Uбе:

Воно відповідає

умові відсічення транзистора.

Задача

2. Визначите тривалість переднього,

заднього фронтів і розсмоктування при

переключеннях транзисторного ключа

(див. рис. 8.1,а) прямокутними імпульсами

напруги, що змінювалися від значення

ЕГ2 =

-2 В до ЕГ1

= 1 В (ланцюг зсуву ЕСМ,

R2 відсутня).

Вихідні дані для розрахунку: EK

= 10 B, R1

= RK

=1 кОм. Вважати h21Е

= 40,

Рішення.

Тривалості фронтів і розсмоктування

визначимо по формулах:

де

Підставляючи

вихідні дані одержимо: Iбн

= 0,25ма, Iб1

= 1ма, Iб2 =

2ма,

= 160 нс,

= 200 нс, t+порівн

58 нс, t-ф

24 нс, tрас

23 нс.

Задача

3. Визначите тривалості включення і

вимикання ключа на МДП–транзисторе з

резистивним навантаженням при Ес

= 15 В, Rс

= 1 кОм, і сумарною паразитною ємністю

Се =

18 пф. Прийняти S = 6мА/В2,

U0 =

3В, Ез.вкл =

15 В.

Рішення.

Час включення

Час

вимикання tBКЛ

= 2,2RССЕ

= 2,210001810–12

= 40 нс.

Задача 4. Запишіть

у виді таблиці істинності й в аналітичній

формі логічну функцію від трьох

перемінних по наступному словесному

описі: функція дорівнює одиниці, якщо

дві з вхідних перемінних дорівнюють

одиниці.

Рішення.

Таблиця істинності має вид:

Х1

0

1

0

0

1

0

1

1

X2

0

0

1

0

1

1

0

1

X3

0

0

0

1

0

1

1

1

Y

0

0

0

0

1

1

1

0

Логічна функція

в СДНФ:

Y=X1X2

Логічна функція

в СКНФ:

Y=(X1+X2+X3)(

+X2+X3)(X1+

+X3)(X1+X2+

)(

+

+

Задача 5. Мінімізуйте

логічну функцію чотирьох перемінних

Y(X1, X2, X3, X4) = 1110111001000100. Такий запис функції

означає, що вона задається рядком її

значень, записаних у порядку зростання

двоічних номерів комбінацій незалежних

перемінних, тобто при X1=0, X2=0. Х3=0, X4=0 Y=1;

при X1=1, X2=0. Х3=0, X4=0 Y=1; при X1=0, X2=1. Х3=0, X4=0

Y=1; при X1=1, X2=1. Х3=0, X4=0 Y=0 і т.д.

Рішення.

Нанесемо цю функцію на карту Карно:

Поєднуючи

клітки, що містять "1", у дві

прямокутні області розміром 22=4,

одержуємо мінімальне вираження функції

в ДНФ:

Y=

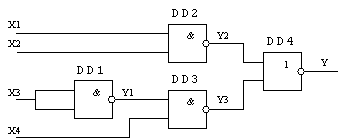

Задача 6. Яку

логічну функцію виконує схема, зображена

не рис. 8.2? Як зміниться ця функція, якщо

елемент ДДЗ вийде з ладу (на його виході

з'явиться низький потенціал, що відповідає

рівню "0")?

Рисунок 8.2

Рішення.

Запишемо вихідні сигнали логічних

елементів:

Y1=

; Y2=

Застосовуючи

правило де Моргана, одержуємо:

Y=Х1Х2X3X4.

При

виході елемента ДДЗ із ладу, схема буде

виконувати наступну логічну функцію:

Y=

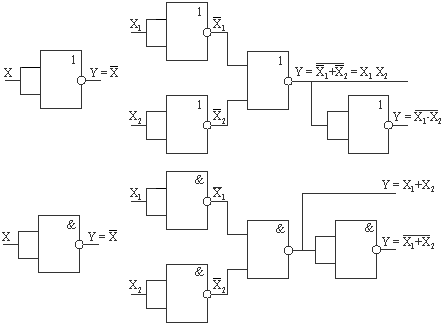

Задача 7. На

елементах І-НІ побудувати схеми, що

реалізують функції НЕ, ЧИ, ЧИ-НІ. На

елементах ЧИ-НІ побудувати схеми, що

реалізують функції НЕ, І, І-НІ. Укажіть

на недоліки отриманих схем.

Рішення.

Умовні графічні

позначення елементів І-НІ і ЧИ-НІ і

таблиця істинності приведена на рис.

8.3.

Рисунок 8.3

Використовуючи

властивість інверсії і правило Моргана,

запишемо:

Тоді схеми, що

реалізують задані функції, мають вид,

представлений на рис. 8.4.

Рисунок 8.4

Недоліки таких

схем:

за рахунок

об'єднання входів елементів збільшується

їхня вхідна ємність, вхідні струми і

споживана потужність;

за рахунок

збільшення кількості елементів

збільшується споживана схемою

потужність, збільшується час затримки;

збільшуються

габарити пристрою, його вага, ціна,

ускладнюється трасування міжз’єднань,

знижується перешкодозахищеність і

надійність.

Задача

8. Визначите рівні вихідної напруги

двохвхідной ТТЛ-схеми зі складним

інвертором (рис. 8.5) для випадків: а)UВХ1

= UВХ2

= ЕК

; б) UВХ1

= 0,2 В, UВХ2

= ЕК;

в) UВХ1

= UВХ2

= 0,2 В. Вважати, що напруги на прямосмещенных

переходах відкритих транзисторів Uбен

= Uбки

рівні 0,7 В, напруга колектор-эміттер

насиченого транзистора Uкен

дорівнює 0,2 В, напруга на прямозміщеном

діоді дорівнює 0,7 В, гранична напруга

відмикання транзистора дорівнює 0,6 В,

ЕК = 5 В, h21Е

= 10, h21ЕІ

= 0,025, R1

= 4 кому, R2

= 1,6 кОм, а навантаженням є аналогічна

ТТЛ-схема.

Рисунок 8.5

Рішення.

У режимі логічної одиниці на входах

транзистор VT1 знаходиться в активному

інверсному режимі (еміттерні переходи

зміщені в зворотному, а колекторний –

у прямому напрямку), транзистора VT2, VT4

– відкриті і насичені, а транзистор

VT3. замкнений. VТ3 замкнений, тому що

напруга на його базі Uбз

= Uкен2

+ Uбен 4

= 0,2+0,7 = 0,9 В, на еміттері UЕ3

= Uкен4

+ UVD1

= 0,2+0,7 = 0,9 В, у той час як поріг відмикання

UПОР. 3

= Uбз

– Uез =

0,6 B. Тому Uвих

= Uкен4

= 0,2 В.

При

подачі рівня логічного "0" хоча б

на один вхід VT1 входить у режим насичення,

транзистори VТ2, VT4 закриваються, а

транзистор VT3 переходить в активний

режим. Отже, Uвих

= Ек

– UR2

– Uбез

– UVD1

, де UR2

= IбзR2

= Iе3R2/(h21е

+ 1) – спадання напруги на резисторі R2

від протікання базового струму

транзистора VT3. Тому що схема навантажена

аналогічним ТТЛ-елементом, то величина

струму IЕ3

дорівнює еміттерному току вхідного

многоеміттерного транзистора VT1

навантаження: IЕ3

= IН

= IR1Hh21еI,

де = IR1H

– струм через резистор R1

навантажувального ТТЛ-елемента; h21еI

– інверсний коефіцієнт підсилення по

струму.

Струм

IR1

дорівнює:

Тоді

IЕЗ

= 0,018 мА, UR2

= 2,6 мВ, а UВИХ

= 3,6 В.

Задача

9. Визначите рівні вихідної напруги

схеми ЕСЛ-елемента з заземленою мінусовою

шиною (рис. 8.6) при UBX1

= U1

, UBX2

= U0.

Вважати, що напруги база-еміттер і

колектор-еміттер відкритого транзистора

Uбео

= 0,7 В, Uкео

= 0,6 В, a U0

= 3,5 В, U1

= 4,З В, U0

= (U1

+ U0)/2

= 3,9 В, Еп

= 5B.

Рисунок 8.6

Рішення.

Тому що еміттери транзисторів VT1 – VT3

зв'язані між собою, то відкривається

той транзистор, потенціал бази якого

вище. У розглянутому випадку це транзистор

VT1(Uб1

= Uвх1

= 4,3 В, Uб2

= 3,5 В, Uб3

= 3,9 В). У результаті протікання еміттерного

струму відкритого транзистора через

резистор R5

на ньому створюється спадання напруги

UR5 =

U1 –

Uбео=4,3-0,7=3,6

В. Тому що для транзистора VT3 Uбез

= U0

– UR5

= 3,9 – 3,6 = 0,3 В, то він закривається.

Зневажаючи величинами струмів IK3

і Iб5,

можна вважати, що Uкз

Eп=

5В. Тому Uвих2

Eп – Uбе5

= 5 – 0,7 = 4,3 В, що відповідає рівню логічної

одиниці.

З огляду

на спадання напруги на проміжку

колектор-еміттер відкритого транзистора

VT1 одержуємо: Uк1

= UR5

+ Uкео

= 3,6 + 0,6 = 4,2 В.

Тоді

Uвих1

= Uк1

– Uбео

= 4,2 – 0,7 = 3,5 В, що відповідає рівню

логічного нуля.

Таким чином, на

виході 2 реалізується логічна ЧИ функція,

на виході 1 – ЧИ-НІ.

Задача

10. Оціните швидкодію ЛЕ ЧИ-НІ на

МДП-транзисторах з динамічним

навантаженням (рис. 8.7), Вихідні дані

для розрахунку: ЕП

= 15 В, напруга відсічення U0

= 3 В, питома крутість характеристик

активного і навантажувального

транзисторів вА

= вН

= 0,5 мА/В2,

СЕКВ

= 20 пф.

Рисунок 8.7

Рішення.

Швидкодія ЛЕ визначається його часом

включення і вимикання. Нехай у вихідному

стані UВИХ

= EП.

Після подачі сигналу рівня, що відмикає,

"1" на один з активних транзисторів

його струм стоку досягає значення IC

= вA/2[(EП

– U0)

– U0]2.

Ємність

CЕКВ

починає розряджатися цим струмом, UВИХ

зменшується. Після переходу активного

транзистора з положистої області в

круту починає зменшуватися і IC.

Будемо вважати, що IС

= CONST, тоді

Підставляючи

вихідні дані, одержуємо tВКЛ

= 21520/0,5/(15–6)2

15 нс.

При

надходженні замикаючого сигналу рівня

логічного нуля (U0 =

0) струм IC

зменшується до нуля. Активний транзистор

запирається, а ємність СЕКВ

заряджається від ЕП

через навантажувальний транзистор

VT3. Час вимикання

tВИКЛ

= 2,2ВИКЛ=2,2

де

1/(E–U0)вH

– опір каналу навантажувального

транзистора.

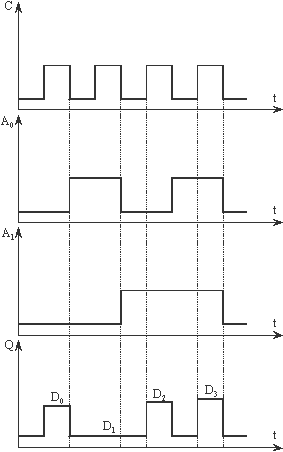

Задача

11. Побудувати синхронний чотирьохвхідний

мультіплексор із прямим і інверсних

виходом на основі логічних елементів.

Визначити максимально припустиму

затримку сигналу по адресних входах,

якщо частота стробіруючого сигналу 1

МГц. Як застосувати отриманий мультіплексор

для перетворення рівнобіжного двоічного

коду в послідовний? Намалюйте відповідні

тимчасові діаграми. За допомогою

мультіплексора реалізуйте логічну

функцію f(X1, X2) = X1

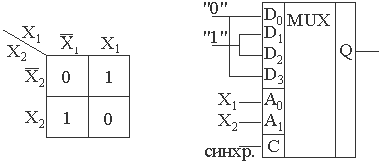

Рішення.

Для комутації вхідних сигналів

використовуємо елементи І DD1-DD4, об'єднані

ланцюгом синхронізації С. Коли на С

поступає рівень логічної 1, всі елементи

І відкриваються і можуть комутирувати

вхідні сигнали. Блокування всіх

елементів, крім одного, здійснюється

сигналами на адресних ланцюгах А0

і А1

відповідно до таблиці:

А1

А0

Q

0

0

1 1

0

1

0 1

Д0

Д1

Д2 Д3

Інвертори DD5, DD6

формують інверсії адресних сигналів.

Вибір одного з 4

можливих сигналів відбувається елементом

DD7 ЧИ. Інверсія вихідного сигналу

здійснюється інвертором DD8.

Розглянемо

роботу схеми. Нехай при С=1 А0

= А1

= 1. На всіх керуючих входах DD4 виявляється

рівень “1” і вхідний сигнал D3

вільно проходить через DD4 і DD7 на вихід.

При цьому на виходах DD1, DD2 і DD3 підтримується

рівень “0”, обумовлений наявністю

рівня “0” інверсій

Рисунок 8.8

При

частоті стробіруючого сигналу f=1 МГц

і шпаруватості

Рисунок 8.9

За цей

час сигнал адреси повинен установитися

на входах елементів І. Затримка адресного

сигналу відбувається в інверторах DD5,

DD6. Тому tзад.инв.<

0,5 мкс.

Рівнобіжний

чотирьохрозрядний код, подаваний

одночасно всіма розрядами на входи

D0-D3,

може бути перетворений у послідовний

код за допомогою відповідних адресних

сигналів за 4 такти синхросигнала. За

умови, що на вході D0=1,

D1=0,

D2=D3=1

і передача починається з молодшого

розряду (D0),

послідовність сигналів буде мати вид,

представлений на рис. 8.10.

Слід зазначити,

що зміна сигналів адреси повинна

відбуватися під час відсутності

дозволяючого синхросигнала, щоб

виключити помилкове спрацьовування

елементів.

Рисунок 8.10

Представимо

необхідну логічну функцію у виді карти

Карно:

Рисунок 8.11

Функція

приймає одиничне значення на наборах

Х1=1,

Х2=0

і Х1=0,

Х2=1.

Подамо

сигнали Х1

і Х2

на адресні входи мультіплексора. Тому

що комбінація адресних сигналів А0=0,

А1=1

– до комутації входу D2,

то на ці входи варто подати рівні

логічної одиниці, а на інші – рівні

логічного нуля. Схема представлена на

рис. 8.11.

Задача 12. На рис.

8.12,а приведена умовна позначка мікросхеми

дешифратора 4х16 типи К155ИДЗ. Поясните

призначення входів мікросхеми. Як на

її основі побудувати дешифратор 5х32?

Рішення.

Мікросхема має 4 входи D0...D3,

два інверсних дозволяючих входи V0,

V1 і

16 інверсних виходів, пронумерованих

від 0 до 15. Дешифратор є повним, тому що

при числі розрядів n = 4 число виходів m

= 16 (m = 2n).

Якщо на обох входах, що дозволяють,

підтримується рівень "0", мікросхема

працює як дешифратор. Рівень "1",

поданий на кожній із дозволяючих входів,

приводить до появи рівня "1" на

усіх виходах незалежно від стану входів.

Рисунок 8.12

Щоб

одержати дешифратор 5х32, необхідно

сигнал старшого розряду подати на

дозволяючий вхід першого дешифратора,

і через інвертор - на дозволяючий вхід

другої мікросхеми. Однойменні входи

дешифраторів варто об'єднати. Тоді

доти, поки в старшому розряді зберігається

рівень "0", працює перший дешифратор.

З появою в старшому розряді рівня "1"

блокується вже перший дешифратор, а

дешифрацію вхідного сигналу здійснює

другий дешифратор, Для керування роботою

5-розрядного дешифратора дозволяючи

входи V1

поєднуються. Схема побудованого

дешифратора приведена на рис.8.12,б.

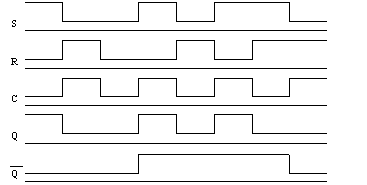

Задача 13. Намалюйте

часові діаграми вихідного сигналу

RS-тригера з прямими входами, якщо: а)

тригер асинхронний; б) тригер синхронний.

Часові діаграми вхідних сигналів

приведені на рис. 8.13,а. Инерціоністю

RS-тригера зневажити. Вихідний стан

тригера – нульовий.

Рішення.

Для побудови часових діаграм вихідного

сигналу скористаємося таблицею

переключення RS-тригера з прямими

входами. Необхідно відзначити, що на

7-м такті вхідних сигналів надходить

заборонена комбінація R=S=1.

Рисунок 8.13

Протягом

цього часу Q =

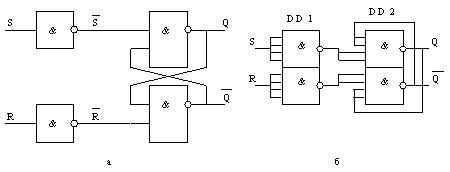

Задача 14. Реалізуйте

асинхронний RS-тригер із прямими входами

на мікросхемах К155ЛА1 (двох чотирьохвхідних

елемента І-HІ в одному корпусі), складіть

структурну схему і визначите необхідне

число корпусів мікросхем і максимальну

робочу частоту, якщо середній час

затримки одного ЛЕ 50 нс.

Рішення.

Робота асинхронного RS-тригера з прямими

входами описується наступним логічним

вираженням: Q = SV

Таким

чином, необхідно мати інверсії вхідних

сигналів

,

S і за допомогою двох двохвхідних

елементів І-НІ реалізувати функції

Щоб побудувати

тригер необхідно два корпуси мікросхеми

К155ЛА1. Для одержання інверторів вхідних

сигналів входи двох елементів І-НІ

варто об'єднати. Схема тригера на

мікросхемі К155ЛА1 приведена на рис.

8.14,б.

Тому

що елементи ДД1 спрацьовують одночасно,

а елементи ДД2 при переключенні –

послідовно, то загальний час затримки

переключення tзад

= 3tзадЛЕ

= 150 нс. Тоді максимальна частота вхідного

сигналу fmax

= 1/tзад

6,7 МГц.

Задача 15. Побудуйте

синхронний чотирьохрозрядний двоічный

підсумовуючий лічильник з послідовним

переносом на мікросхемах серії K531.

Визначите стан його виходів після

надходження на вхід 45 імпульсів. Вихідний

стан лічильника – нульовий. Знайдіть

максимальну частоту рахунка.

Рисунок 8.14

Рішення.

Використовуємо для побудови лічильника

мікросхему К531ТВ9П і К531ЛИ1П. Це два

JК-триггера в одному корпусі з додатковими

входами установки логічних 0 і 1 і чотири

двохвхідних елементи І в одному корпусі

відповідно. Тому що лічильник

чтирьохрозрядний, то необхідно

використовувати два корпуси мікросхеми

К531ТВ9П і один корпус К531ЛИ1П. Схема

лічильника має вид, представлений на

рис. 8.15.

Коефіцієнт

перерахування такого лічильника 24

= 16, тобто кожен 16-й імпульс установлює

всі розряди в нульовий стан. Тому після

надходження 45 імпульсів на виходах

лічильника встановлюються логічні

рівні, що відповідають двоічному коду

числа 13 (45–2 16–13), тобто а0

= 1, а1

= 0, а2

= 1, а3

= 1.

Сигнал

переносу в схемі формується послідовно,

тому максимальна величина затримки

сигналу tзад.т =

(n–2)tзад.ЛЕ,

де n – число розрядів лічильника.

Підставляючи значення tзад.ЛЕ

= 7,5 нс, одержуємо tзад.т

= 15 нс. Тоді максимальна

частота рахунка fmax

67 МГц.

Рисунок 8.15

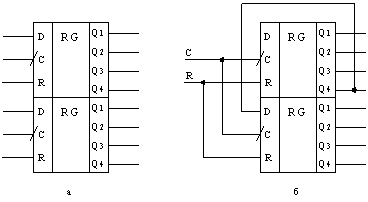

Задача 16. На рис.

8.16,а приведене умовне зображення

мікросхеми 564ИР2. Які основні операції

може виконувати ця схема і яке призначення

входів і виходів? Як потрібно з'єднати

входи і виходи мікросхеми при нарощуванні

розрядності регістра? Скільки корпусів

мікросхем 564ИР2 необхідно для збереження

двоічного числа 1001101110?

Рисунок 8.16

Рішення.

Це здвоєний чотирьохрозрядний статичний

регістр зрушення на КМОП-структурах з

послідовним введенням і рівнобіжним

висновком інформації. Керування

здійснюється переднім фронтом тактуючого

імпульсу (при переході з 0 у 1). Вхід D –

інформаційний, С – тактовий, R – скидання

регістра в нуль. При нарощуванні

розрядності регістра входи і виходи

з'єднуються так, як показано на рис.

8.16,б.

Для збереження

10-розрядного числа необхідно два корпуси

мікросхем (один повний і 1/4 другого).

1 Мета і задачі курсу "Цифрова схемотехніка"

1.1 Мета викладання курсу

1.2 Програма знань і умінь

2 Робоча програма дисципліни "Цифрова схемотехніка"

2.1 Лекційні заняття

2.2 Розділи програми, що пропонуються для самостійного вивчення

2.3 Лабораторні заняття

2.4 Практичні заняття

2.5 Курсове проектування

2.6 Рекомендована література

3 Характеристика підручників і навчальних посібників

4 Методичні вказівки з вивчення курсу "Цифрова схемотехніка"

5 Індивідуальні розрахункові завдання, контрольні завдання

6 Рекомендації з використання обчислювальної техніки

7 Рекомендації з організації самостійної роботи

8 Приклади розв’язання типових задач

![]() ,

,

![]() .

.![]() = 10/(220)

= 0,25 мА.

= 10/(220)

= 0,25 мА.![]() ,

, .

.![]() =

1 Мгц. СКЕ

= 40 пф.

=

1 Мгц. СКЕ

= 40 пф.![]() ,

,![]() ,

,![]() ,

,![]() .

.![]() ,

де

,

де

![]() = 6(15–3)/2

= 36 мА. Тоді tBKЛ =

1,51518/36

=11,25нс.

= 6(15–3)/2

= 36 мА. Тоді tBKЛ =

1,51518/36

=11,25нс.

![]() V

V

![]() X2X3

V X1

X2X3

V X1![]() X3.

X3.![]() ).

).

![]() V X1

.

V X1

.

![]() ; Y3=

; Y3=![]() =

=![]() ; Y=

; Y=![]() =

=

![]() =X1X2.

=X1X2.

![]() ;

;![]() .

.

![]() 0,725 мА

0,725 мА

![]()

![]() ,

,![]() +

+![]() X2.

X2.

![]() і

і

![]() на одному з керуючих входів. При А0

= А1

= 0, рівень “0” є присутнім на входах

DD2-DD4. І тільки на трьох керуючих входах

DD1 є присутнім рівень”1”, забезпечуючи

проходження сигналу D0

на вхід. І т.д. Умовне графічне позначення

такого мультіплексора приведене на

рис. 8.8.

на одному з керуючих входів. При А0

= А1

= 0, рівень “0” є присутнім на входах

DD2-DD4. І тільки на трьох керуючих входах

DD1 є присутнім рівень”1”, забезпечуючи

проходження сигналу D0

на вхід. І т.д. Умовне графічне позначення

такого мультіплексора приведене на

рис. 8.8.

![]() (див. рис. 8.9), тривалість сигналу, що

дозволяє,

(див. рис. 8.9), тривалість сигналу, що

дозволяє,

![]() с

= 0,5 мкс.

с

= 0,5 мкс.

![]() = 0. Тому що на 8-м такті сигнал на S-вході

приймає значення 0, то відбувається

зміна рівня тільки на інверсному заході.

У випадку синхронного тригера зміна

стану тригера можлива тільки при С = 1.

При надходженні заданої комбінації С

= 0, тому тригер на неї не реагує. Тимчасові

діаграми асинхронного і синхронного

тригерів приведені на рис. 8.13,б і 8.13,в,

відповідно.

= 0. Тому що на 8-м такті сигнал на S-вході

приймає значення 0, то відбувається

зміна рівня тільки на інверсному заході.

У випадку синхронного тригера зміна

стану тригера можлива тільки при С = 1.

При надходженні заданої комбінації С

= 0, тому тригер на неї не реагує. Тимчасові

діаграми асинхронного і синхронного

тригерів приведені на рис. 8.13,б і 8.13,в,

відповідно.![]() Q0,

де Q0 –

поточний стан тригера. Скориставшись

правилом де Моргана і властивістю

інверсії, перетворимо його до виду:

Q0,

де Q0 –

поточний стан тригера. Скориставшись

правилом де Моргана і властивістю

інверсії, перетворимо його до виду:![]() .

.![]() і

і

![]() .

Структурна схема такого тригера

приведена на рис. 8.14,а.

.

Структурна схема такого тригера

приведена на рис. 8.14,а.

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

17

32

18

31

19

30

20

29

21

28

22

27

23

26

24

25