- •СведенИя о процессоре pic16. Система команд Архитектура процессоров семейства pic16

- •Распределение областей памяти процессоров pic16

- •Система команд процессоров pic16

- •Программирование на Ассемблере

- •Синтаксис числовых значений в различных системах счисления

- •Практическая часть Процесс подготовки программ для процессоров pic16 Методические указания

- •Ход работы

- •Лабораторная работа № 1

- •Теоретические сведения

- •Ход работы

- •Лабораторная работа № 2.

- •Теоретические сведения

- •Ход работы

- •Лабораторная работа № 3.

- •Теоретические сведения

- •Ход работы

- •Лабораторная работа № 4

- •Теоретические сведения

- •Ход работы

- •Лабораторная работа № 5

- •Теоретические сведения

- •Ход работы

- •Лабораторная работа № 6

- •Теоретические сведения

- •Ход работы

- •Лабораторная работа № 7

- •Теоретические сведения

- •Ход работы

- •Лабораторная работа № 8

- •Теоретические сведения

- •Ход работы

- •Список литературы

Лабораторная работа № 7

Тема работы: «Организация подпрограмм и табличных функций»

Теоретические сведения

Если функция представлена таблицей данных уі (хі) либо может быть выражена так, что конечному числу аргументов соответствует конечное количество значений функции и если конечное значение функции достаточно сложное, то целесообразно организовать такую функцию в виде подпрограммы-таблицы. Ключевым способом адресации в этом случае является индексная, при которой номер аргумента і определяет выбор строки в таблице.

Головная программа передает в w номер аргумента х, начиная с нуля, и вызывает подпрограмму – таблицу. Подпрограмма возвращает значение функции в w.

Пример. Организовать вычисление функции у = х2 + 1, где х = 0…3.

Функцию вычисления возложим на компилятор ассемблера. Х вводится вручную (считаем, что его формирует какая-то предыдущая часть программы)

LIST p=17f77

INCLUDE p16f77.inc

CBLOCK 0x20

c_x

c_y

ENDC

m_loop MOVF c_x, w

CALL s_tab

MOVWF c_y

goto m_loop

s_tab ADDWF PCL, f ; ключевая команда подпрограммы-таблицы

; с индексной адресацией

RETLW 0*0+1

RETLW 1*1+1

RETLW 2*2+1

RETLW 3*3+1

NOP

END

При этом необходимо предусмотреть следующие ограничения:

Индексная адресация процессоров PIC16 работает в пределах одного сегмента, поэтому количество строк в таблице на должно превышать 256;

Команда RETLW возвращает однобайтовое число, поэтому значение функции должно находиться в диапазоне от 0 до 256;

Подпрограмма табличной функции должна находиться в пределах одного сегмента, и для ее вызова номер сегмента предварительно должен быть размещен в регистре PCLATH.

Ход работы

Составить программу заполнения массива X из AA однобайтовых чисел результатами вычисления выражения

у = BB * x(i)2 + CC,

организованного в виде подпрограммы вычисления табличной функции (AА, BВ, СС – номера первых трех букв фамилии);

Рассчитать ожидаемые результаты.

Выполнить компиляцию и проверку работы программы. Сопоставить результаты с ожидаемыми и сделать соответствующие выводы.

Оформить протокол работы, включающий в себя исходные численные данные, а также таблицу с текстом программы с собственными данными и численные значения переменных после выполнения программы.

Контрольные вопросы.

Принцип организации подпрограмм.

Как реализуется индексная адресация с участием стека.

Как реализуется индексная адресация с участием PCL.

Какая команда процессоров PIC16 обеспечивает организацию табличных функций.

Лабораторная работа № 8

Тема работы: «Управление периферийными устройствами».

Теоретические сведения

В состав процессоров PIC-16 включают до 5 параллельных портов PORTA…PORTE с общим количеством выводов до 33:

PORTA – 6 выводов;

PORTВ…PORTD – 8 выводов;

PORTЕ – 3 вывода.

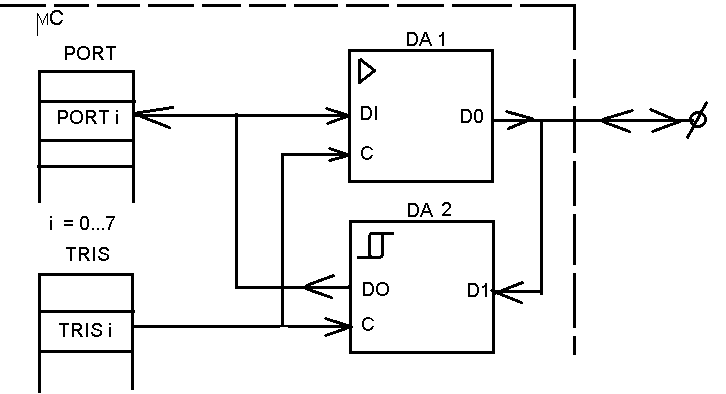

Каждый вывод порта является двунаправленным, т.е. может принимать или передавать логические сигналы. Структура информационного канала выглядит следующим образом:

В состав информационного канала входит одноименный разряд однобайтового регистра PORT , операционный усилитель DA1 и триггер Шмитта DA2. DA1 предназначен для согласования уровней и увеличения мощности выходного сигнала, DA2 - для согласования уровней и устранения помех входного сигнала. DA1 и DA2 могут иметь три состояния выходов:

- «0» и «1» - активные уровни;

- высокоомное z – состояние, эквивалентное разрыву электрической цепи.

Активный или пассивный режим работы усилителей определяется управляющим сигналом С, подаваемым на них от управляющего регистра TRIS.

![]() - режим вывода

- режим вывода

![]() - режим ввода

- режим ввода

Канал управления параллельного порта включает один регистр TRIS.

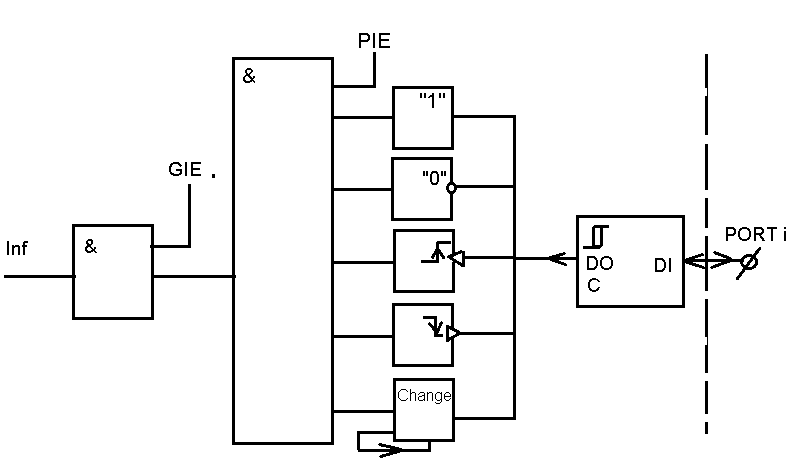

Канал прерывания параллельного порта может реагировать на определенные состояния, переходы или изменения уровней сигнала PORTi. Обычно в модуль прерывания подается сигнал после DА2.

Режим реагирования на прерывание определяется в специальном регистре прерывания порта.

Управление прерыванием порта PIECOM. В этом регистре присутствует бит PIE=1, разрешающий прерывание от этого порта. Прерыванием управляет также сигнал GIE, разрешающий прерывание системы в целом.

Пример. Составить программу инициализации для PORTD, у которого разряды 0…5 работают в режиме вывода, а 6 и 7 – в режиме ввода.

BSF STATUS, RP0 ; активизация первой страницы Page 1

CLR TRISB ; все выводы порта В в режиме вывода

BSF TRISB, 6 ; 6 в режиме ввода

BSF TRISB, 7 ; 7 в режиме ввода

BCF STATUS, RP0 ; активизация нулевой страницы Page 0

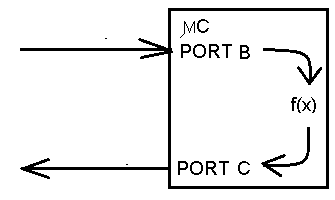

Пример. Составить программу инициализации для передачи данных из разрядов 0 и 1 PORTВ в разряды 3 и 4 PORTС и запретить прерывание PORTВ.

PORTВ 0 и 1 – режим вывода

PORTС 3 и 4 – режим ввода

При разработке такой программы необходимо учесть, что служебные регистры TRIS находятся в первой странице памяти, а рабочие в нулевой.

-

Бит регистра STATUS

Page

PR1

PR0

0

0

0

0

1

1

1

0

2

1

1

3

BSF STATUS, RP0 ;активизация первой страницы памяти Page 1

CLR TRIS B ; все разряды порта В в режиме вывода, в том числе 0 и 1

BSF TRISС, 3 ; 3 и 4 разряды порта С

BSF TRISС, 4 ; в режиме ввода

BCF STATUS, RP0 ; активизация нулевой страницы Page 0

BCF INTCOM, RBIE; запрет прерываний порта В (указание на этот флажок содержится в документации на служебные регистры PIC16