- •Створення і дослідження мультиплексорів, претворення паралельного коду в послідовний

- •Створення і дослідження шифраторів (позиційного кодув двійковий, двійковий в десятковий) на основі логічних елементів

- •Створення і дослідження дешифраторів (двійкового коду, двійководесяткового в позиційний) на основі логічних елементів

- •Визначення кількості інформації, оцінка інформаційних втрат та швидкості передачі для дискретних інформаційних каналів

- •Побудова кодів, які виявляють помилки для заданого ансамблю повідомлень телемеханічних систем

- •Побудова кодів, які виявляють і виправляють помилки для заданого ансамблю повідомлень телемеханічних систем

- •Кодування циклічних кодів методами ділення інформаційних символів на утворюючий багаточлен та визначення провірочних символів під час проведення лінійни операцій

- •Декодування циклічних кодів з використанням схем ділення першого і другого типу

Ващишак С.П., Мельничук С.І.,

Романів В.М.

Телемеханіка і передача інформації в нафто-газовій промисловості

ЛАБОРАТОРНИЙ ПРАКТИКУМ

МІНІСТЕРСТВО ОСВІТИ І НАУКИ МОЛОДІ ТА СПОРТУ УКРАЇНИ

Івано-Франківський національний технічний

університет нафти і газу

Кафедра інформаційно–вимірювальної техніки

Ващишак С.П., Мельничук С.І.,

Романів В.М.

Телемеханіка і передача інформації в нафто-газовій промисловості

ЛАБОРАТОРНИЙ ПРАКТИКУМ

Івано–Франківськ

2012

УДК 621.398:622.323

ББК 32.968

В 23

Рецензент:

М.А.Кононенко, кандидат технічних наук, доцент кафедри інформаційно-вимірювальної техніки ІФНТУНГ

Рекомендовано методичною радою університету

( протокол № 1 від 22.10.2012 р. )

Ващишак С.П.

В 23 Телемеханіка і передача інформації в нафтогазовій промисловості: лабораторний практикум/ С.П.Ващишак, С.І.Мельничук, В.М.Романів. – Івано-Франківськ: ІФНТУНГ, 2012. - 100 с.

МВ 02070855-3872-2012

Практикум містить методичні вказівки для проведення лабораторних занять з дисципліни “Телемеханіка і передача інформації в нафтогазовій промисловості ”. Розроблені відповідно до робочої програми навчальної дисципліни.

Призначені для студентів напряму 6.051001“Метрологія та інформаційно-вимірювальні технології”

УДК 621.398:622.323

ББК 32.968

МВ 02070855-3872-2012

© Ващишак С.П., Мельничук С.І.,

Романів В.М., 2012

© ІФНТУНГ, 2012

ВСТУП

Лабораторні роботи виконуються з метою закріплення теоретичних розділів дисципліни і набуття практичних навиків побудови і дослідження функціональних вузлів пристроїв телемеханіки зокрема шифраторів, дешифраторів, пристроїв перетворення паралельного коду в послідовний, пристроїв кодування та декодування для збору та передачі інформації на об’єктах нафто-газової промисловості для студентів за напрямком підготовки “Метрологія та інформаційно-вимірювальні технології ” .

Всі лабораторні роботи виконуються з використанням програмного комплексу MAX +plus II фірми Altera, який має засоби зручного вводу дизайну, контролю та моделювання телемеханічних пристроїв.

Студент зобов’язаний завчасно отримати у викладача варіант технічного завдання на лабораторну роботу. У процесі самостійної підготовки до виконання лабораторної роботи студент повинен обов’язково ознайомитись з рекомендованою літературою та САПР MAX +plus II.

Зміст

Вступ

Лабораторна робота №1.

Ознайомлення із САПР Altera Max Plus +........................7

Лабораторна робота №2.

Створення і дослідження, мультиплексорів,

перетворення паралельного коду в послідовний............23

Лабораторна робота №3.

Дослідження комбінаційних схем з використанням

мультиплексорів................................................................37

Лабораторна робота №4.

Створення і дослідження шифраторів (позиційного коду

в двійковий, двійковий в десятковий) на основі логічних

елементів............................................................................45

Лабораторна робота №5.

Створення і дослідження дешифраторів (двійкового

коду, двійководесяткового в позиційний) на основі

логічних елементів............................................................52

Лабораторна робота №6.

Визначення кількості інформації, оцінка інформаційних

втрат та швидкості передачі для дискретних

інформаційних каналів......................................................62

Лабораторна робота №7.

Побудова кодових комбінацій – розрядних кодів для

кодування повідомлень в телемеханічних системах,

мінімальна та максимальна кодова відстань...................70

Лабораторна робота №8.

Побудова кодів, які виявляють помилки для заданого

ансамблю повідомлень телемеханічних систем.............75

Лабораторна робота №9.

Побудова кодів, які виявляють і виправляютьпомилки

для заданого ансамблю повідомлень телемеханічних

систем.................................................................................80

10. Лабораторна робота №10.

Кодування циклічних кодів методами ділення

інформаційних символів на утворюючий багаточлен та

визначення провірочних символів під час проведення

лінійних операцій..............................................................85

11. Лабораторна робота №11.

Декодування циклічних кодів з використанням схем

ділення першого і другого типу.......................................92

Рекомендована література........................................................100

Лабораторна робота №1

Система проктування елементів і засобів цифрової та

обчислювальної техніки MAX+plus II

1.1 Мета роботи

Набути практичних навиків при проектуванні телемеханічних пристроїв у програмному комплексі MAX+plus II.

1.2 Варіанти завдань

Використовуючи засоби САПР MAX+plus II створити графічний проект, скомпілювати і провести функціональне моделювання логічної функції.

1.2.1

![]()

1.2.2

![]()

1.2.3

![]()

1.2.4

![]()

1.2.5

![]()

1.3 Основні теоретичні відомості

1.3.1 Структура, призначення та опис компонентів

Система автоматизації робіт по проектуванню цифрових та обчислювальних пристроїв МАХ+plus II складається з 11 програм-обробників проекту (прикладних програм), які функціонують під керуванням основної програми Manager (Hierarchy Display, Gpaphic Editor, Symbol Editor, Text Editor, Waveform Editor, Floorplan Editor, Compiler, Simulator, Timing Analizer, Programmer, Message Processor). Системою підтримується повний процес проектування-реалізація, від вводу, контролю опису, моделювання та діагностики проекту до програмування ПЛІС мікросхеми. Такі комплекси тримали назву ЕDА – electronic design automation.

Проект в системі МАХ+рlus II може бути ієрархічним, або складатися з набору модулів. Кожен модуль містить опис частини проекту, причому підтримується довільна форма опису: логічна схема, текст на мовах АНDL/ VHDL / Verilog або логіко-часова діаграма функціонування. Тобто в одному проекті дозволяється використовувати модулі описані різними методами, а ткож модулі з інших проектів.

Для спрощення роботи в МАХ+рlus II наявні бібліотеки готових логічних елементів: примітивів, мегафункцій стандартних цифрових компонентів, мпкрофуикцій застарілого типу ТТЛ-мікросхем 74-тої серії., а також присутня можливість створення компонентів з необхідними властивостям (функціями) та власних бібліотек.

Для створення вихідних модулів пристроїв, їх перевірки, діагностування, функціонального моделювання та укладки в корпус мікросхеми ПЛІС в системі автоматизованого проектування МАХ+рlus II задіяні наступні програми-обробники:

Hierarchy Display - (огляд ієрархії) здійснює візуалізацію усіх модулів поточного проекту, показує їх взаємозв'язки, а також всі типи файлів сформованих в процесі обробки проекту у вигляді дерева з гілками, що являють собою піддизайни;

Graphic Editor - (графічний редактор) призначений для вводу логічноїсхеми частини проекту в формі схеми з'єднань логічних елементів і пристроїв;

Symbol Editor - (редактор символів) призначений для представлення окремих частин проекту, графічних чи текстових, в графічному вигляді як окремих символів (створення макрокомпоненетів), надалі такі символи можна використовувати при створенні ієрархічного проекту;

Text Editor - (текстовий редактор) призначений для вводу текстових компонентів проекту, на мовах АНDL / VHDL / Verilog;

Waveform Editor - (сигнальний редактор) призначений для розробки опису і також інструментом вводу і коригування тестових векторів сигналів та спостереження за результатами функціонального моделювання (симуляції);

Floorplan Editor - (порівневий планувальник) дозволяє побачити зв'язки логічних елементів в середині мікросхеми ПЛІС, призначеній виводів мікросхеми, а також дозволяє коректувати розміщення виводів в корпусі ПЛІС;

Compiler - (компілятор) здійснює обробку вихідних модулів проекту, включаючи трансляцію, розташування і трасування на комірках заданого типу мікросхеми ПЛІС; Simulator - (симулятор) реалізує перевірку функціонування спроектованого пристрою на рівні моделювання, а також здійснює контроль внутрішньої синхронізації логічної схеми. Вхідними даними для нього є файли проекту після трансляції і тестові вектори сигналів, а результатом - логіко-часовї діаграми функцій виходів. Можливі три режими тестування: функціональне, часове і тестування кількох з'єднаних між собою пристроїв;

Timing Analyzer - (аналізатор часових параметрів) здійснює аналіз часових параметрів, визначення критичних шляхів тощо на рівні інструментального моделювання, дозволяє оцінити затримки, що виникають при роботі схеми;

Programmer - (програматор) реалізує процес програмування, конфігурування, здійснює верифікацію і випробування мікросхем ПЛІС та контроль правильності виконання процесу через доступний порт вводу-виводу (LPТ, СОМ, USВ);

Message Processor - (генератор повідомлень) формує повідомлення про помилки та зауваження, які виникли в ході трансляції проекту та іншу службову інформацію, дозволяє автоматично знаходити джерело повідомлення у вихідному чи допоміжному файлі (файлах).

Доцільно зазначити, що вигляд меню основної програми керування Manager залежить від задіяної прикладної програми, тобто на ньому розміщується набір інструментальних панелей актуальний для поточного вікна задіяної програми-обробника.

В загальному проектування цифрових систем на основі великих інтегральних схем (ВІС) програмованої логіки ПЛІС пов'язане з необхідністю освоєння інформації за кількома напрямками: характеристики і особливості мікросхем ПЛІС; методи роботи з використанням автоматизованих систем проектування та специфікація мов опису компонентів HDL.

1.3.2 Створення проекту, параметри файлу проекту, монітор структури проекту

В системі автоматизованого проектування МАХ+рlus II засіб чи пристрій, який розробляється обов'язково подається у вигляді проекту, тобто на початку роботи необхідно визначити параметри поточного проекту:

найменування проекту;

директорію (папку) проекту.

Вказані параметри задаються в діалоговому вікні при одночасному натисканні комбінації клавіш: [ Ctrl ] + [ j ].

Якщо проект вже існус, то необхідний файл можна викликати, в цьому ж діалоговому вікні з переліку Files.

Робочий пристрій і папка (директорія) викликаються за допомогою відповідних меню: Drivers та Directories діалогового вікна, а ім'я файлу проекту вказується в строчці Project Name.

Для прикладу візьмемо наступні параметри:

найменування: example;

директорію: d:\temp\.

При правильному вводі, ім'я (найменування) проекту відобразиться в титульному рядку вікна програми Manager.

Структуру проекту можна побачити скориставшись програмою Hierarchy Display, для виклику якої потрібно вибрати необхідний пункт меню програми Manager.

Враження структури проекту реалізовано у вигляді дерева, де вказано ім'я кожного файлу, його тип та відповідне графічне позначення. Подвійне натискання лівої кнопки маніпулятора "миша" на вибраному і графічному позначенні відкриває файл опису (вихідний файл нижнього рівня) за допомогою відповідного редактора. Зліва від кожної гілки вказуються файли, які створені системою в процесі обробки вихідного файлу (файли з тими ж іменами, але іншими розширннями).

У випадку, коли необхідно задати головний файл верхнього рівня, змінити головний файл проекту, або зв'язати проект з поточним файлом, така ситуація часто виникає при необхідності створення проектів з уже існуючих описів модулів (файли з розширеннями .gdf та .tdf), які не є проектами, проводять зміну параметрів. Для цього відкривають потрібний файл за допомогою відповідного редактора (вікно редактора повніша бути активним) і за допомогою вибору пунктів меню програми Маnager, або при одночасному натисканні комбінапії клавіш: [ Сtrl ] + [ Shift ] + [ j ] перетворюють його в головний файл проекту (верхнього рівня). Змінену структуру проекту можна побачити скориставшись програмою Нierarchy Display.

1.3.3 Внесення логічної схеми пристрою за допомогою графічного редактора Graphic Editor

Після того, як визначено параметри проекту, див.п.1.3.2, за допомогою графічного редактора – Graphic Editor можна здійснити внесення схеми засобу, який проектується у вигляді електричної схеми з'єднань логічних елементів.

Для виклику графічного редактора необхідно вибрати необхідний пункт меню програми Мanager.

Перед вводом логічної схеми за допомогою редактора Graphic Editor обов'язково потрібно задати ім'я графічного файлу, розширення .gdf (Graphic Design File). Для цього виберіть пункт меню програми Маnager: File→Save As, після чого наберіть ім'я створюваного файлу у рядку File Nате: діалогового вікна.

Внесення графічних позначень логічних елементів в схему, яка проектується, здійснюється за рахунок їх імпортування з відповідної бібліотеки, або власного файлу (розширення .sym), який описує роботу потрібного елементу. Виклик діалогового вікна вводу елементу, здійснюється за допомогою подвійного натискання лівої клавіші маніпулятора "миша" в тому місці робочого вікна програми Graphic Editor де повинен вноситись елемент; або за допомогою вибору відповідних пунктів меню програми Мапager.

В діалоговому вікні, потрібно вказати пристрій Drivе та директорію (папку) Directories: в якій є бібліотеки логічних елементів, далі необхідно викликати потрібну бібліотеку зі списку Symbol Libraries, після чого в меню Symbol Files виводиться перелік наявних логічних елементів,

Встановлення шляхів до власних бібліотек логічних елементів здійснюється в діалоговому вікні User Libraries, яке можна викликати за допомогою меню: Орtіоns → User Libraries... програми Мапager при активному вікні програми Graphic Editor.

Подвійне натискання лівої клавіші маніпулятора "миша" на потрібному елементі приводить до копіювання його графічного позначення у робоче вікно Graphic Editor, в позицію попередньо визначену курсором, аналогічно здійснюється імпортування та розміщення усіх інших елементів, які потрібні для побудови схеми.

Одноразове натискання лівої клавіші маніпулятора "миша" на елементі здійснює його вибір, про що свідчить поява зовнішньої рамки червоного кольору. Після цього, не відпускаючи ліву клавішу маніпулятора, можна пересовувати в межах вікна графічного редактора.

Для видалити непотрібних елементів схеми у вікні графічного, редактора достатньо здійснити вибір таких елементів і натискання клавіші функціональної клавіатури

[ Deletе ].

Для зручнішого та точнішого позиціонування елементів доцільно викликати координатну сітку у вікні редактора викликавши меню Options → Show Guidelines, програми Мапager.

У внутрішній бібліотеці примітивів \рrim, яка найчастіше розташована <пристрій>:\тах3р1иs\тах2lib\prim\*, присутні практично всі необхідні логічні елементи для реалізації схем. Як приклад розглянемо деякі з них за функціональним призначенням:

input - вхідний порт (сигнальна лінія);

output - вихідний порт (сигнальна лінія);

not -інвертор;

or2 - логічне "АБО";

bor2 - логічне "АБО" з інвертованими входами;

nor2 - логічне "АБО" з інвертованим виходом;

bnor2 - логічне "АБО" з інвертованими входами та

виходом;

and2 - логічне "І"; band2 - логічне "І" з інвертованими входами;

n a n d 2 - логічне "І" з інвертованим виходом;

b n a n d 2 - логічне "І" з інвертованими входами та

виходом;

Доцільно зазначити, що кількість входів елементу може бути від 2 до 12.

Детальніші пояснення, стосовно інших елементів та біблютек можна отримати, скориставшись довідковою системою автоматизованого комплексу проектування МАХ+рlus II.

Після того, як внесено всі логічні елементи і символи вхідних та вихідних портів обов'язково потрібно присвоїти нові імена усім портам. Для цього натисніть праву клавішу маніпулятора "миша" на графічному позначенні порту (властивості елементу) і в меню виберіть пункт Edit Ріп Nате, після чого замініть стару назву елементу (порту) своєю, новою. Аналогічним чином потрібно змінити всі назви вхідних та вихідних портів.

Наступним кроком є формування схеми за допомогою з'єднувальних її ній, що здійснюється за допомогою горизонтальних і вертикальних відрізків прямих. Натисніть (втопіть) кнопку на панелі вибору об'єкта (зображено стрілочку), якщо після цього підвести курсор до кінця лінії виводу елементу, то його зображення трансформується у вигляд хрестика, а пісня натискання лівої клавіші маніпулятора "миша" з подальшим переміщенням потягне за собою з'єднувальну лінію (node), яка закінчиться при відпусканні клавіші маніпулятора.

Для того, щоб стерти непотрібний елемент з'єднання в схемі достатньо активізувати такий елемент або групу елементів, утримуючи при цьому клавішу [ Shift ], і натиснути клавішу функціональної клавіатури [ Delete ].

1.3.4 Компіляція реалізованої схеми (опису) пристрою за допомогою програми Сотріler

Після вводу схеми виконується етап аналізу і генерування булевих рівнянь для всіх логічних функцій проекту.

Перед проведенням компіляції необхідно вибрати тил мікросхеми ПЛМ на якій буде реалізовано проект. Для цього потрібно викликати діалогове вікно Device, за допомогою пунктів меню: Assign → Device…, програми Manager, після чого вказати бажаний тип мікросхеми. У випадку, коли тип мікросхеми наперед невідомий, доцільно залишити режим (Аutо) автоматичного підбору мікросхеми.

Виклик компілятора - Compiler здійснюється через відповідний пункт меню програми Мапаger.

Після завершення компіляції проекту, у вікні програми Message Processor виводяться зауваження (синім кольором) та помилки (червоним кольором), якщо такі знайдено, а також службова інформація по проекту.

Для зменшення часу перекомпіляції проекту доцільно встановити опцію: Smart Recompile, попередньо вибравши за допомогою пунктів меню: Processing → Smart Recompile, програми Manager. Крім того можна перевірити (всі файли проекту на відповідність до правил реалізації на вибраній мікросхемі ПЛІС, що: здійснюється за допомогою утиліти: Processing → Design Doctor.

У випадку успішного завершення процесу компіляції, потрібно вікно програми Compiler закрити, а файли проекту записати.

Функціональне моделювання (симуляція) відкомпільо-ваної схеми (опису) пристрою за допомогою програми Simulator

Моделювання, як правило – функціональний процес використанням програмно-логічної моделі. В нашому випадку для перевірки функціонування пристрою необхідно створити тестові вектори, які характеризують значення вхідних сигналів. Іншими словами – створити сигнальну модель можливих станів на входах спроектованого пристрою.

Для створення секторів сигналів (сигнальної моделі) необхідно скористатись сигнальним редактором – Waveform Editor, викликавши допомогою відповідних пунктів меню програми Manager.

Перед формуванням тестових векторів за допомогою редактора Waveform Editor обов'язково потрібно задати ім'я сигнального файлу, розширення .scf (Simulator Channel File), для цього викличте пункт меню програми Мanager: File → Save As і наберіть ім'я створюваного файлу у рядку File Name: діалогового вікна.

Наступним кроком є визначення вхідних та вихідних ліній схеми для проведення процесу моделювання, для цього використовується файл з розширенням .snf (Simulator Node File), який автоматично створюється на етапі компіляції проекту схеми, п.1.3.4.

Виклик діалогового вікна визначення вхідних та вихідних ліній схеми, здійснюється за допомогою двахразового натискання лівої клавіші маніпулятора "миша" в колонці Nате: робочого вікна програми Waveform Editor, або щляхом виклику відповідних пунктів меню програми Мапаger. Внесення задіяних ліній проекту схеми можна реалізувати наступними способами:

почергово вказати назви усіх задіяних ліній у рядку Node Name:, їх типи в І/О Туре та значення рівня сигналу по замовчуванню в Default Value;

натиснути кнопку List нижньої частини діалогового вікна Insert Node, після чого перелік наявних ліній виводиться з snf-файлу у вікно cписку Node & Group from SNF, далі почергово викликати необхідні для моделювання лінії.

У вигпадку, коли всі вхідні та вихідні лінії проекту потрібно використати при моделюванні доцільніше скористатись діалоговим вікном Insert Node from SNF, програми Мanager, котре викликається за допомогою пунктів меню: Node → Insert Node from SNF. В цьому випадку відкриється два вікна: Available Nodes & Groups та Selected Nodes & Groups. Після натискання кнопки List в перше вікно виводиться перелік вхідних і вихідних ліній із .snf-файлу. Далі потрібно І активізувати необхідні для симуляції лінії по одній чи блоком і натиснути кнопку переносу [=>] між вікнами. Щоб активізувати одну лінію – натисть ліву клавішу маніпулятора "миша" попередньо підвівши курсор на неї, щоб активізувати блок - проведіть курсором між потрібними лініями утримуючи при цьому ліву клавішу маніпулятора.

Після внесення всіх в х ідних та в их ідн их сигнальних ліній , потр ібно встановити наступні параметри процесу моделювання:

тривалість процесу функціонального моделювання;

інтервал сітки вікна редактора Waveform Editor;

початкові значення сигналів на вхідних лініях, колонка Value;

вектори тестових сигналів для всіх вхідних ліній.

Виклик діалогового вікна встановлення тривалості процесу моделювання здійснюється за допомогою вибору відповідних пунктів меню програми Manager, після чого вказується тривалість з обов'язковим позначенням розмірності часового інтервалу:

ns - наносекунди;

ms - мілісекуиди;

us - мікросекунди;

s - секунди;

mhz - мегагерци.

Виклик діалогового вікна встановлення інтервалу сітки вікна редактора Waveform Editor здійснюється за допомогою вибору відповідних пунктів меню програми Manager, після чого вказується величина інтервалу з обов’язковим позначенням розмірності часового інтервалу.

Встановлення початкових значень сигналів на вхідних та вихідних лініях здійснюється за допомогою відповідних функціональних кнопок:

[ 0 ] - значення логічного "0";

[ 1 ] - значення логічної "1";

[ х ] - невизначений стан (для вихідних ліній);

Навпроти вибраної сигнальної лініїї виділити стару величину (місце) в колонці Value після чого, за допомогою відповідної кнопки встановити необхідне значення.

Для забезпечення повного моделювання функціонування пристрою необхідно подати на входи всі можливі комбінації значень сигналів. Враховуючи те, що в нашому випадку задіяно лише дві вхідні лінії, то кількість комбінації буде: 2²=4. Тривалість кожної комбінації при повному інтервалі моделювання в 80ns складатиме: 80/4=20(ns).

Для редагування часової діаграми вектору активізують потрібну ділянку вхідної лінії, для цього утримуючи ліву клавішу маніпулятора "миша" натиснутою перемістіть курсор вздовж інтервалу, значення якого буде змінюватись (виділиться чорним кольором). Використовуючи функціональні

панелі клавіш: [ 0 ], або [ 1 ] встановити потрібне значення. Аналогічним чином редагуються всі вектори сигналів. Після того як встановлено всі параметри моделювання потрібно обов'язково зберегти створений файл.

Виклик діалогового вікна встановлення інтервалу сітки вікна Waveform Editor здійснюється за допомогою вибору відповідних пунктів меню програмі Мanager, а далі вказується інтервал з позначенням розмірності.

Моделювання відкомпільованого опису згідно збереженого .snf-файлу сигнальної моделі виконується програмою Simulator, викликаною за допомогою відповідних пунктів меню програми Manager.

В діалоговому вікні Simulator, вказується час початку та завершення процесу моделювання з обов'язковим позначенням розмірності:

Star Тіте - задається нульове значеная (моделювання з початку вектора), або значення початку інтервалу (симуляція з заданої позиції вектора);

End Тіте - задається кінцеве значення (симуляція до кінця вектора), або значення кінця інтервалу (симуляція до заданої позиції вектора), моделювання здійснюється після натискання панелі кнопки Start.

Після успішного завершення моделювання проекту, коли відсутнє вікно програми Мessage Processor, тобто у вікні програми відсутні повідомлення про помилки, вікно програми Simulator закрити, результати функціонального моделювання виводяться у вікні редактора Waveform Editor.

1.3.6 Програмування (запис в мікросхему ПЛІС) відкомпільованої схеми (опису) пристрою за допомогою програми Рrogrammer

Більшість мікросхем ПЛІС фірми "Altera" програмуються в системі через стандартний чотирьохконтактний JTAG-інтерфейс. Програмне забезпечення створює конфігураційну послідовність, що записується в ПЛІС за допомогою спеціалізованого загрузочного кабелю: ByteBlaster, BitBlaster або MasterBlaster.

Програмування мікросхем ПЛІС та контроль правильності виконання процесу здійснюється за допомогою програми-обробника Programmer, виклик якої здійснюється за допомогою вибору відповідних файлів меню програм Мanager.

В діалоговому вікні Рrogrammer, вибирається необхідний файл. Перелік, наявних пунктів та функції наступні:

Рrogram - запис файлу проекту в одну, або більше незаписаних (очищених) мікросхем ПЛМ;

Verify - контроль відповідності (правильності) записаних в мікросхему даних і даних файлу проекту; Ехamine - перевірка (огляд) можливості запису проекту в мікросхему (додаткові дані в документації виробника);

Blank-Check - контроль наявності даних в мікросхемі, перевірка на успішність очистки мікросхеми ПЛМ; Configure - зчитування конфігурації з одного, або більше файлів проекту;

Test - функціональне моделювання записаної мікросхеми ПЛМ на в ідпо в і дн і сть попередн ьо змодельованим тесто ви м векторам..

Запис мікросхеми здійснюється через відповідні пристрої (програмахори), які під’єднуються до доступного порту вводу-виводу (LРТ, СОМ, USВ).

Доцільно зазначити, що процес програмування може здійснюватись тільки для тих ПЛІС, які дозволяють здійснити запис інформації безпосередньо в складі системи без використання програматора, на змонтованій платі, причому програмування ПЛІС або конфігураційного ПЗП може здійснюватись багатократно. Реконфігурування в схемі (In Circuit Reconfigurability, ISR) дозволяє здійснювати перезавантаження даних в ПЛІС, яка реалізована по SRАМ технології без виключення живлення з наступаючим перезавантаженням нової конфігурації.

Внесення опису логічного функціонування пристрою за допомогою текстового редактора Теxt Еditor

Опис функціонування пристрою реалізується на мовах АНDL і VНDL за допомогою текстового редактора – Техt Еditor можна здійснювати окремим проектом (після того, як визначено параметри проекту, див.п.1.3.2) і частиною, або доповненням функціональого вузла уже існуючого проекту.

Для виклику текстового редактора необхідно вибрати необхідний файлменю програми Manager .

Перед вводом опису функціонування за допомогою Техt Editor обов’язков потрібно задали ім'я текстового файлу, розширення .tdf (Text Design File), дл цього виберіть пункт меню, програми Мanager: File → Save As, далі наберіть ім’я створюваного файлу у рядку File Name: діалогового вікна.

Внесення текстового опису цифрової схеми здійснюється за допомогою мови АНDL (Altera Hardware Description Language). При вводі тексту доцільно використовувати готові шаблони конструкцій мови, які можна викликати вибравши файл меню програми Мапаger: Templates → AHDL Template…, після чого з діалогового вікна вибрати потрібну конструкцію. В розділі Тitlе задається текст заголовку для формування файлу Report File (.rpt), обов'язковим є розділ Subdesign, в ньому описуються усі вхідні і вихідні порти (сигнальні лінії).

В розділі Logic, який починається ключовим словом ВEGIN і закінчуетьі END, здійснюється опис функціонування за допомогою відповідних рівняв умовних операторів, операторів псевдоциклу тощо, який зв'язує значена сигналів на вхідних і вихідних портах.

Наступним етапом є проведенням компіляції проекту, який здійснюються аналогічно до п.1.3.4. Після успішного завершення компіляції проводиться функціональне моделювання (симуляція) проекту, аналогічно до п.1.3.5.

1.3.8 Створення нових функціональних блоків (макрокомпонентів) з використанням редактора Symbol Editor

Створення власних функціональних модулів зручніше здійснювати як окремі проекти. Тобто створювати проект макрокомпоненту, описувати його роботу за допомогою графічного (Graphic Editor) п.1.3.3, або текстового (Text Editor) п.1.3.7 редакторів, компілювати п.1.3.4 і проводити функціональне моделювання п.1.3.5. Після чого, уже відлагоджений, опис перетворюють в окремий компонент, що здійснюється за допомогою вибору відповідних файлів меню програми Manager.

В результаті такої операції формується файл з розширенням sym, в нашому випадку example.sym, позначення якого можна побачити скориставшись програмою Hierarchy Display. Редагування та доповнення здійснюється в діалоговому вікні Symbol Editor, яке викликається: TMAX+plusII → Symbol Editor програми Мапаger.

Фактично так створюється незалежний спеціалізований модуль з власною, назвою та функціональним призначенням, який можна використовувати в різних пристроях, викликаючи аналогічно до п.1.3.3 через діалогове вікно і безпосередньо вибираючи файл з описом потрібного макрокомпонеиту зі списку Symbol Libraries без встановлення бібліотеки.

1.4 Порядок виконання робіт циклу

1.4.1 Ознайомитися із метою лабораторної роботи та основними теоретичними відомостями.

1.4.2 Отримати у викладача завдання згідно варіанту.

1.4.3 Використовуючи програмний комплекс MAX+plus II реалізувати задану функцію.

1.4.4 Оформити звіт з результатами роботи.

1.5 Контрольні питання

1.5.1 З яких розділів складається САПР MAX+plus II?

1.5.2 Яким чином визначаються параметри поточного проекту?

1.5.3 Як здійснюється внесення схеми пристрою, який проектується у вигляді електричної схеми?

1.5.4 Як вибрати елемент із стандартної бібліотеки логічних елементів?

1.5.5 Як можна створити свою бібліотеку елементів?

1.5.6 Як і для чого проводиться компіляція реалізованої схеми пристрою?.

1.5.7 Основні етапи функціонального моделювання відкомпільованої схеми пристроїв.

1.5.8 Яким чином здійснюється внесення опису логічного функціонування пристроїв за допомогою текстового редактора?

Лабораторна робота №2

Створення і дослідження мультиплексорів, претворення паралельного коду в послідовний

2.1 Мета роботи

Вивчення принципів побудови перетворювачів паралельного коду в послідовний, ознайомлення з варіантами побудови перетворювачів, практична реалізація і дослідження роботи схем, що синтезуються на мультиплексорах і інших елементах середнього ступеня інтеграції

2.2 Варіанти завдань

2.2.1 Розробка і дослідження 4-розрядного перетворювача паралельного коду в послідовний із застосуванням мультиплексора 4:1.

2.2.2 Розробка і дослідження 8-разрядного перетворювача паралельного коду в послідовний із застосуванням мультиплексора 8:1.

2.2.3 Розробка і дослідження 16-розрядного перетворювача паралельного коду в послідовний із застосуванням мультиплексора 16:1.

2.2.4 Розробка і дослідження 8-розрядного перетворювача паралельного коду в послідовний із застосуванням мультиплексора 8:1, синтезованого за пірамідальною схемою за допомогою мультиплексорів 4:1.

2.2.5 Розробка і дослідження 16-розрядного перетворювача паралельного коду в послідовний із застосуванням мультиплексора 16:1, синтезованого за пірамідальною схемою за допомогою мультиплексорів 8:1.

2.2.6 Разработка і дослідження 16-розрядного перетворювача паралельного коду в послідовний із застосуванням мультиплексора 16:1, синтезованого по послідовній схемі за допомогою мультиплексорів 8:1.

2.3 Основні теоретичні відомості

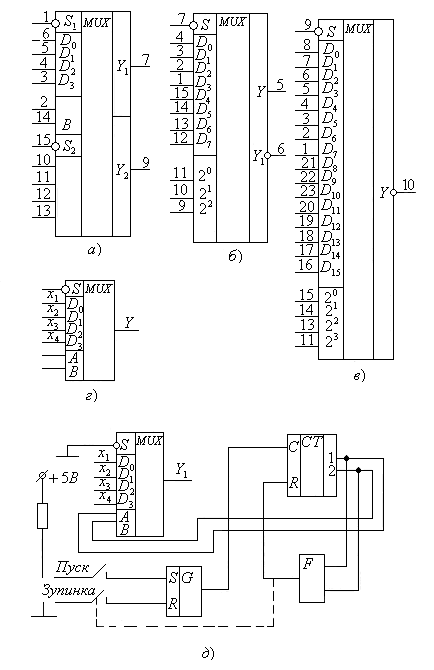

Для побудови перетворювачів паралельного коду в послідовний можна використовувати спеціальні мікросхеми – мультиплексори. Призначення мультиплексорів – комутувати в бажаному порядку інформаційні сигнали з декількох вхідних шин на одну вихідну. На рис. 2.1, показаний мультиплексор, комутатор чотирьох вхідних шин, що є, на одну вихідну 4:1.

Мультиплексор

(комутатор) є комбінаційною багато

вхідною логічною схемою з одним виходом.

Входи мультиплексора поділяються на

інформаційні![]() і керуючі . Керуючі входи у свою чергу

діляться на адресні

і керуючі . Керуючі входи у свою чергу

діляться на адресні

![]() і, що стробують

і, що стробують

![]() .

Якщо мультиплексор має адресних входів,

то кількість його інформаційних входів

дорівнює

.

Якщо мультиплексор має адресних входів,

то кількість його інформаційних входів

дорівнює

![]() .

При подачі на адресні входи сигналу у

вигляді двійкового коду до виходу

мультиплексора підключається один із

його інформаційних входів, номер якого

відповідає цьому двійковому коду (при

наявності вирішального сигналу на

вході, що стробує ). Вхід, що стробує

керує

всіма інформаційними входами незалежно

від стану адресних. Заборонений сигнал

на стробуючому вході блокує роботу

всього мультиплексора. Наявність

стробуючого входу розширює функціональні

можливості мультиплексора, та дозволяє

синхронізувати його роботу з роботою

інших вузлів. Стробуючий вхід

використовується також для нарощування

розрядності мультиплексора.

.

При подачі на адресні входи сигналу у

вигляді двійкового коду до виходу

мультиплексора підключається один із

його інформаційних входів, номер якого

відповідає цьому двійковому коду (при

наявності вирішального сигналу на

вході, що стробує ). Вхід, що стробує

керує

всіма інформаційними входами незалежно

від стану адресних. Заборонений сигнал

на стробуючому вході блокує роботу

всього мультиплексора. Наявність

стробуючого входу розширює функціональні

можливості мультиплексора, та дозволяє

синхронізувати його роботу з роботою

інших вузлів. Стробуючий вхід

використовується також для нарощування

розрядності мультиплексора.

Мультиплексори

відрізняються в основному кількістю

адресних і інформаційних входів ,

наявністю або відсутністю входу, що

стробується , а також характером вихідних

сигналів, які можуть бути прямими

![]() ,

інверсними

,

інверсними

![]() або парними . Відповідно розрізняють

мультиплексори 4:1, 8:1, 16:1.

або парними . Відповідно розрізняють

мультиплексори 4:1, 8:1, 16:1.

Рис. 2.1 Структурні схеми мультиплексорів та перетворювача чотирьохрозрядного коду в послідовний

Функціонування мультиплексора, приведеного на рис. 2.1,г, може бути представлено таблицею істинності (табл. 2.1) або у вигляді логічної функції, що виконується мультиплексором

![]() (2.1)

(2.1)

Таблиця істинності мультиплексора 4:1 рис 2.1

Входи |

Вихід |

||

Стробуючий |

Адресні |

||

|

|

||

0 |

0 |

0 |

|

0 |

1 |

0 |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

* |

* |

0 |

Примітка: * – довільне значення.

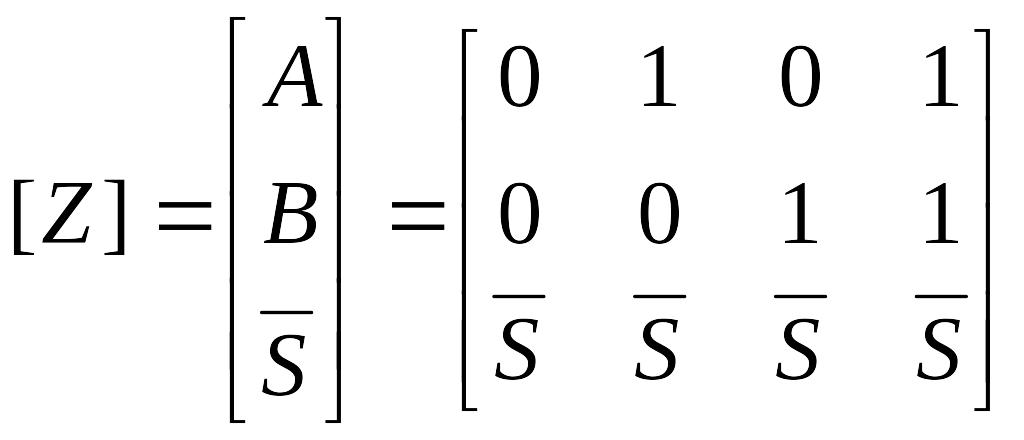

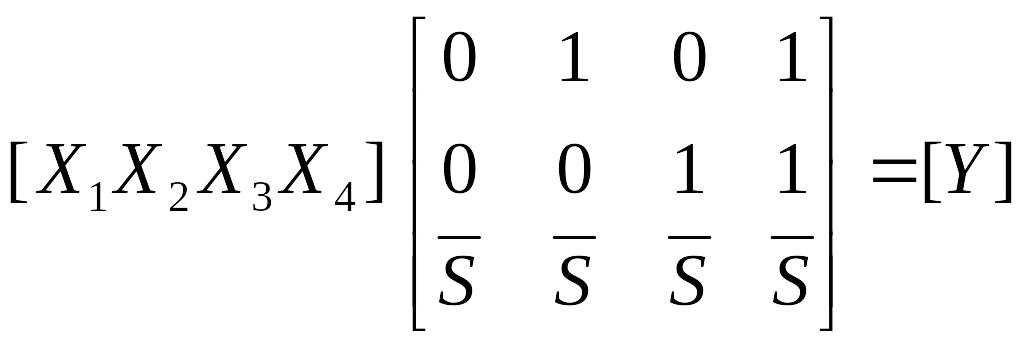

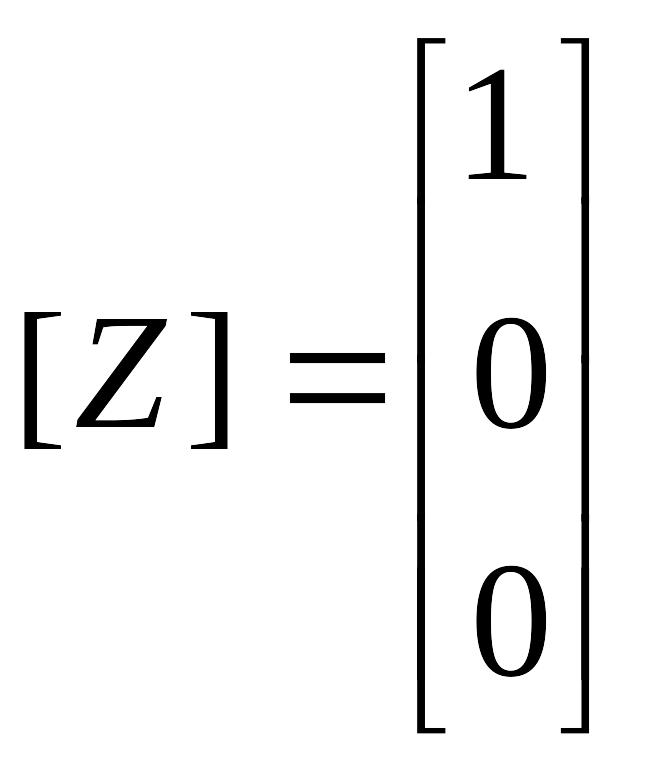

В процесі проектування логічну функцію (2.1), що виконується мультиплексором, зручно представити в матричному вигляді

(2.2)

де – матриця вхідних змінних.

Матриця

адресації,

в якій

– молодший розряд адресних змінних,

– старший розряд адресних змінних, –

сигнал на стробуючому вході мультиплексора,

матриця вихідних змінних.

в якій

– молодший розряд адресних змінних,

– старший розряд адресних змінних, –

сигнал на стробуючому вході мультиплексора,

матриця вихідних змінних.

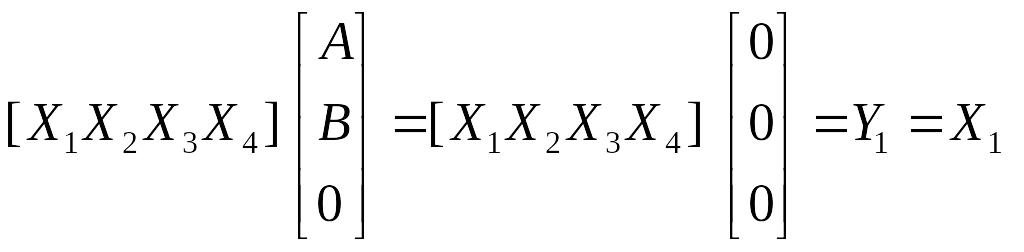

В результаті для мультиплексора, приведеного на рис. 2.1, г, отримуємо

(2.3)

(2.3)

Значення

вихідної змінної

![]() можуть бути визначені вживанням операції

логічного множення матриці вхідних

змінних на матрицю адресації При

виконанні операції логічного множення

значення вихідної функції ототожнюється

з конкретною вхідною змінною (стовпцем

матриці вхідних змінних , яка вибирається

відповідним значенням, (стовпцем) матриці

– ця операція називається також

адресацією.

можуть бути визначені вживанням операції

логічного множення матриці вхідних

змінних на матрицю адресації При

виконанні операції логічного множення

значення вихідної функції ототожнюється

з конкретною вхідною змінною (стовпцем

матриці вхідних змінних , яка вибирається

відповідним значенням, (стовпцем) матриці

– ця операція називається також

адресацією.

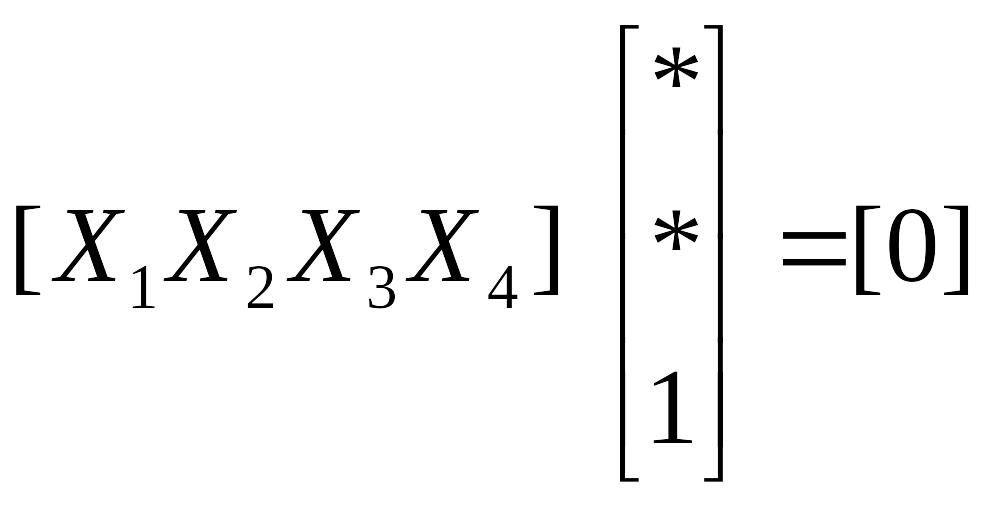

Наприклад,

при

вихідна змінна (функція) прирівнюється

вхідній змінній яка є першим стовпцем

матриці ,

вихідна змінна (функція) прирівнюється

вхідній змінній яка є першим стовпцем

матриці ,

![]() .

.

Для

вихідна змінна прирівнюється вхідній

змінній

вихідна змінна прирівнюється вхідній

змінній![]() ,

яка є другим стовпцем матриці , і так

далі. За наявності заборонного сигналу

на стробуючому вході , незалежно від

сигналів на адресах входах . вихідна

функція

набуває значення, дорівнює нулю тобто

,

яка є другим стовпцем матриці , і так

далі. За наявності заборонного сигналу

на стробуючому вході , незалежно від

сигналів на адресах входах . вихідна

функція

набуває значення, дорівнює нулю тобто

Ці правила логічного множення матриць розповсюджуються на складніші випадки декількох мультиплексорів.

Побудова

перетворювачів паралельного коду в

послідовний на мультиплексорах

здійснюється таким чином. Для цього на

інформаційні входи

необхідно подати розряди паралельного

коду

![]() в тому порядку, в якому повинен формуватися

послідовний код. При циклічній зміні

двійкового коду на адресних входах

в тому порядку, в якому повинен формуватися

послідовний код. При циклічній зміні

двійкового коду на адресних входах

![]()

на виході мультиплексора буде послідовно формуватимутися сигнал

![]()

тобто

послідовний код. Для циклічної зміни

код на адресних входах мультиплексора

можна використовувати відповідні виходу

двійкового лічильника при подачі на

його вхід тактових імпульсів від окремого

генератора. Структурна схема перетворювача

паралельної чотирирозрядного коду в

послідовний представлена на рис.2.1, д.

Робота схеми відбувайся таким чином.

До запуску генератора тактових імпульсів

![]() на виходах лічильника

на виходах лічильника

![]() і відповідно на адресних входах

мультиплексора

і відповідно на адресних входах

мультиплексора

![]() присутній

код

присутній

код

![]() .

Відповідно до логіки роботи мультиплексора

(2.3) його вихідний сигнал рівний

.

Відповідно до логіки роботи мультиплексора

(2.3) його вихідний сигнал рівний

![]() .

При запуску генератора

і надходженні на вхід лічильника СТ2

одного тактового імпульсу на його

виходах

.

При запуску генератора

і надходженні на вхід лічильника СТ2

одного тактового імпульсу на його

виходах

![]() з’явиться код

з’явиться код

![]() ,

що приводить до появи на виході

сигналу

,

що приводить до появи на виході

сигналу

![]() .

Після надходження на вхід лічильника

трьох тактових імпульсів на його виходах

1, 2 формується код I, I і на виході

з'являється сигнал

.

Після надходження на вхід лічильника

трьох тактових імпульсів на його виходах

1, 2 формується код I, I і на виході

з'являється сигнал

![]() .

Код

.

Код

![]() на виході лічильника відповідає його

заповненню. При цьому на виході формувача

на виході лічильника відповідає його

заповненню. При цьому на виході формувача

![]() формується

сигнал, який, поступаючи на вхід

формується

сигнал, який, поступаючи на вхід

![]() лічильника, повертає його в початковий

стан, при якому код на його виходах знову

приймає значення

.

лічильника, повертає його в початковий

стан, при якому код на його виходах знову

приймає значення

.

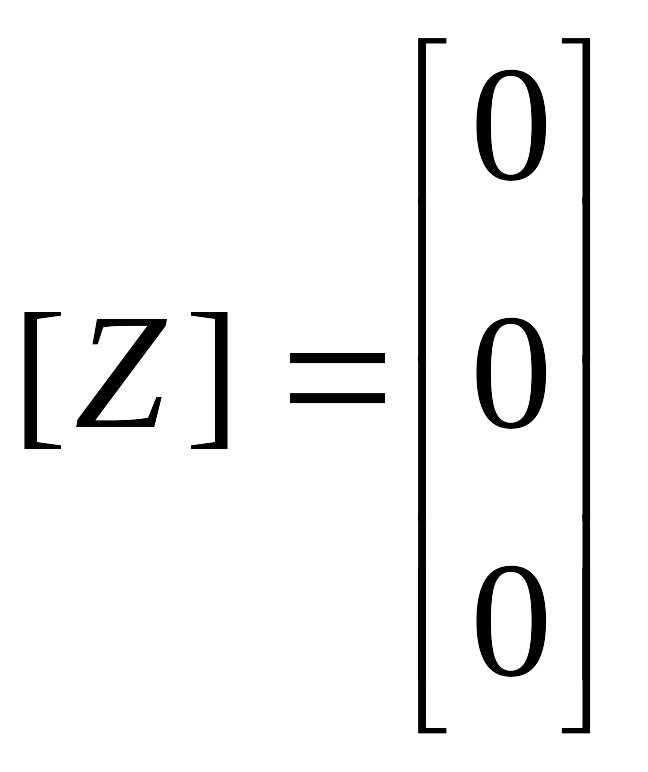

Після цього цикл роботи перетворювача повторюється. Це відповідає "циклічному" режиму роботи перетворювача. Для роботи перетворювача в одноразовому або "спорадичному" режимі сигнал виходу формувача повинен не тільки повертати лічильник в початковий стан, але і зупиняти генератор тактових імпульсів . Для цього повинен існувати додатковий зв'язок виходу формувача з входом "зупинка" генератора (на рис.2.1, д цей додатковий зв'язок показаний пунктирною лінією). У "спорадичному" режимі перетворювач перетворить паралельний код на його вході в послідовний код на його виході, після чого повернеться в початковий стан і зупинить свою роботу.

При збільшенні числа вхідних змінних паралельного коду на вході перетворювача виникає проблема нарощування розрядності мультиплексорів. Нарощування розрядності мультиплексорів можна виконати двома способами: об'єднанням декількох мультиплексорів в пірамідальну схему, об'єднанням в послідовну схему з використанням стробуючих входів як старші розрядів адресних входів.

Пірамідальний характер схеми полягає в тому, що кожен ступінь, починаючи з першої, має більше входів чим подальша. Зазвичай застосовують 2, рідше 3 і більше ступенів.

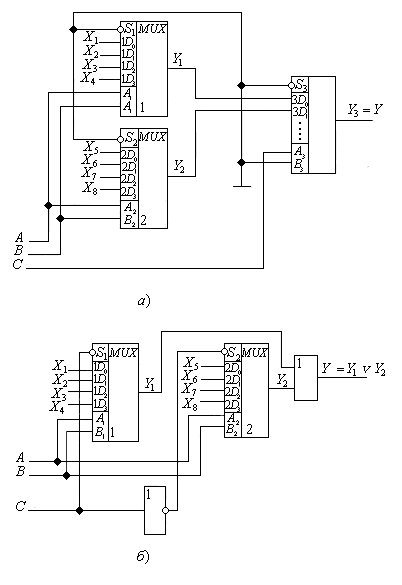

При цьому молодші розряди коди адреси подаються на адресні входу першого ступеня, а ступеням вищого рангу відповідають старші розряди коду адреса. На рис.2.2, а показаний варіант побудови мультиплексора 8:1 по пірамідальній схемі з використанням розглянутих вище мультиплексорів 4:1. Логічна функція, що виконується даною схемою, може бути представлена в загальному вигляді

(2.4)

(2.4)

Для конкретних вхідних змінних і сигналів на адресних входах мультиплексорів вона приймає вигляд

(2.5)

(2.5)

Ця форма

запису дає вичерпну інформацію про

значення всіх сигналів, присутніх в

даній схемі. Наприклад, якщо змінні

![]() мають значення

мають значення

![]() ,

то значення вихідного сигналу

може бути визначене як логічний добуток

першого рядка матриці вхідних змінних

на перший стовбець матриці адресації

,

то значення вихідного сигналу

може бути визначене як логічний добуток

першого рядка матриці вхідних змінних

на перший стовбець матриці адресації

(2.6)

(2.6)

Значення

вихідного сигналу

![]() відповідно рівно логічному множенню

2-го рядка на другий стовбець

відповідно рівно логічному множенню

2-го рядка на другий стовбець

(2.7)

(2.7)

і значення

вхідного сигналу

![]() дорівнює логічному множенню 3-го рядка

на 3-ій стовбець

дорівнює логічному множенню 3-го рядка

на 3-ій стовбець

(2.8)

(2.8)

Р исунок

2.2 Структурні схеми збільшення розрядності

мультиплексорів

исунок

2.2 Структурні схеми збільшення розрядності

мультиплексорів

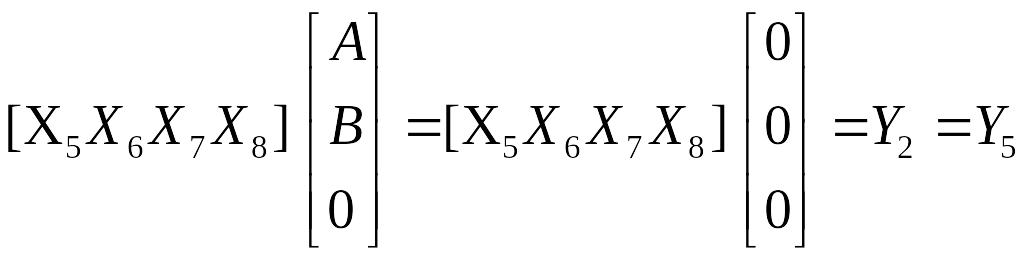

Оскільки

виходом

![]() синтезованої схеми мультиплексора 8:1

є вихідний сигнал

,

то

синтезованої схеми мультиплексора 8:1

є вихідний сигнал

,

то

![]() .

Аналогічно можна визначити значення

виходів

для будь-якого значення змінних

.

.

Аналогічно можна визначити значення

виходів

для будь-якого значення змінних

.

Недоліками пірамідального нарощування слід вважати підвищену витрату мікросхем, а також порівняно невисока швидкодія із-за підсумовування затримок при послідовному проходженні сигналів по ступенях піраміди.

Послідовна схема з використанням стробуючих входів як старших розрядів адресних входів немає таких недоліків, але вимагає додаткової зовнішньої логіки.

На рис.2.2,б показаний варіант побудови мультиплексора 8:1 синтезованого за послідовною схемою на основі мультиплексорів 4:1. Логічна функція, що виконується даною схемою, може бути передставлена в загальному вигляді як

(2.9)

(2.9)

або для конкретних вхідних змінних на адресних входах

(2.10)

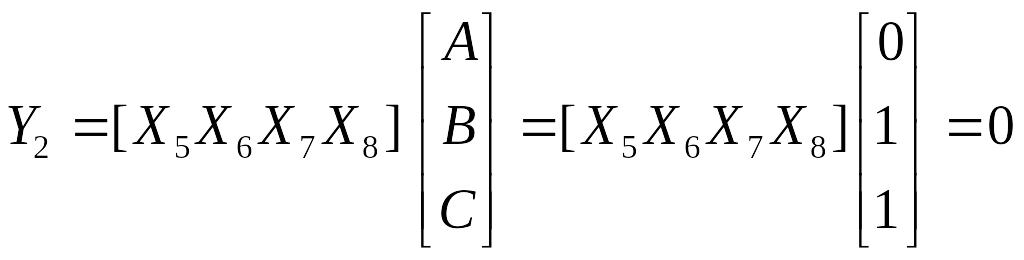

(2.10)

Роботу

даної схеми можна розглянути на прикладі.

Нехай змінні

мають значення

![]() ,

тоді

,

тоді

(2.11)

(2.11)

(тут як і раніше мається на увазі логічне множення рядка на відповідний стовбець, тобто адресація),

(2.12)

(2.12)

оскільки

сигнал на стробуючому вході

![]() мультиплексора рівний

мультиплексора рівний

![]() ,

що блокує роботу цього мультиплексора.

,

що блокує роботу цього мультиплексора.

Вихідний

сигнал

![]() (2.13)

(2.13)

Схема управління синтезованими мультиплексорами збільшеної розрядності відрізнятиметься від приведеної на рис.2.1,д тільки числом розрядів (виходів) лічильника СТ2 відповідно до числа адресних змінних вказаних мультиплексорів

2.4 Порядок виконання робіт циклу

2.4.1 Ознайомитися з описом лабораторної роботи і короткими відомостями з теорії.

2.4.2 Отримати у викладача технічне завдання.

2.4.3 Скласти структурну схему перетворювача.

2.4.4 По структурній схемі скласти матриці вхідних змінних, адресації і вихідних змінних для перетворювача на мультиплексорах.

2.4.5 Використовуючи засоби автоматизованого проектування MAX+II: створити графічний проект, скомпілювати та провести функціональне моделювання логічної функції.

2.4.6 Порівняти дані експерименту з даними 2.4.4

2.5 Контрольні питання

2.5.1 Мультиплексори.

2.5.2 Універсальні регістру зсуву.

2.5.3 Лічильники

2.5.4 Генератори тактових імпульсів.

2.5.5 Перелічувальні схеми.

2.5.6 Регістри індикації.

2.5.7 Логічні елементи.

2.5.8 Пірамідальна схема нарощування структури мультиплексора.

2.5.9 Послідовна схема нарощування структури мультиплексора.

2.5.10 Перетворювачі паралельного коду в послідовний на мультиплексорах

2.5.11 Матриці вхідних змінних, адресації і вихідних змінних для перетворювача на мультиплексорах.

Лабораторна робота №3

Дослідження комбінаційних схем з використанням

мультиплексорів

3.1 Мета роботи

Вивчення принципів побудови комбінаційних схем на базі мультиплексорів.

3.2 Варіанти завдань

3.2.1 Розробка і дослідження схеми, контролю коду на парність для 3-розрядного коду.

3.2.2 Розробка і дослідження схеми контролю коду на непарність для 4-розрядного коду.

3.2.3 Розробка і дослідження мажоритарного логічного елементу на 5 входів.

3.2.4 Розробка і дослідження суматора по модулю 2 на 5 входів.

3.2.5 Розробка і дослідження схеми порівняння двох 2-розрядних кодів на рівність.

3.2.6 Розробка і дослідження схеми порівняння двох 4-разрядних кодів на нерівність А>В.

3.2.7 Розробка і дослідження порогового пристрою чотирьох вхідних змінних з порогом ≤2 для індикації перебувань на двох, три або чотирьох входах одночасно.

3.2.8 Розробка і дослідження вузла захисту дешифратора для виявлення комбінацій, що містять більше однієї логічної одиниці.

3.3 Основні теоретичні відомості

Мультиплексор,

окрім свого основного призначення –

комутації в бажаному порядку інформаційних

сигналів з декількох вхідних шин на

одну вихідну, може бути використаний

як універсальний логічний елемент, що

реалізовує будь-яку логічну функцію,

що містить до

![]() змінних, де

змінних, де

![]() число адресних входів мультиплексора.

число адресних входів мультиплексора.

Процедуру синтезу при цьому найзручніше проводити по таблиці істинності для логічної функції, що підлягає реалізації. Нижче розглянута процедура синтезу на прикладі реалізації мажоритарного логічного елементу для трьох змінних (на три входи) на базі мультиплексора 4:1.

Таблиця

істинності мажоритарного логічного

елементу для трьох змінних

![]() представлена табл.3.1.

представлена табл.3.1.

Даний

мультиплексор має два адресні входи

![]() і

і

![]() ,

на яких можуть бути подані дві змінні

,

на яких можуть бути подані дві змінні

![]() та

та

![]() .

.

Їх необхідно записати зліва від відповідних логічних змінних.

Таблиця 3.1 Таблиця істинності мажоритарного логічного елемену для трьох змінних

Тоді

перші два стовбці для змінних

і

однакові і дорівнюють 0 і 0. Це відповідає

наявності коду

![]() на

адресних входах

і

,

тобто підключенню першого інформаційного

входу

на

адресних входах

і

,

тобто підключенню першого інформаційного

входу

![]() на вихід мультиплексора. Зверху таблиці

істинності можна записати для цих двох

стовбців значення інформаційного входу

. Аналогічно для наступних двох стовбців

код на адресних входах

і

рівний 10, що відповідає підключенню

входу

на вихід мультиплексора. Зверху таблиці

істинності можна записати для цих двох

стовбців значення інформаційного входу

. Аналогічно для наступних двох стовбців

код на адресних входах

і

рівний 10, що відповідає підключенню

входу

![]() і так далі. Значення сигналів, які повинні

бути подані на інформаційні входи

і так далі. Значення сигналів, які повинні

бути подані на інформаційні входи

![]() ,

визначають шляхом порівняння значень

третьої логічної змінної

,

визначають шляхом порівняння значень

третьої логічної змінної

![]() і логічної функції

і логічної функції

![]() ,

що реалізовується. Для перших двох

стовпців функція

має значення, рівне 0. Отже, на вхід

необхідно подати сигнал логічного "0".

Для наступних двох стовбців змінна

,

що реалізовується. Для перших двох

стовпців функція

має значення, рівне 0. Отже, на вхід

необхідно подати сигнал логічного "0".

Для наступних двох стовбців змінна

![]() приймає

послідовно значення 0 і 1. Функція

при цьому. Тоже приймає послідовно

значення 0 і 1, тобто повторює її. Тому

на вхід

подається сама змінна

.

Аналогічно отримують на вході

приймає

послідовно значення 0 і 1. Функція

при цьому. Тоже приймає послідовно

значення 0 і 1, тобто повторює її. Тому

на вхід

подається сама змінна

.

Аналогічно отримують на вході

![]() .сигнал

і на вході

.сигнал

і на вході

![]() сигнал логічної "1". Схема реалізації

мажоритарного логічного елемента на 3

входа на мультиплексорі 4:1 приведена

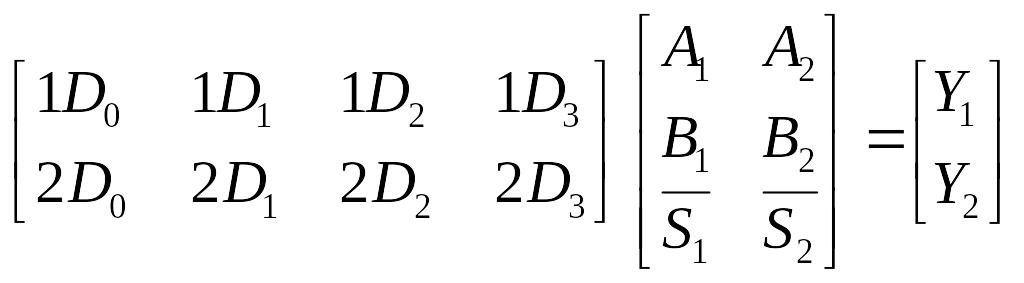

на рис.3.1,а.

сигнал логічної "1". Схема реалізації

мажоритарного логічного елемента на 3

входа на мультиплексорі 4:1 приведена

на рис.3.1,а.

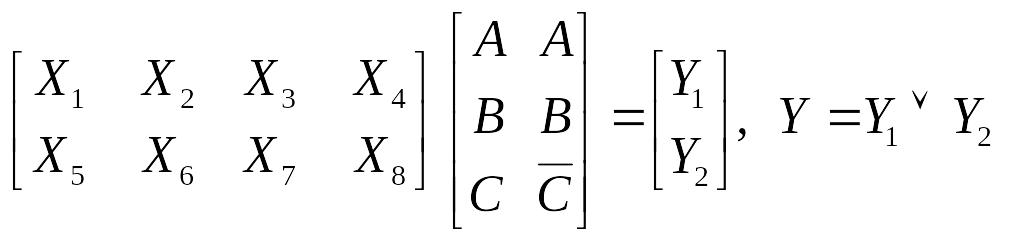

Реалізована логічна функція представлена в матричній формі, має вигляд

![]() ,

(3.1)

,

(3.1)

![]()

Таблиця 3.2 Таблиця істинності суматора по модулю 2 читирьох змінних

Мультиплексор

4:1 має два адресних входи отже, на кожному

з них окремо може бути реалізована

тільки логічна функція 3 змінних. Для

реалізацій логічної функції 4 змінних

необхідно додатково використовувати

стробуючий вхід мультиплексора. Для

керування стробуючими входами

мультиплексорів в табл.3.2 виділена

змінна

![]() це найбільш зручно та наочно. Із таблиці

видно, що змінна

для перших 8 столбців приймає значення,

рівне "0", а для наступних стовбців

– "1". У віповідності із цим табл.3.2

можна, розділити на дві частини по

границі "0" – "1" для змінної.

Першу частину табл. 3.2 необхідно

реалізувати на одному мультиплексорі,

а другу частину – на іншому. Перш за все

потрібно реалізувати першу частину

(перші 8 стовбців).

це найбільш зручно та наочно. Із таблиці

видно, що змінна

для перших 8 столбців приймає значення,

рівне "0", а для наступних стовбців

– "1". У віповідності із цим табл.3.2

можна, розділити на дві частини по

границі "0" – "1" для змінної.

Першу частину табл. 3.2 необхідно

реалізувати на одному мультиплексорі,

а другу частину – на іншому. Перш за все

потрібно реалізувати першу частину

(перші 8 стовбців).

Р ис.

3.1 Структурні схеми мажоритарного

логічного елементу і суматора модуля

2 на 4 входи

ис.

3.1 Структурні схеми мажоритарного

логічного елементу і суматора модуля

2 на 4 входи

Змінною

приписують зліва значення стробуючого

входу

![]() першого мультиплексора, яким вона керує.

Залишається логічна функція 3 змінних

–

першого мультиплексора, яким вона керує.

Залишається логічна функція 3 змінних

–

![]() i яка реалізується аналогічно прикладу,

розглянутому вище. Змінним

і

приписують зліва значення

i яка реалізується аналогічно прикладу,

розглянутому вище. Змінним

і

приписують зліва значення

![]() і

і

![]() адресних входів першого мультиплексора.

Тоді першим двом стовбцям таблиці

відповідає код

на адресних входах

,

тобто підключення першого входу першого

мультиплексора

адресних входів першого мультиплексора.

Тоді першим двом стовбцям таблиці

відповідає код

на адресних входах

,

тобто підключення першого входу першого

мультиплексора

![]() .

Значення сигналу, який необхідно подати

на вхід

.

Значення сигналу, який необхідно подати

на вхід

![]() ,

визначають за значеннями змінної

,

визначають за значеннями змінної

![]() і функції

для цих стовбців. Для перших двох стовпців

приймає послідовно значення "0" і

"1". Функція приймає послідовно ті

ж значення "0" і "1", тобто

повторює змінну

.

Відповідно, на вході

необходно підвести саму змінну

.

Аналогично можна вияснити, що на вхід

необхідно подати інвертоване значення

і функції

для цих стовбців. Для перших двох стовпців

приймає послідовно значення "0" і

"1". Функція приймає послідовно ті

ж значення "0" і "1", тобто

повторює змінну

.

Відповідно, на вході

необходно підвести саму змінну

.

Аналогично можна вияснити, що на вхід

необхідно подати інвертоване значення

![]() ,

на вхід

,

на вхід

![]() ,

на

,

на

![]() .

Таким чином, перша частина табл. 3.2

реалізується на першому мультиплексорі

4:1.

.

Таким чином, перша частина табл. 3.2

реалізується на першому мультиплексорі

4:1.

Друга

частина табл. 3.2 реалізується на другому

мультиплексорі аналогічно. Відмінність

полягатиме в тому, що на стробуючий вхід

![]() другого мультиплексора підводиться не

сама змінна

,

а її інвертоване значення

другого мультиплексора підводиться не

сама змінна

,

а її інвертоване значення

![]() ,

оскільки для другої частини табл. 3.2

змінна

має значення, рівне "1", а для роботи

мультиплексора необхідна наявність

"0" на його стробуючому вході. Із

другої частини табл. 3.2 (наступні її 8

стовбців) по аналогії може набути

значення сигналів на інформаційних

входах другого мультиплексора. На перший

вхід другого мультиплексора

,

оскільки для другої частини табл. 3.2

змінна

має значення, рівне "1", а для роботи

мультиплексора необхідна наявність

"0" на його стробуючому вході. Із

другої частини табл. 3.2 (наступні її 8

стовбців) по аналогії може набути

значення сигналів на інформаційних

входах другого мультиплексора. На перший

вхід другого мультиплексора

![]() ,

на другий _

,

на другий _![]() ,

на третій

,

на третій

![]() і на четвертий

і на четвертий

![]() Схема реалізації суматора по модулю 2

на 4 входи приведена на рис.3.2, б.

Схема реалізації суматора по модулю 2

на 4 входи приведена на рис.3.2, б.

Реалізована логічна функція , представлена в . матричному вигляді, може бути записана як

![]() (3.2)

(3.2)

3.4 Порядок виконання робіт циклу

3.4.1 Ознайомитися з короткими відомостями з теорії.

3.4.2 Отримати у викладача технічне завдання.

3.4.3 По таблицях істинності скласти матриці вхідних змінних, адресації і вихідних змінних.

3.4.4 Скласти структурну схеми реалізації заданого пристрою.

3.4.5 Використовуючи засоби автоматизованого проекту-вання MAX+II: створити графічний проект, скомпілювати та провести функціональне моделювання логічної функції.

3.4.6 Порівняти результати експерименту з результатами синтезу.

3.5 Контрольні питання

3.5.1 Логічні функції, що реалізовуються на мультиплек-сорах.

3.5.2 Функції перемикачів і форми їх представлення.

3.5.3 Процедури, синтезу пристроїв на базі мультиплексорів.

3.5.4 Схеми порівняння кодів на рівність і нерівність.

3.5.5 Схеми контролю кодів на парність і непарність.

3.5.6 Порогові пристрої.

3.5.7 Суматори по модулю два.

3.5.8 Мажоритарний логічний елемент.

3.5.9 Вузол захисту дешифратора.

Лабораторна робота №4